# CPE 323: DMA Controller

Aleksandar Milenkovic

Electrical and Computer Engineering The University of Alabama in Huntsville

milenka@ece.uah.edu

http://www.ece.uah.edu/~milenka

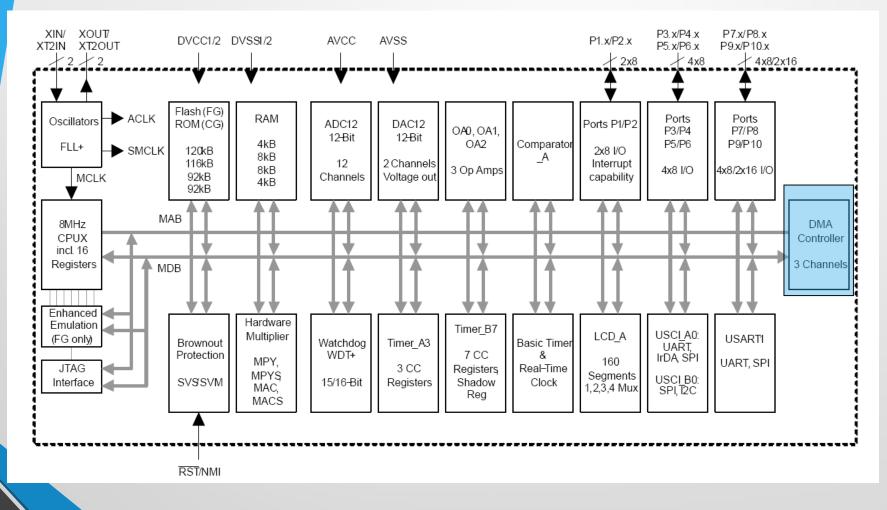

### System View: MSP430FG461x

THE UNIVERSITY OF

# I/O Interfacing: A Review

- Three principal software approaches to interfacing peripheral I/O devices

- Polling

- Interrupts

- DMA Transfers

- Polling

- Check the status bit (e.g., is USCI.RX.IFG bit set new character is received); If it is set, read the data from RXBUF; If it is not set, read the status bit again;

- CPU does polling continually (long waits, no useful work done)

- Interrupts

- When the status bit is set, ISR is requested

- CPU does the transfer when needed

- DMA

- Transfer takes place when everything is ready with no CPU intervention

THE UNIVERSITY OF ALABAMA IN HUNTSVILLE

# **DMA Controller Introduction**

- Direct memory access (DMA) controller transfers data from one address to another without CPU intervention, across the entire address range

- Examples

- Move data from the ADC12 conversion memory to RAM, move data from RAM to DAC12, move a message to USCI, receive a message from USCI

- Devices that contain a DMA controller may have one, two, or three DMA channels available

- Benefits of using the DMA controller

- Can increase the throughput of peripheral modules

- Can reduce system power consumption by allowing the CPU to remain in a low-power mode without having to awaken to move data to or from a peripheral

THE UNIVERSITY OF

# **MSP430 DMA Controller Features**

- Up to three independent transfer channels

- Configurable DMA channel priorities

- Requires only two MCLK clock cycles per transfer

- Byte or word and mixed byte/word transfer capability

- Block sizes up to 65535 bytes or words

- Configurable transfer trigger selections

- Selectable edge or level-triggered transfer

- Four addressing modes

- Single, block, or burst-block transfer modes

- Configured from software

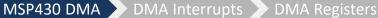

## **DMA Block Diagram**

Demos

DMA Registers

CPE

MSP430 DMA DMA Interrupts

Introduction

# **DMA Operation**

- 3 Channels (DMA0, DMA1, DMA2) for independent transfers

- Initialize block of data transfer from software, carry it out in hardware

- DMA Registers

- Starting Address (SA)

- Destination Address (DA)

- Block Size (SZ)

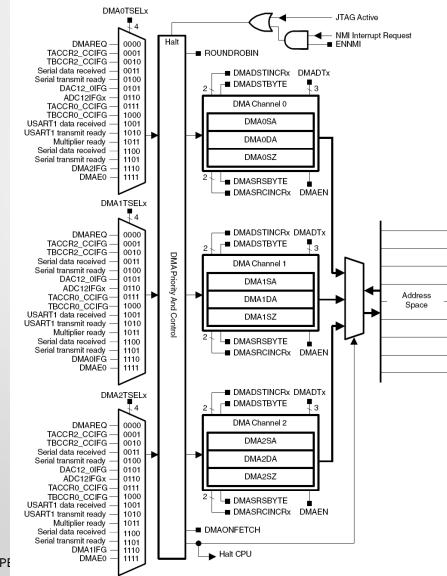

# **DMA Addressing Modes**

- Configured with the DMASRCINCRx and DMADSTINCRx control bits

- Select if the source/destination address is incremented, decremented, or unchanged after each transfer

- Four transfer modes

- Fixed address to fixed address (e.g., comm2comm)

- Fixed address to block of addresses (e.g. comm2mem)

- Block of addresses to fixed address (e.g., mem2comm)

- Block of addresses to block of addresses (mem2mem)

Fixed Address To Block Of Addresses

- Byte-to-byte, word-to-word, byte-toword, or word-to-byte

- Word-to-byte: only the lower byte of the source-word is transferred

- Byte-to-word: the upper byte of the destination-word is cleared when the transfer occurs

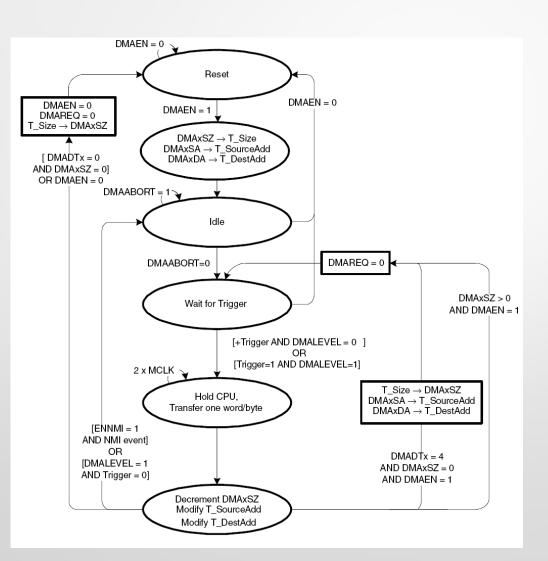

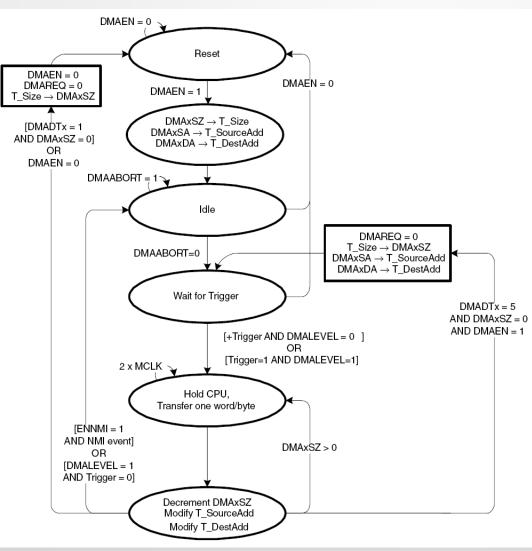

## **DMA Transfer Modes**

- Single/Repeated single modes: each byte/word transfer requires a separate trigger

- Block/Repeated block modes: a transfer of a complete block of data occurs after one trigger

- CPU is halted until the complete block has been transferred

- Burst-block/Repeated burst-block modes: transfers are block transfers with CPU activity interleaved.

- CPU executes 2 MCLK cycles after every four byte/word transfers of the block resulting in 20% CPU execution capacity

| DMADTx   | Transfer<br>Mode                    | Description                                                                                                                     |

|----------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 000      | Single transfer                     | Each transfer requires a trigger. DMAEN is automatically cleared when DMAxSZ transfers have been made.                          |

| 001      | Block transfer                      | A complete block is transferred with one trigger.<br>DMAEN is automatically cleared at the end of the block transfer.           |

| 010, 011 | Burst-block<br>transfer             | CPU activity is interleaved with a block transfer.<br>DMAEN is automatically cleared at the end of the<br>burst-block transfer. |

| 100      | Repeated single transfer            | Each transfer requires a trigger. DMAEN remains enabled.                                                                        |

| 101      | Repeated<br>block transfer          | A complete block is transferred with one trigger.<br>DMAEN remains enabled.                                                     |

| 110, 111 | Repeated<br>burst-block<br>transfer | CPU activity is interleaved with a block transfer.<br>DMAEN remains enabled.                                                    |

### **DMA Single Transfer**

MSP430 DMA DMA Interrupts

THE UNIVERSITY OF ALABAMA IN HUNTSVILLE

**DMA Block Transfer**

Demos

# **DMA Trigger Operation**

- DMAxTSELx bits select trigger

- Edge-sensitive or level-sensitive

| <ul> <li>0000 A transfer is triggered when the DMAREQ bit is set. The DMAREQ bit is automatically reset when the transfer starts</li> <li>0001 A transfer is triggered when the TACCR2 CCIFG flag is set. The TACCR2 CCIFG flag is automatically reset when the transfer starts. If the TACCR2 CCIE bit is set, the TACCR2 CCIFG flag will not trigger a transfer.</li> <li>0010 A transfer is triggered when the TBCCR2 CCIFG flag is set. The TBCCR2 CCIFG flag is automatically reset when the transfer starts. If the TBCCR2 CCIE bit is set, the TBCCR2 CCIFG flag is automatically reset when the transfer starts. If the TBCCR2 CCIE bit is set, the TBCCR2 CCIFG flag will not trigger a transfer.</li> <li>0011 Devices with USART0: A transfer is triggered when the URXIFG0 flag is set. URXIFG0 is automatically reset when the transfer starts. If URXIE0 is set, the URXIFG0 flag will not trigger a transfer.</li> <li>0010 Devices with USCI_A0: A transfer is triggered when the UCA0RXIFG flag is set. UCA0RXIFG flag will not trigger a transfer.</li> <li>0100 Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UCA0RXIE is set, the UCA0RXIFG flag will not trigger a transfer.</li> <li>0100 Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> <li>0100 Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> </ul> | DMAxTSELx | Operation                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>automatically reset when the transfer starts. If the TACCR2 CCIE bit is set, the TACCR2 CCIFG flag will not trigger a transfer.</li> <li>0010 A transfer is triggered when the TBCCR2 CCIFG flag is set. The TBCCR2 CCIFG flag is automatically reset when the transfer starts. If the TBCCR2 CCIE bit is set, the TBCCR2 CCIFG flag will not trigger a transfer.</li> <li>0011 Devices with USART0: A transfer is triggered when the URXIFG0 flag is set. URXIFG0 is automatically reset when the transfer starts. If URXIE0 is set, the URXIFG0 flag will not trigger a transfer.</li> <li>0011 Devices with USCI_A0: A transfer is triggered when the UCA0RXIFG flag is set. UCA0RXIFG is automatically reset when the transfer starts. If UCA0RXIE is set, the UCA0RXIFG flag will not trigger a transfer.</li> <li>0100 Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UCA0RXIE is set, the UCA0RXIFG flag will not trigger a transfer.</li> <li>0100 Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000      |                                                                                                                                                                                                                                                                                                             |

| <ul> <li>automatically reset when the transfer starts. If the TBCCR2 CCIE bit is set, the TBCCR2 CCIFG flag will not trigger a transfer.</li> <li>Devices with USART0: A transfer is triggered when the URXIFG0 flag is set. URXIFG0 is automatically reset when the transfer starts. If URXIE0 is set, the URXIFG0 flag will not trigger a transfer.</li> <li>Devices with USCI_A0: A transfer is triggered when the UCA0RXIFG flag is set. UCA0RXIFG flag will not trigger a transfer.</li> <li>Devices with USART0: A transfer is triggered when the UCA0RXIFG flag is set. UCA0RXIFG flag will not trigger a transfer.</li> <li>Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> <li>Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0001      | automatically reset when the transfer starts. If the TACCR2 CCIE bit is set, the TACCR2                                                                                                                                                                                                                     |

| <ul> <li>automatically reset when the transfer starts. If URXIE0 is set, the URXIFG0 flag will not trigger a transfer.</li> <li>Devices with USCI_A0: A transfer is triggered when the UCA0RXIFG flag is set. UCA0RXIFG is automatically reset when the transfer starts. If UCA0RXIE is set, the UCA0RXIFG flag will not trigger a transfer.</li> <li>0100 Devices with USART0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> <li>Devices with USCI_A0: A transfer is triggered when the UTXIFG0 flag is set. UTXIFG0 is automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0010      | automatically reset when the transfer starts. If the TBCCR2 CCIE bit is set, the TBCCR2                                                                                                                                                                                                                     |

| automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger a transfer.<br>Devices with USCI_A0: A transfer is triggered when the UCA0TXIFG flag is set. UCA0TXIFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0011      | automatically reset when the transfer starts. If URXIE0 is set, the URXIFG0 flag will not trigger<br>a transfer.<br>Devices with USCI_A0: A transfer is triggered when the UCA0RXIFG flag is set. UCA0RXIFG<br>is automatically reset when the transfer starts. If UCA0RXIE is set, the UCA0RXIFG flag will |

| not trigger a transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0100      | automatically reset when the transfer starts. If UTXIE0 is set, the UTXIFG0 flag will not trigger<br>a transfer.<br>Devices with USCI_A0: A transfer is triggered when the UCA0TXIFG flag is set. UCA0TXIFG<br>is automatically reset when the transfer starts. If UCA0TXIE is set, the UCA0TXIFG flag will |

THE UNIVERSITY OF ALABAMA IN HUNTSVILLE

# DMA Trigger Operation (cont'd)

Demos

0101 Devices with DAC12: A transfer is triggered when the DAC12\_0CTL DAC12IFG flag is set. The DAC12\_0CTL DAC12IFG flag is automatically cleared when the transfer starts. If the DAC12 0CTL DAC12IE bit is set, the DAC12 0CTL DAC12IFG flag will not trigger a transfer. 0110 Devices with ADC12: A transfer is triggered by an ADC12IFGx flag. When single-channel conversions are performed, the corresponding ADC12IFGx is the trigger. When sequences are used, the ADC12IFGx for the last conversion in the sequence is the trigger. A transfer is triggered when the conversion is completed and the ADC12IFGx is set. Setting the ADC12IFGx with software will not trigger a transfer. All ADC12IFGx flags are automatically reset when the associated ADC12MEMx register is accessed by the DMA controller. Devices with SD16 or SD16 A: A transfer is triggered by the SD16IFG flag of the master channel in grouped mode or of channel 0. Setting the SD16IFG with software will not trigger a transfer. All SD16IFG flags are automatically reset when the associated SD16MEMx register is accessed by the DMA controller. If the SD16IE of the master channel is set, the SD16IFG will not trigger a transfer. 0111 A transfer is triggered when the TACCR0 CCIFG flag is set. The TACCR0 CCIFG flag is automatically reset when the transfer starts. If the TACCR0 CCIE bit is set, the TACCR0 CCIFG flag will not trigger a transfer. 1000 A transfer is triggered when the TBCCR0 CCIFG flag is set. The TBCCR0 CCIFG flag is automatically reset when the transfer starts. If the TBCCR0 CCIE bit is set, the TBCCR0 CCIFG flag will not trigger a transfer. 1001 Devices with USART1: A transfer is triggered when the URXIFG1 flag is set. URXIFG1 is automatically reset when the transfer starts. If URXIE1 is set, the URXIFG1 flag will not trigger a transfer. Devices with USCI A1: A transfer is triggered when the UCA1RXIFG flag is set. UCA1RXIFG is automatically reset when the transfer starts. If UCA1RXIE is set, the UCA1RXIFG flag will not trigger a transfer.

# DMA Trigger Operation (cont'd)

| DMAxTSELx | Operation                                                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1010      | Devices with USART1: A transfer is triggered when the UTXIFG1 flag is set. UTXIFG1 is automatically reset when the transfer starts. If UTXIE1 is set, the UTXIFG1 flag will not trigger a transfer.<br>Devices with USCI_A1: A transfer is triggered when the UCA1TXIFG flag is set. UCA1TXIFG |

|           | is automatically reset when the transfer starts. If UCA1TXIE is set, the UCA1TXIFG flag will not trigger a transfer.                                                                                                                                                                           |

| 1011      | A transfer is triggered when the hardware multiplier is ready for a new operand.                                                                                                                                                                                                               |

| 1100      | A transfer is triggered when the UCB0RXIFG flag is set. UCB0RXIFG is automatically reset when the transfer starts. If UCB0RXIE is set, the UCB0RXIFG flag will not trigger a transfer.                                                                                                         |

| 1101      | A transfer is triggered when the UCB0TXIFG flag is set. UCB0TXIFG is automatically reset when the transfer starts. If UCB0TXIE is set, the UCB0TXIFG flag will not trigger a transfer.                                                                                                         |

| 1110      | A transfer is triggered when the DMAxIFG flag is set. DMA0IFG triggers channel 1, DMA1IFG triggers channel 2, and DMA2IFG triggers channel 0. None of the DMAxIFG flags are automatically reset when the transfer starts.                                                                      |

| 1111      | A transfer is triggered by the external trigger DMAE0.                                                                                                                                                                                                                                         |

**Stopping DMA Transfers**

Demos

**DMA Registers**

- Two ways to stop DMA transfers in progress:

- A single, block, or burst-block transfer may be stopped with an NMI interrupt, if the ENNMI bit is set in register DMACTL1

- A burst-block transfer may be stopped by clearing the DMAEN bit

THE UNIVERSITY OF

# **DMA Channel Priorities**

Demos

- Default DMA channel priorities are DMA0–DMA1–DMA2

- If two or three triggers happen simultaneously or are pending, the channel with the highest priority completes its transfer (single, block or burst-block transfer) first, then the second priority channel, then the third priority channel.

- Transfers in progress are not halted if a higher priority channel is triggered

- The higher priority channel waits until the transfer in progress completes before starting

- DMA channel priorities are configurable with the ROUNDROBIN bit

| DMA Priority       | Transfer Occurs | New DMA Priority   |

|--------------------|-----------------|--------------------|

| DMA0 – DMA1 – DMA2 | DMA1            | DMA2 – DMA0 – DMA1 |

| DMA2 – DMA0 – DMA1 | DMA2            | DMA0 – DMA1 – DMA2 |

| DMA0 – DMA1 – DMA2 | DMA0            | DMA1 – DMA2 – DMA0 |

DMA Registers > Demos

## **DMA Transfer Cycle Times**

- DMA requires 1 or 2 MCLK cc to synchronize before each single transfer or complete block or burst-block transfer

- Each byte/word transfer requires 2 MCLK after synchronization, and one cycle of wait time after the transfer

- DMA cycle time is dependent on the MSP430 operating mode and clock system setup (use MCLK)

- If the MCLK source is active, but the CPU is off, the DMA controller will use the MCLK source for each transfer, without re-enabling the CPU

- If the MCLK source is off, the DMA controller will temporarily restart MCLK, sourced with DCOCLK, for the single transfer or complete block or burst-block transfer

- The CPU remains off, and after the transfer completes, MCLK is turned off

| CPU Operating Mode    | Clock Source  | Maximum DMA Cycle Time                 |

|-----------------------|---------------|----------------------------------------|

| Active mode           | MCLK=DCOCLK   | 4 MCLK cycles                          |

| Active mode           | MCLK=LFXT1CLK | 4 MCLK cycles                          |

| Low-power mode LPM0/1 | MCLK=DCOCLK   | 5 MCLK cycles                          |

| Low-power mode LPM3/4 | MCLK=DCOCLK   | 5 MCLK cycles + 6 $\mu$ s <sup>†</sup> |

| Low-power mode LPM0/1 | MCLK=LFXT1CLK | 5 MCLK cycles                          |

| Low-power mode LPM3   | MCLK=LFXT1CLK | 5 MCLK cycles                          |

| Low-power mode LPM4   | MCLK=LFXT1CLK | 5 MCLK cycles + 6 $\mu$ s <sup>†</sup> |

<sup>†</sup> The additional 6  $\mu$ s are needed to start the DCOCLK. It is the t<sub>(LPMx)</sub> parameter in the data sheet. CFE 323 INFORMATION CONTINUES Systems

# **DMA and Interrupts**

- DMA transfers are not interruptible by system interrupts

- System interrupts remain pending until the completion of the transfer

- NMI interrupts can interrupt the DMA controller if the ENNMI bit is set

- System interrupt service routines are interrupted by DMA transfers

- If an interrupt service routine or other routine must execute with no interruptions, the DMA controller should be disabled prior to executing the routine

# **DMA Interrupts**

Demos

**DMA Registers**

- Each DMA channel has its own DMAIFG flag

- Each DMAIFG flag is set in any mode, when the corresponding DMAxSZ register counts to zero. If the corresponding DMAIE and GIE bits are set, an interrupt request is generated

- All DMAIFG flags source only one DMA controller interrupt vector and the interrupt vector may be shared with the other modules

- software must check the DMAIFG and other flags to determine the source of the interrupt

- The DMAIFG flags are not reset automatically and must be reset by software

# **DMAIV** Register

MSP430 DMA DMA Interrupts

# DMA and ADC12

Demos

**DMA** Registers

- DMA can automatically move data from any ADC12MEMx register to another location

- No CPU intervention, independently from LPMs

- => increases throughput of the ADC12 module, and saves energy

- DMA transfers can be triggered from any ADC12IFGx flag

- When CONSEQx = {0,2} the ADC12IFGx flag for the ADC12MEMx used for the conversion can trigger a DMA transfer

- When CONSEQx = {1,3}, the ADC12IFGx flag for the last ADC12MEMx in the sequence can trigger a DMA transfer

- Any ADC12IFGx flag is automatically cleared when the DMA controller accesses the corresponding ADC12MEMx

DMA Registers Demos

## **DMA Registers**

#### Register Short Form Address Initial State **Register Type** DMACTL0 DMA control 0 Read/write 0122h Reset with POR DMA control 1 DMACTL1 Read/write 0124h Reset with POR DMA interrupt vector DMAIV Read only 0126h Reset with POR DMA channel 0 control DMA0CTL Read/write 01D0h Reset with POR 01D2h Unchanged DMA channel 0 source address **DMA0SA** Read/write **DMA0DA** Read/write 01D6h Unchanged DMA channel 0 destination address DMA channel 0 transfer size **DMA0SZ** Read/write 01DAh Unchanged DMA channel 1 control DMA1CTL Read/write 01DCh Reset with POR DMA channel 1 source address DMA1SA 01DEh Read/write Unchanged DMA1DA 01E2h Unchanged DMA channel 1 destination address Read/write DMA channel 1 transfer size DMA1SZ Read/write 01E6h Unchanged DMA channel 2 control DMA2CTL 01E8h Reset with POR Read/write DMA channel 2 source address DMA2SA Read/write 01EAh Unchanged DMA channel 2 destination address DMA2DA Read/write 01EEh Unchanged DMA-channel 2 transfer size DMA2SZ Read/write 01F2h Unchanged

### Table 10–5. DMA Registers, MSP430FG461x, MSP430F471xx devices

# **DMACTLO**

### DMACTL0, DMA Control Register 0

| I | 15           | 14            | 13                                                                                                                                                                                                                                         | 12                                                                                                                                                                                                                                                                                                                                           | 11        | 10     | 9      | 8                                           |

|---|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|--------|---------------------------------------------|

|   | Reserved     |               |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                              | DMA2TSELx |        |        |                                             |

|   | rw–(0)       | rw–(0)        | rw–(0)                                                                                                                                                                                                                                     | rw–(0)                                                                                                                                                                                                                                                                                                                                       | rw–(0)    | rw–(0) | rw–(0) | rw–(0)                                      |

|   | 7            | 6             | 5                                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                            | 3         | 2      | 1      | 0                                           |

|   |              | DN            | MA1TSELx                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                              |           | DMAG   | DTSELx |                                             |

|   | rw–(0)       | rw–(0)        | rw–(0)                                                                                                                                                                                                                                     | rw–(0)                                                                                                                                                                                                                                                                                                                                       | rw–(0)    | rw–(0) | rw–(0) | rw–(0)                                      |

| F | Reserved     | Bits<br>15–12 | Reserved                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                              |           |        |        |                                             |

| _ | MA2<br>SELx  | Bits<br>11–8  | The trigge<br>MSP430FG<br>device-spec<br>0000 DMA<br>0001 TACC<br>0010 TBCC<br>0011 URX<br>0100 UTXI<br>0101 DAC<br>0111 TACC<br>1000 TBCC<br>1001 URX<br>1010 UTXI<br>1010 UTXI<br>1010 UTXI<br>1010 No a<br>1101 No a<br>1101 DMA<br>DMA | 461x devices it is given below; for other devices, see the<br>ific data sheet.<br>REQ bit (software trigger)<br>R2 CCIFG bit<br>R2 CCIFG bit<br>FG0 (MSP430FG43x), UCA0RXIFG (MPS430FG461x)<br>FG0 (MSP430FG43x), UCA0TXIFG (MSP430FG461x)<br>2_0CTL DAC12IFG bit<br>2 ADC12IFGx bit<br>F80 CCIFG bit<br>F80 CCIFG bit<br>FG1 bit<br>FG1 bit |           |        |        | FG43x and<br>ces, see the<br>461x)<br>461x) |

|   | OMA1<br>SELx | Bits<br>7–4   | Same as D                                                                                                                                                                                                                                  | MA2TSELx                                                                                                                                                                                                                                                                                                                                     |           |        |        |                                             |

|   | OMA0<br>SELx | Bits<br>3–0   | Same as D                                                                                                                                                                                                                                  | MA2TSELx                                                                                                                                                                                                                                                                                                                                     |           |        |        |                                             |

## **DMACTL1**

### DMACTL1, DMA Control Register 1

| 15              | 14   | 13                                                                                                                                                                                                                                                                                                                                                          | 12 | 11         | 10             | 9              | 8          |

|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|----------------|----------------|------------|

| 0               | 0    | 0                                                                                                                                                                                                                                                                                                                                                           | 0  | 0          | 0 0            |                | 0          |

| r0              | rO   | r0                                                                                                                                                                                                                                                                                                                                                          | r0 | r0         | rO             | r0             | r0         |

|                 |      |                                                                                                                                                                                                                                                                                                                                                             |    | I          |                |                |            |

| 7               | 6    | 5                                                                                                                                                                                                                                                                                                                                                           | 4  | 3          | 2              | 1              | 0          |

| 0               | о    | 0                                                                                                                                                                                                                                                                                                                                                           | 0  | 0          | DMA<br>ONFETCH | ROUND<br>ROBIN | ENNMI      |

| r0              | r0   | r0                                                                                                                                                                                                                                                                                                                                                          | r0 | rO         | rw–(0)         | rw–(0)         | rw–(0)     |

| Reserved<br>DMA | 15–3 | Reserved. Read only. Always read as 0.                                                                                                                                                                                                                                                                                                                      |    |            |                |                |            |

| ONFETCH         | (    |                                                                                                                                                                                                                                                                                                                                                             |    | curs immed |                | fetch after th | ne trigger |

| round<br>Robin  | (    | <ul> <li>Round robin. This bit enables the round-robin DMA channel priorities.</li> <li>0 DMA channel priority is DMA0 – DMA1 – DMA2</li> <li>1 DMA channel priority changes with each transfer</li> </ul>                                                                                                                                                  |    |            |                |                |            |

| ENNMI           | i    | <ul> <li>Enable NMI. This bit enables the interruption of a DMA transfer by an NMI interrupt. When an NMI interrupts a DMA transfer, the current transfer is completed normally, further transfers are stopped, and DMAABORT is set.</li> <li>0 NMI interrupt does not interrupt DMA transfer</li> <li>1 NMI interrupt interrupts a DMA transfer</li> </ul> |    |            |                |                |            |

# DMAxCTL

#### DMAxCTL, DMA Channel x Control Register

|                |                                                                                                                         |                                                                                                                                                                                      | 15                                   | 14                                                                                                                                                                                                                                                                           | 13                                                                                                                                                                                                                            | 12                                                    | 11                                                                                                                                                       | 10                                                      | 9                                                             | 8                                                            |

|----------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|

|                |                                                                                                                         |                                                                                                                                                                                      | Reserved                             |                                                                                                                                                                                                                                                                              | DMADTx                                                                                                                                                                                                                        |                                                       | DMADS                                                                                                                                                    | TINCRx                                                  | DMASI                                                         | RCINCRx                                                      |

|                |                                                                                                                         |                                                                                                                                                                                      | rw–(0)                               | rw–(0)                                                                                                                                                                                                                                                                       | rw–(0)                                                                                                                                                                                                                        | rw–(0)                                                | rw–(0)                                                                                                                                                   | rw–(0)                                                  | rw–(0)                                                        | rw–(0)                                                       |

|                |                                                                                                                         |                                                                                                                                                                                      | 7                                    | 6                                                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                             | 4                                                     | 3                                                                                                                                                        | 2                                                       | 1                                                             | 0                                                            |

|                |                                                                                                                         |                                                                                                                                                                                      | DMA<br>DSTBYTE                       | DMA<br>SRCBYTE                                                                                                                                                                                                                                                               | DMALEVEL                                                                                                                                                                                                                      | DMAEN                                                 | DMAIFG                                                                                                                                                   | DMAIE                                                   | DMA<br>ABORT                                                  | DMAREQ                                                       |

| DMA<br>SRCBYTE | Bit 6                                                                                                                   | DMA source byte. This bit selects the source as a byte or word.<br>0 Word<br>1 Byte                                                                                                  | rw–(0)<br>Reserved                   | rw-(0)<br>Bit 15                                                                                                                                                                                                                                                             | rw–(0)<br>Reserved                                                                                                                                                                                                            | rw–(0)                                                | rw–(0)                                                                                                                                                   | rw–(0)                                                  | rw–(0)                                                        | rw–(0)                                                       |

| DMA<br>LEVEL   | Bit 5                                                                                                                   | <ul> <li>DMA level. This bit selects between edge-sensitive and level-sensitive triggers.</li> <li>0 Edge sensitive (rising edge)</li> <li>1 Level sensitive (high level)</li> </ul> | DMADTx                               | DMADTx Bits DMA Tran<br>14–12 000 Sing<br>001 Bloc<br>010 Burs                                                                                                                                                                                                               |                                                                                                                                                                                                                               |                                                       | eserved<br>MA Transfer mode.<br>20 Single transfer<br>21 Block transfer<br>20 Burst-block transfer<br>21 Burst-block transfer<br>21 Burst-block transfer |                                                         |                                                               |                                                              |

| DMAEN          | Bit 4                                                                                                                   | DMA enable<br>0 Disabled<br>1 Enabled                                                                                                                                                | Disabled 101 Rep<br>Disabled 110 Rep |                                                                                                                                                                                                                                                                              | 101 Repeated block transfer<br>110 Repeated burst-block transfer                                                                                                                                                              |                                                       |                                                                                                                                                          |                                                         |                                                               |                                                              |

| DMAIFG         | Bit 3                                                                                                                   | DMA interrupt flag<br>0 No interrupt pending<br>1 Interrupt pending                                                                                                                  | DSTINCRx 11-10                       | DMA destination increment. This bit selects automatic incrementing or<br>decrementing of the destination address after each byte or word transfer.<br>When DMADSTBYTE=1, the destination address increments/decrements by<br>one. When DMADSTBYTE=0, the destination address |                                                                                                                                                                                                                               |                                                       |                                                                                                                                                          |                                                         |                                                               |                                                              |

| DMAIE          | Bit 2                                                                                                                   | DMA interrupt enable<br>0 Disabled<br>1 Enabled                                                                                                                                      |                                      |                                                                                                                                                                                                                                                                              | increments/decrements by two. The DMAXDA is copied into a temporary<br>register and the temporary register is incremented or decremented. DMAxDA<br>is not incremented or decremented.<br>00 Destination address is unchanged |                                                       |                                                                                                                                                          |                                                         |                                                               | a temporary                                                  |

| DMA<br>ABORT   | Bit 1                                                                                                                   | DMA Abort. This bit indicates if a DMA transfer was interrupt by an NMI.0DMA transfer not interrupted1DMA transfer was interrupted by NMI                                            |                                      |                                                                                                                                                                                                                                                                              | 01 Destinat<br>10 Destinat                                                                                                                                                                                                    | ion address<br>ion address                            | is unchange<br>is decremer<br>is incremen                                                                                                                | ed<br>nted                                              |                                                               |                                                              |

| DMAREQ         | EQ Bit 0 DMA request. Software-controlled DMA start. DMAREQ is reset<br>automatically.<br>0 No DMA start<br>1 Start DMA |                                                                                                                                                                                      | DMA<br>SRCINCRx                      | 9–8                                                                                                                                                                                                                                                                          | DMA source<br>decrementing<br>DMASRCBYT<br>When DMASI<br>two. The DMA<br>register is inc<br>decremented.<br>00 Source a                                                                                                       | of the sour<br>E=1, the s<br>RCBYTE=0,<br>AxSA is cop | ce address f<br>ource addre<br>the source<br>ied into a te<br>r decrement                                                                                | or each byt<br>ess increme<br>address in<br>emporary re | e or word tra<br>ents/decreme<br>crements/de<br>gister and tl | ansfer. When<br>ents by one.<br>ecrements by<br>ne temporary |

|                |                                                                                                                         |                                                                                                                                                                                      |                                      |                                                                                                                                                                                                                                                                              | 01 Source a<br>10 Source a                                                                                                                                                                                                    | address is u                                          | nchanged<br>ecremented                                                                                                                                   |                                                         |                                                               |                                                              |

|                |                                                                                                                         |                                                                                                                                                                                      | DMA<br>DSTBYTE                       |                                                                                                                                                                                                                                                                              | DMA destinati<br>0 Word<br>1 Byte                                                                                                                                                                                             | on byte. Thi                                          | s bit selects                                                                                                                                            | the destinat                                            | tion as a byt                                                 | e or word.                                                   |

|                |                                                                                                                         | CPE 323 Introduction to Embedded Computer Systems                                                                                                                                    |                                      |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                               |                                                       |                                                                                                                                                          | 25                                                      | La                                                            | CAS                                                          |

### DMAxSA

#### DMAxSA, DMA Source Address Register 28 31 30 29 27 26 25 824 Reserved r0 r0 r0 r0 r0 r0 r0 r0 21 23 22 20 19 18 17 16 Reserved DMAxSAx r0 r0 r0 r0 rw rw rw rw 12 15 14 13 11 10 9 8 DMAxSAx rw rw rw rw rw rw rw rw 2 7 6 5 4 3 0 DMAxSAx rw rw rw rw rw rw rw rw Reserved Bits Reserved 31-20 DMA source address. The source address register points to the DMA source Bits DMAxSAx 19–0 address for single transfers or the first source address for block transfers. The source address register remains unchanged during block and burst-block transfers. Devices that have addressable memory range 64-KB or below contain a single word for the DMAxSA. MSP430FG461x and MSP430F471xx devices implement two words for the DMAxSA register as shown. Bits 31-20 are reserved and always read as zero. Reading or writing bits 19-16 requires the use of extended instructions. When writing to DMAxSA with word instructions, bits 19-16 are cleared.

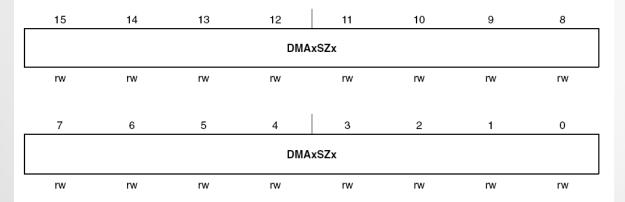

### DMAxSZ

Demos

### DMAxSZ, DMA Size Address Register

DMAxSZxBits<br/>15-0DMA size. The DMA size register defines the number of byte/word data per<br/>block transfer. DMAxSZ register decrements with each word or byte transfer.<br/>When DMAxSZ decrements to 0, it is immediately and automatically reloaded<br/>with its previously initialized value.

- 00000h Transfer is disabled

- 00001h One byte or word to be transferred

- 00002h Two bytes or words have to be transferred

- 0FFFFh 65535 bytes or words have to be transferred

### **DMAIV**

### DMAIV, DMA Interrupt Vector Register

| 15 | 14 | 13 | 12 | 11    | 10     | 9     | 8  |

|----|----|----|----|-------|--------|-------|----|

| 0  | 0  | 0  | 0  | 0     | 0      | 0     | 0  |

| r0 | r0 | r0 | r0 | r0    | r0     | r0    | r0 |

|    |    |    |    |       |        |       |    |

| 7  | 6  | 5  | 4  | 3     | 2      | 1     | 0  |

| 0  | 0  | 0  | 0  |       | DMAIVx |       | 0  |

| r0 | r0 | rO | rO | r–(0) | r–(0)  | r–(0) | r0 |

DMAIVx

DMA Interrupt Vector value Bits 15-0

| DMAIV Contents | Interrupt Source     | Interrupt Flag | Interrupt<br>Priority |

|----------------|----------------------|----------------|-----------------------|

| 00h            | No interrupt pending | -              |                       |

| 02h            | DMA channel 0        | DMA0IFG        | Highest               |

| 04h            | DMA channel 1        | DMA1IFG        |                       |

| 06h            | DMA channel 2        | DMA2IFG        |                       |

| 08h            | Reserved             | -              |                       |

| 0Ah            | Reserved             | -              |                       |

| 0Ch            | Reserved             | _              |                       |

| 0Eh            | Reserved             | -              | Lowest                |

### **Mem2Mem DMA Transfer**

| //* | *****               | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <pre>#include "msp430xG46x.h"</pre>                                             |  |  |  |  |

|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| //  | MSP430xG461x Demo   | - DMA0, Repeated Burst to-from RAM, Software Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                 |  |  |  |  |

| //  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                 |  |  |  |  |

| //  | Description: A 16 w | word block from 1400-141fh is transferred to 1420h-143fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | void main(void)                                                                 |  |  |  |  |

| //  | using DMA0 in a bu  | rst block using software DMAREQ trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | {                                                                               |  |  |  |  |

| //  | After each transfer | c, source, destination and DMA size are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | WDTCTL = WDTPW + WDTHOLD; // Stop WDT                                           |  |  |  |  |

| //  | reset to initial so | oftware setting because DMA transfer mode 5 is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P5DIR $ = 0 \times 002$ ; // P1.0 output                                        |  |  |  |  |

| //  | P5.1 is toggled du  | ring DMA transfer only for demonstration purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |  |  |  |  |

| //  | ** RAM location 0x1 | 400 - 0x143f used - make sure no compiler conflict **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DMA0SA = 0x1400; // Start block address                                         |  |  |  |  |

| 11  | ACLK = 32kHz, MCLH  | K = SMCLK = default DCO 1048576Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DMA0DA = 0x1420; // Destination block address                                   |  |  |  |  |

| //  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DMA0SZ = 0x0010; // Block size                                                  |  |  |  |  |

| //  | MSP43               | 30xG461x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <pre>DMA0CTL = DMADT_5 + DMASRCINCR_3 + DMADSTINCR_3 + DMAEN; // Rpt, inc</pre> |  |  |  |  |

| //  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                 |  |  |  |  |

| //  | 71\1                | XIN   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DMAOCTL  = DMAEN; // Enable DMAO                                                |  |  |  |  |

| //  | 1.1                 | 32kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 |  |  |  |  |