# CPE 323: MSP430 Digital I/O

Aleksandar Milenkovic

Electrical and Computer Engineering The University of Alabama in Huntsville

milenka@ece.uah.edu

http://www.ece.uah.edu/~milenka

### Outline

- System View

- Digital I/O

- Address Mapping

- Port Operations

- Schematics

- Configuration

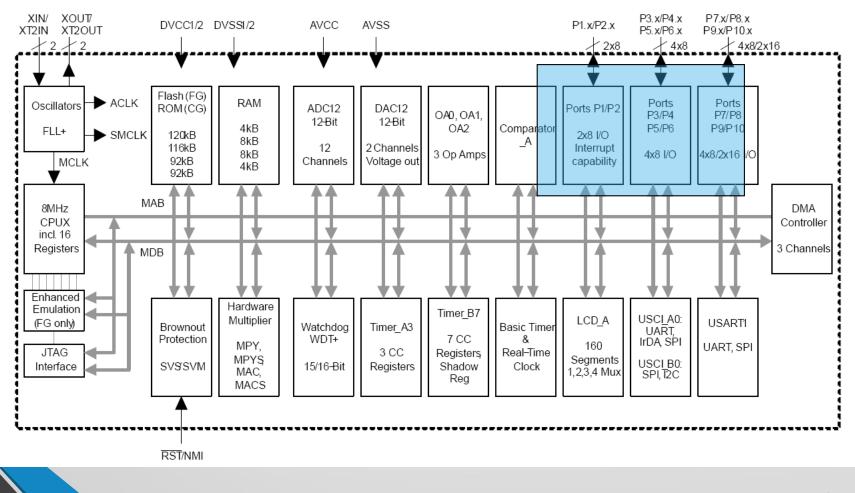

# Functional Block Diagram of MSP430xG461x

Configuration

Operation

CPE 323 Intro to Embedded Computer Systems

System View

Digital IO

Address Mapping

Operation

Digital IO > Address Mapping

System View

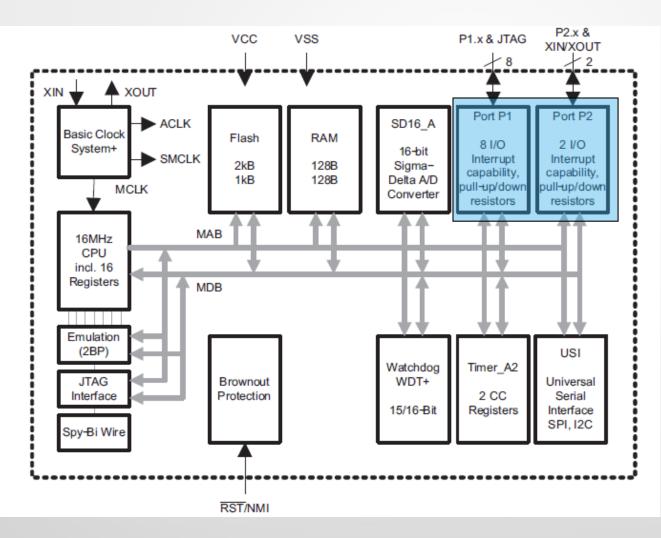

# Functional Block Diagram of MSP430xF20x3

Configuration

THE UNIV

OF

## **Digital Input, Output**

Schematics

Configuration

Digital inputs – they are either on or off

Operation

Inputs from humans or sensors

Digital IO Address Mapping

- E.g., switches, sensors (e.g., door is locked, button is pressed, ...)

- Digital outputs set them on or off

- Light-emitting diodes (LEDs), seven segment displays, liquid-crystal displays (LCDs)

- MSP430 can supply these directly if they work from the same voltage and draw a sufficiently small current

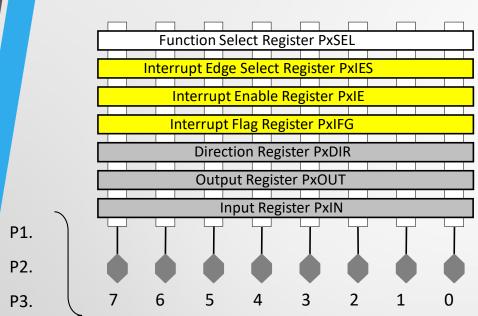

- Digital input/output ports (P1 Pn), n=2 ... 10

- Almost all pins can be used either for digital I/O or for other (special) functions

- Their operation must be configured on start up

System View

Digital IO

# Digital Input, Output (cont'd)

Schematics

Configuration

- Ports P1 and P2 have interrupt capability

- Each interrupt for the P1 and P2 input lines can be individually enabled and configured to provide an interrupt on a rising edge or falling edge of an input signal

Operation

• The digital I/O features include:

Address Mapping

- Independently programmable individual I/Os

- Any combination of input or output

- Individually configurable P1 and P2 interrupts

- Independent input and output data registers

- The digital I/O is configured with user software

#### **Parallel Ports**

| Port1 | Port3      |  |  |  |

|-------|------------|--|--|--|

| Port2 | <br>Port10 |  |  |  |

| yes   | yes        |  |  |  |

| yes   | no         |  |  |  |

| yes   | no         |  |  |  |

| yes   | no         |  |  |  |

| yes   | yes        |  |  |  |

| yes   | yes        |  |  |  |

| yes   | yes        |  |  |  |

P4.

...

P10.

System Viev

Operation > S

Configuration

### IAR View of Digital I/O Ports

P1, P2

| egister       |   |               |   |  |   |

|---------------|---|---------------|---|--|---|

| Port 1/2      |   |               | • |  |   |

| PIIN          | - | 0x03          |   |  |   |

| PIOUT         |   |               |   |  |   |

| PIDIR         | = | 0x00          |   |  |   |

| P1IFG         | = | 0x00          |   |  |   |

| PIIES         | = | 0x2D          |   |  |   |

| PIIE          | = | $0 \times 00$ |   |  |   |

| PISEL         |   |               |   |  |   |

| P2IN          |   | 0x20          |   |  |   |

| P2OUT         |   | $0 \times 00$ |   |  | _ |

| P2DIR         |   |               |   |  |   |

| P2IFG         |   |               |   |  |   |

| P2IES<br>P2IE |   | 0x71          |   |  |   |

|               |   | 00x00<br>00x0 |   |  |   |

|               | - | 0x00          |   |  |   |

#### P1, P2, Expanded view

| Register       |   |               |   |               |   |      |

|----------------|---|---------------|---|---------------|---|------|

| Port 1/2       |   |               | • |               |   |      |

| <b>P1IN</b>    | = | 0x03          |   | <b>P2DIR</b>  |   |      |

| <b>∃</b> P1OUT | = | 0x23          |   | - P7          | = | 0    |

| <b>P1DIR</b>   | = | 0x00          |   | <b>⊞P2IFG</b> | = | 0x00 |

| <b>P11FG</b>   | = | $0 \times 00$ |   | <b>⊞P2IES</b> | = | 0x71 |

| <b>P1IES</b>   | = | 0x2D          |   | <b>⊞P2IE</b>  | = | 0x00 |

| <b>P1IE</b>    | = | 0x00          |   | <b>⊞P2SEL</b> | = | 0x00 |

| <b>P1SEL</b>   | = | $0 \times 00$ |   |               |   |      |

| <b>∃P2IN</b>   | = | 0x20          |   |               |   |      |

| FP2OUT         | = | $0 \times 00$ |   |               |   |      |

| - P0           | = | 0             |   |               |   |      |

| - P1           | = | 0             |   |               |   |      |

| - P2           | = | 0             |   |               |   |      |

| - P3           | = | 0             |   |               |   |      |

| - P4           | = | 0             |   |               |   |      |

| - P5           | = | 0             |   |               |   |      |

| - P6           | = | 0             |   |               |   |      |

| L P7           | = | 0             |   |               |   |      |

| P2DIR          | = | $0 \times 00$ |   |               |   |      |

| - P0           | = | 0             |   |               |   |      |

| - P1           | = | 0             |   |               |   |      |

| - P2           | = | 0             |   |               |   |      |

| - P3           | = | 0             |   |               |   |      |

| - P4           | = | 0             |   |               |   |      |

| - P5           | = | 0             |   |               |   |      |

| - P6           | = | 0             |   |               |   |      |

#### P3, P4, Expanded view

| Register<br>Port 3/4 |   |      |   |  |  |  |

|----------------------|---|------|---|--|--|--|

|                      |   | 0.00 | • |  |  |  |

| <b>BP3IN</b>         |   | 0x26 |   |  |  |  |

| EP3OUT<br>EP3DIR     |   |      |   |  |  |  |

| ⊞P3DIR<br>⊞P3SEL     |   |      |   |  |  |  |

| ⊞P3SEL<br>⊞P4IN      |   |      |   |  |  |  |

| EP41N                |   |      |   |  |  |  |

| ⊞P400T<br>⊞P4DIR     |   |      |   |  |  |  |

| BP4DIR               |   |      |   |  |  |  |

| HP45LL               | - | 0x00 |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

| 1                    |   |      |   |  |  |  |

|                      |   |      |   |  |  |  |

: > Configuration

#### MSP430FG4618 Port Address Mapping

- Notice addresses of P9.IN and P10.IN, P9.OUT and P10.OUT

- Other pairs of register too

- What are implications?

$\rightarrow$

| Port P10 | Port P10 selection              | P10SEL        | 00Fh         |

|----------|---------------------------------|---------------|--------------|

| FOILFIU  |                                 |               |              |

|          | Port P10 direction              | P10DIR        | 00Dh         |

|          | Port P10 output                 | P10OUT        | 00Bh         |

|          | Port P10 input                  | P10IN         | 009h         |

| Port P9  | Port P9 selection               | P9SEL         | 00Eh         |

|          | Port P9 direction               | P9DIR         | 00Ch         |

|          | Port P9 output                  | P9OUT         | 00Ah         |

|          | Port P9 input                   | P9IN          | 008h         |

| Port P8  | Port P8 selection               | P8SEL         | 03Fh         |

|          | Port P8 direction               | P8DIR         | 03Dh         |

|          | Port P8 output                  | P8OUT         | 03Bh         |

|          | Port P8 input                   | P8IN          | 039h         |

| Port P7  | Port P7 selection               | P7SEL         | 03Eh         |

|          | Port P7 direction               | P7DIR         | 03Ch         |

|          | Port P7 output                  | P7OUT         | 03Ah         |

|          | Port P7 input                   | P7IN          | 038h         |

| Port P6  | Port P6 selection               | P6SEL         | 037h         |

|          | Port P6 direction               | P6DIR         | 036h         |

|          | Port P6 output                  | P6OUT         | 035h         |

|          | Port P6 input                   | P6IN          | 034h         |

| Port P5  | Port P5 selection               | P5SEL         | 033h         |

|          | Port P5 direction               | P5DIR         | 032h         |

|          | Port P5 output                  | P5OUT         | 031h         |

|          | Port P5 input                   | P5IN          | 030h         |

| Port P4  | Port P4 selection               | P4SEL         | 01Fh         |

|          | Port P4 direction               | P4DIR         | 01Eh         |

|          | Port P4 output                  | P4OUT         | 01Dh         |

|          | Port P4 input                   | P4IN          | 01Ch         |

| Port P3  | Port P3 selection               | P3SEL         | 01Bh         |

| i oiti 5 | Port P3 direction               | P3DIR         | 01Ah         |

|          | Port P3 output                  | PSOUT         | 019h         |

|          | Port P3 input                   | P3IN          | 018h         |

| Port P2  | Port P2 selection               | P3IN          | 018h         |

| FOITFZ   | Port P2 interrupt enable        | P2IE          | 02En         |

|          | Port P2 Interrupt-edge select   | P2IE<br>P2IES | 02Dh         |

|          |                                 |               | 02Ch<br>02Bh |

|          | Port P2 interrupt flag          | P2IFG         |              |

|          | Port P2 direction               | P2DIR         | 02Ah         |

|          | Port P2 output                  | P2OUT         | 029h         |

|          | Port P2 input                   | P2IN          | 028h         |

| Port P1  | Port P1 selection               | P1SEL         | 026h         |

|          | Port P1 interrupt enable        | P1IE          | 025h         |

|          | Port P1 interrupt-edge select   | P1IES         | 024h         |

|          | Port P1 interrupt flag          | P1IFG         | 023h         |

|          | Port P1 direction               | P1DIR         | 022h         |

|          | Port P1 output                  | P1OUT         | 021h         |

|          | Port P1 output<br>Port P1 input | P1OUT<br>P1IN | 021          |

9

Configuration

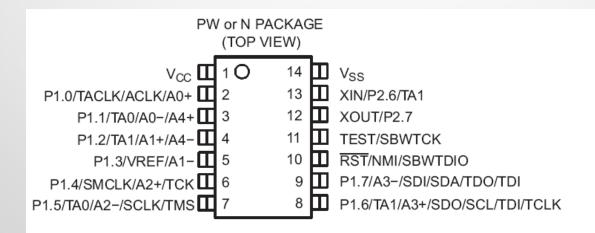

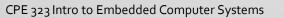

### MSP430F2013 Port Address Mapping

- There is one 8-bit I/O port implemented—port P1 and two bits of I/O port P2

- Each I/O has an individually programmable pullup/pulldown resistor

|         | 1 4                           | 1     |      |

|---------|-------------------------------|-------|------|

| Port P2 | Port P2 resistor enable       | P2REN | 02Fh |

|         | Port P2 selection             | P2SEL | 02Eh |

|         | Port P2 interrupt enable      | P2IE  | 02Dh |

|         | Port P2 interrupt edge select | P2IES | 02Ch |

|         | Port P2 interrupt flag        | P2IFG | 02Bh |

|         | Port P2 direction             | P2DIR | 02Ah |

|         | Port P2 output                | P2OUT | 029h |

|         | Port P2 input                 | P2IN  | 028h |

| Port P1 | Port P1 resistor enable       | P1REN | 027h |

|         | Port P1 selection             | P1SEL | 026h |

|         | Port P1 interrupt enable      | P1IE  | 025h |

|         | Port P1 interrupt edge select | P1IES | 024h |

|         | Port P1 interrupt flag        | P1IFG | 023h |

|         | Port P1 direction             | P1DIR | 022h |

|         | Port P1 output                | P1OUT | 021h |

|         | Port P1 input                 | P1IN  | 020h |

Address Mapping

Schematics >> Configuration

# **Digital I/O Registers: Operation**

Operation

#### Input Register PnIN

Digital IO

- Each bit in each PnIN register reflects the value of the input signal at the corresponding I/O pin when the pin is configured as I/O function.

- Bit = 0: The input is low

- Bit = 1: The input is high

Do not write to PxIN. It will result in increased current consumption

#### Output Registers PnOUT

- Each bit in each PnOUT register is the value to be output on the corresponding I/O pin when the pin is configured as I/O function and output direction.

- Bit = 0: The output is low

- Bit = 1: The output is high

LaCASA

THE UNIVERSITY OF

# **Digital I/O Registers: Operation**

<u>Schematics</u>

Configuration

Direction Registers PnDIR

Address Mapping

**Digital IO**

• Bit = 0: The port pin is switched to input direction

Operation

• Bit = 1: The port pin is switched to output direction

- Function Select Registers PnSEL

- Port pins are often multiplexed with other peripheral module functions.

- Bit = 0: I/O Function is selected for the pin

- Bit = 1: Peripheral module function is selected for the pin

Schematics >> Configuration

# **Digital I/O Registers: Operation**

Operation

- Interrupt Flag Registers P1IFG, P2IFG (only for P1 and P2)

- Bit = 0: No interrupt is pending

Address Mapping

Digital IO

- Bit = 1: An interrupt is pending

- Only transitions, not static levels, cause interrupts

- Interrupt Edge Select Registers P1IES, P2IES

- Each PnIES bit selects the interrupt edge for the corresponding I/O pin (n=1, 2).

- Bit = 0: The PnIFGx flag is set with a low-to-high transition

- Bit = 1: The PnIFGx flag is set with a high-to-low transition

### Digital I/O Registers: Operation (Specific for MSP430F2xxx)

Configuration

Pullup/Pulldown Resistor Enable Registers PxREN

Operation

Address Mapping

**Digital IO**

- Each bit in each PxREN register enables or disables the pullup/pulldown resistor of the corresponding I/O pin

- The corresponding bit in the PxOUT register selects if the pin is pulled up or pulled down

- Bit = 0: Pullup/pulldown resistor disabled

- Bit = 1: Pullup/pulldown resistor enabled

### Digital I/O Registers: Operation (Specific Formain HUNTSVILLE MSP430F2xxx)

#### Two select registers PxSEL and PxSEL2

| PxSEL2 | PxSEL | Pin Function                                      |

|--------|-------|---------------------------------------------------|

| 0      | 0     | I/O function is selected.                         |

| 0      | 1     | Primary peripheral module function is selected.   |

| 1      | 0     | Reserved. See device-specific data sheet.         |

| 1      | 1     | Secondary peripheral module function is selected. |

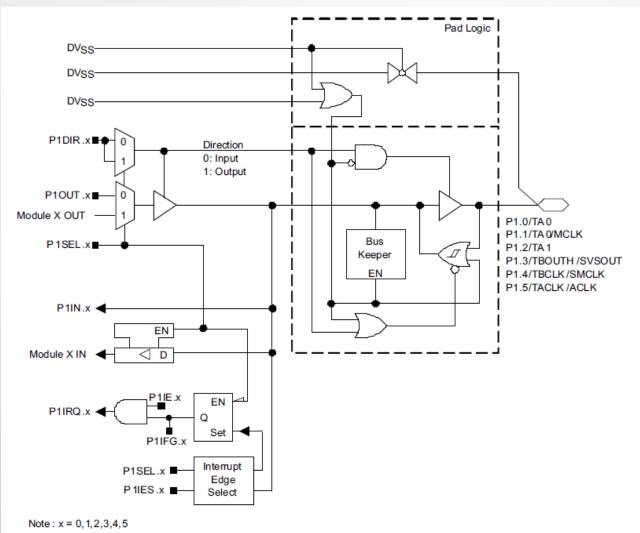

### MSP430FG4618 P1.0-5 Schematic

Operation

**Schematics**

Digital IO

Address Mapping

I.aCAS

16

Digital IO Address Mapping

lapping > Operation 🔰

Schematics Configuration

### MSP430F20x3 Port P1 Schematic

17 LaCASA

# **Configuring Unused Pins**

Schematics

Configuration

Unused pins must never be left unconnected in their default state as inputs

Operation

- Floating (unconnected) input both pull-up and pull-down may be causing shoot-through current => deplete your power source

- What should you do?

Address Mapping

Digital IO

- Wire unused pins externally to V<sub>GND</sub> or V<sub>DD</sub> and configure them as inputs (Warning: if you accidentally configure them as outputs you may damage the chip)

- Leave the pins unconnected externally, but connect them internally to V<sub>GND</sub> or V<sub>DD</sub> (applicable only to MSP430F2xx devices)

- Leave the pins unconnected and configure them as outputs (Warning: do not short circuit them with the probe)