## **MSP430 Instruction Set**

**Double Operand Instructions**

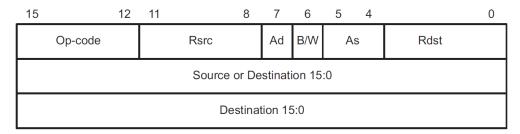

Figure 6-22. MSP430 Double-Operand Instruction Format

Table 6-4. MSP430 Double-Operand Instructions

| Mnemonic | S-Reg,<br>D-Reg | Operation                                   | Status Bits <sup>(1)</sup> |   |   |   |  |

|----------|-----------------|---------------------------------------------|----------------------------|---|---|---|--|

|          |                 |                                             | V                          | N | Z | С |  |

| MOV(.B)  | src,dst         | src 	o dst                                  | _                          | _ | - | - |  |

| ADD(.B)  | src,dst         | $src + dst \rightarrow dst$                 | *                          | * | * | * |  |

| ADDC(.B) | src,dst         | $src + dst + C \rightarrow dst$             | *                          | * | * | * |  |

| SUB(.B)  | src,dst         | $dst + .not.src + 1 \rightarrow dst$        | *                          | * | * | * |  |

| SUBC(.B) | src,dst         | $dst + .not.src + C \rightarrow dst$        | *                          | * | * | * |  |

| CMP(.B)  | src,dst         | dst - src                                   | *                          | * | * | * |  |

| DADD(.B) | src,dst         | $src + dst + C \rightarrow dst (decimally)$ | *                          | * | * | * |  |

| BIT(.B)  | src,dst         | src .and. dst                               | 0                          | * | * | Z |  |

| BIC(.B)  | src,dst         | .not.src .and. $dst \rightarrow dst$        | -                          | - |   | - |  |

| BIS(.B)  | src,dst         | $\text{src .or. dst} \to \text{dst}$        | ::                         | _ |   | _ |  |

| XOR(.B)  | src,dst         | $src.xor.dst \rightarrow dst$               | *                          | * | * | Z |  |

| AND(.B)  | src,dst         | $src.and. dst \rightarrow dst$              | 0                          | * | * | Z |  |

<sup>\* =</sup> Status bit is affected.

- = Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

## **Single Operand Instructions**

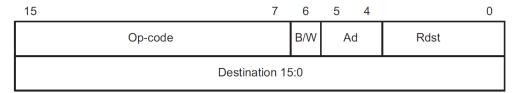

Figure 6-23. MSP430 Single-Operand Instructions

Table 6-5. MSP430 Single-Operand Instructions

| Mnemonic  | S-Reg, | Omenskien                                                                                      | Status Bits <sup>(1)</sup> |   |   |   |  |

|-----------|--------|------------------------------------------------------------------------------------------------|----------------------------|---|---|---|--|

| winemonic | D-Reg  | Operation                                                                                      | V                          | N | Z | С |  |

| RRC(.B)   | dst    | $C \to MSB \to \!\! \dots \!\! \dots \!\! LSB \to C$                                           | 0                          | * | * | * |  |

| RRA(.B)   | dst    | $MSB \to MSB \to LSB \to C$                                                                    | 0                          | * | * | * |  |

| PUSH(.B)  | src    | $SP - 2 \to SP,src \to SP$                                                                     | _                          | _ | - | _ |  |

| SWPB      | dst    | bit 15bit 8 ↔ bit 7bit 0                                                                       | _                          | _ | - | _ |  |

| CALL      | dst    | Call subroutine in lower 64KB                                                                  | _                          | _ | _ | _ |  |

| RETI      |        | $TOS \to SR, SP + 2 \to SP$                                                                    | *                          | * | * | * |  |

|           |        | $TOS \to PC, SP + 2 \to SP$                                                                    |                            |   |   |   |  |

| SXT       | dst    | Register mode: bit $7 \rightarrow$ bit 8bit 19<br>Other modes: bit $7 \rightarrow$ bit 8bit 15 | 0                          | * | * | Z |  |

<sup>(1) \* =</sup> Status bit is affected.

## **Jump Instructions**

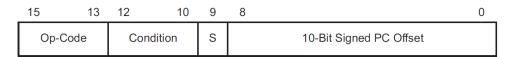

Figure 6-24. Format of Conditional Jump Instructions

Table 6-6. Conditional Jump Instructions

| Mnemonic | S-Reg,<br>D-Reg | Operation                            |

|----------|-----------------|--------------------------------------|

| JEQ, JZ  | Label           | Jump to label if zero bit is set     |

| JNE, JNZ | Label           | Jump to label if zero bit is reset   |

| JC       | Label           | Jump to label if carry bit is set    |

| JNC      | Label           | Jump to label if carry bit is reset  |

| JN       | Label           | Jump to label if negative bit is set |

| JGE      | Label           | Jump to label if (N .XOR. $V$ ) = 0  |

| JL       | Label           | Jump to label if (N .XOR. V) = 1     |

| JMP      | Label           | Jump to label unconditionally        |

<sup>- =</sup> Status bit is not affected.

<sup>0 =</sup> Status bit is cleared.

<sup>1 =</sup> Status bit is set.

## **Emulated Instructions**

Table 6-7. Emulated Instructions

| In admiration | Explanation                | Emulation -     | Status Bits <sup>(1)</sup> |   |   |   |  |

|---------------|----------------------------|-----------------|----------------------------|---|---|---|--|

| Instruction   |                            |                 | V                          | N | Z | С |  |

| ADC(.B) dst   | Add Carry to dst           | ADDC(.B) #0,dst | *                          | * | * | * |  |

| BR dst        | Branch indirectly dst      | MOV dst,PC      | _                          | - | - | _ |  |

| CLR(.B) dst   | Clear dst                  | MOV(.B) #0,dst  | _                          | - | - | _ |  |

| CLRC          | Clear Carry bit            | BIC #1,SR       | _                          | _ | _ | 0 |  |

| CLRN          | Clear Negative bit         | BIC #4,SR       | _                          | 0 | _ | _ |  |

| CLRZ          | Clear Zero bit             | BIC #2,SR       | _                          | _ | 0 | _ |  |

| DADC(.B) dst  | Add Carry to dst decimally | DADD(.B) #0,dst | *                          | * | * | * |  |

| DEC(.B) dst   | Decrement dst by 1         | SUB(.B) #1,dst  | *                          | * | * | * |  |

| DECD(.B) dst  | Decrement dst by 2         | SUB(.B) #2,dst  | *                          | * | * | * |  |

| DINT          | Disable interrupt          | BIC #8,SR       | _                          | _ | _ | _ |  |

| EINT          | Enable interrupt           | BIS #8,SR       | _                          | _ | _ | _ |  |

| INC(.B) dst   | Increment dst by 1         | ADD(.B) #1,dst  | *                          | * | * | * |  |

| INCD(.B) dst  | Increment dst by 2         | ADD(.B) #2,dst  | *                          | * | * | * |  |

Table 6-7. Emulated Instructions (continued)

| Instruction | Explanation                            | Emulation –      | Status Bits <sup>(1)</sup> |   |   |   |  |

|-------------|----------------------------------------|------------------|----------------------------|---|---|---|--|

| instruction |                                        |                  | V                          | N | Z | С |  |

| INV(.B) dst | Invert dst                             | XOR(.B) #-1,dst  | *                          | * | * | * |  |

| NOP         | No operation                           | MOV R3,R3        | -                          | - | - | - |  |

| POP dst     | Pop operand from stack                 | MOV @SP+,dst     | -                          | - | - | - |  |

| RET         | Return from subroutine                 | MOV @SP+,PC      | -                          | - | - | - |  |

| RLA(.B) dst | Shift left dst arithmetically          | ADD(.B) dst,dst  | *                          | * | * | * |  |

| RLC(.B) dst | Shift left dst logically through Carry | ADDC(.B) dst,dst | *                          | * | * | * |  |

| SBC(.B) dst | Subtract Carry from dst                | SUBC(.B) #0,dst  | *                          | * | * | * |  |

| SETC        | Set Carry bit                          | BIS #1,SR        | _                          | _ | _ | 1 |  |

| SETN        | Set Negative bit                       | BIS #4,SR        | _                          | 1 | _ | _ |  |

| SETZ        | Set Zero bit                           | BIS #2,SR        | _                          | _ | 1 | _ |  |

| TST(.B) dst | Test dst (compare with 0)              | CMP(.B) #0,dst   | 0                          | * | * | 1 |  |

<sup>\* =</sup> Status bit is affected.

- = Status bit is not affected.

0 = Status bit is cleared.

1 = Status bit is set.