# AN IMPLEMENTATION AND EXPERIMENTAL EVALUATION OF HARDWARE ACCELERATED CIPHERS IN ALL-PROGRAMMABLE SoCs ON EMBEDDED AND WORKSTATION COMPUTER PLATFORMS

by

#### RYAN A. COWART

# **A THESIS**

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

HUNTSVILLE, ALABAMA

2017

| In presenting this thesis in partia  | ll fulfillment of the requirements for a master's   |

|--------------------------------------|-----------------------------------------------------|

| degree from The University of Ala    | abama in Huntsville, I agree that the Library of    |

| this University shall make it freel  | ly available for inspection. I further agree that   |

| permission for extensive copying f   | for scholarly purposes may be granted by my         |

| advisor or, in his/her absence, by t | the Chair of the Department or the Dean of the      |

| School of Graduate Studies. It is a  | also understood that due recognition shall be given |

| to me and to The University of Ala   | abama in Huntsville in any scholarly use which      |

| may be made of any material in th    | his thesis.                                         |

|                                      |                                                     |

|                                      |                                                     |

|                                      | <u> </u>                                            |

| (student signature)                  | (date)                                              |

|                                      |                                                     |

# THESIS APPROVAL FORM

Submitted by Ryan A. Cowart in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this thesis. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering.

|                                            |         | Committee Chair  |

|--------------------------------------------|---------|------------------|

| (Dr. Aleksandar Milenkovic)                | (Date)  |                  |

| (Dr. David Coe)                            | (Date)  |                  |

| (Dr. Jeffrey Kulick)                       | (Date)  |                  |

| (D. P. : C. )                              | (D, 4.) | Department Chair |

| (Dr. Ravi Gorur)  (Dr. Shankar Mahalingam) | (Date)  | College Dean     |

| (Dr. David Berkowitz)                      | (Date)  | Graduate Dean    |

# ABSTRACT

# The School of Graduate Studies The University of Alabama in Huntsville

Degree <u>Master of Science in Engineering</u> College/Dept. <u>Engineering/Electrical & Computer Engineering</u>

Name of Candidate Ryan A. Cowart

Title An Implementation and Experimental Evaluation of Hardware Accelerated Ciphers in All-Programmable SoCs on Embedded and Workstation Computer Platforms

The protection of confidential information has become very important with the increase of data sharing and storage on public domains. Data confidentiality is accomplished through the use of ciphers that encrypt and decrypt the data to impede unauthorized access. Emerging heterogeneous platforms provide an ideal environment to use hardware acceleration to improve application performance. This thesis explores the performance benefits of hardware accelerated ciphers versus their software counterparts for multiple cipher modes. The hardware accelerated ciphers are implemented on the FPGA fabric of the Zyng-7000 All-Programmable System-on-a-Chip (SoC) and utilizes DMA for communicating with the host processor. The design is implemented within an embedded and workstation computing environment. File encryption and decryption of varying file sizes and a hardware sink test are used as the workloads for testing the software and hardware ciphers, with execution time, speedup, and throughput as the metrics for comparing the performance of each. The performance evaluations show that the hardware accelerated ciphers performed significantly better than the software ciphers in the embedded environment with speedups upwards of 30x, but only achieved moderate improvements for the workstation environment with speedups upwards of 1.5x.

| Abstract Approval: | Committee Chair  |  |

|--------------------|------------------|--|

|                    |                  |  |

|                    | Department Chair |  |

|                    |                  |  |

|                    | Graduate Dean    |  |

#### ACKNOWLEDGMENTS

I would first like to thank my Lord and Savior Jesus Christ from whom all wisdom and knowledge originates (Proverbs 1:7). He has blessed me with the intellectual ability to pursue my graduate studies and has continuously blessed me and my family on a daily basis.

I also want to express my gratitude to those who have made this research and thesis possible. Foremost, I would like to thank my advisor, Dr. Aleksandar Milenkovic, for the opportunity to study under his mentorship, his initial ideas for the research, and for his continuous guidance and support throughout the process. I would also like to thank Dr. Kulick for loaning me the ZC706 development board for use in my research. I would like to thank Dr. Milenkovic, Dr. Coe, and Dr. Kulick for their time reviewing and providing feedback on my Thesis.

Most importantly I would like to thank my family, my wife Brooke and daughter Hadlie, for their unconditional love, support, and patience throughout the process. I consider the accomplishment of this Thesis just as much theirs as it is mine.

# TABLE OF CONTENTS

| CHAPT | ΓER 1                                            | 1   |

|-------|--------------------------------------------------|-----|

| 1.1   | Need for Data Encryption                         | 2   |

| 1.2   | Technology Trends                                | 3   |

| 1.3   | What Has Been Achieved                           | 4   |

| 1.4   | Contributions                                    | 5   |

| 1.5   | Outline of the Thesis.                           | 5   |

| CHAPT | ΓER 2                                            | 7   |

| 2.1   | Advanced Encryption Standard (AES)               | 8   |

| 2.2   | Cipher Modes of Operation                        | .11 |

| 2.3   | Electronic Codebook (ECB)                        | .11 |

| 2.4   | Cipher Block Chaining (CBC)                      | .13 |

| 2.5   | Counter Mode (CTR)                               | .14 |

| 2.6   | OpenSSL                                          | .16 |

| 2.7   | All-Programmable SoCs (Zynq-7000)                | .17 |

| 2.8   | Xillybus                                         | .20 |

| 2.9   | Opportunity: Cryptographic Hardware Acceleration | .23 |

| CHAPT | ΓER 3                                            | .25 |

| CHAPT | ΓER 4                                            | .29 |

| СНАРТ | ΓER 5                                            | .31 |

| 5.1   | Embedded System Design                           | .33 |

| 5.1   | .1    | ARM Cores               | 34 |

|-------|-------|-------------------------|----|

| 5.1   | .2    | Xillybus Kernel Driver  | 35 |

| 5.1   | .3    | AXI4 Bus                | 37 |

| 5.1   | .4    | Xillybus IP Core        | 39 |

| 5.1   | .5    | Cipher Mode Cores       | 41 |

| 5.1   | .6    | AES IP Cores            | 48 |

| 5.2   | Wo    | rkstation System Design | 53 |

| 5.2   | .1    | Intel Processor         | 54 |

| 5.2   | .2    | Xillybus Kernel Driver  | 55 |

| 5.2   | .3    | PCIe Bus                | 56 |

| 5.2   | .4    | Xillybus IP Core        | 56 |

| 5.2   | .5    | Cipher Mode Cores       | 57 |

| 5.2   | .6    | AES IP Cores            | 58 |

| СНАРТ | TER 6 | 6                       | 59 |

| 6.1   | Ma    | ximum Throughput        | 59 |

| 6.2   | Оре   | enSSL Extension6        | 62 |

| СНАРТ | TER 7 | 7                       | 64 |

| 7.1   | Zed   | lboard6                 | 64 |

| 7.2   | Xill  | linux6                  | 65 |

| 7.3   | ZC    | 706                     | 66 |

| 7.4   | Wo    | rkstation6              | 68 |

| 7.  | 5 Me    | asurement Setup                                                     | .68 |

|-----|---------|---------------------------------------------------------------------|-----|

| 7.0 | 6 File  | e Encryption/Decryption Test                                        | .70 |

| 7.  | 7 Ha    | rdware Sink Test                                                    | .73 |

| CHA | APTER   | 8                                                                   | .75 |

| 8.  | 1 Em    | bedded Design Micro-benchmarking                                    | .75 |

|     | 8.1.1   | AXI4 Bus                                                            | .75 |

|     | 8.1.2   | Zedboard HDD (SD Card)                                              | .76 |

|     | 8.1.3   | Hardware Accelerated Ciphers                                        | .76 |

| 8.3 | 2 Wo    | rkstation Design Micro-benchmarking                                 | .77 |

|     | 8.2.1   | PCIe Bus                                                            | .77 |

|     | 8.2.2   | Workstation HDD                                                     | .77 |

|     | 8.2.3   | Hardware Accelerated Ciphers                                        | .78 |

| CHA | APTER   | 9                                                                   | .79 |

| 9.  | 1 Res   | sults for Zedboard Embedded Design                                  | .79 |

|     | 9.1.1   | Results for File Encryption/Decryption Test using Maximum           |     |

|     | Throug  | hput Application                                                    | .80 |

|     | 9.1.2   | Results for Hardware Sink Test using Maximum Throughput             |     |

|     | Applica | tion                                                                | .84 |

|     | 9.1.3   | Results for File Encryption/Decryption Test using OpenSSL Extension | n   |

|     | Applica | tion                                                                | .88 |

| 9.1.4   | Results for Hardware Sink Test using OpenSSL Extension Application  |

|---------|---------------------------------------------------------------------|

|         | 91                                                                  |

| 9.2 Re  | sults for ZC706 Workstation Design94                                |

| 9.2.1   | Results for File Encryption/Decryption Test using Maximum           |

| Throug  | hput Application95                                                  |

| 9.2.2   | Results for Hardware Sink Test using Maximum Throughput             |

| Applica | tion                                                                |

| 9.2.3   | Results for File Encryption/Decryption Test using OpenSSL Extension |

| Applica | ntion                                                               |

| 9.2.4   | Results for Hardware Sink Test using OpenSSL Extension Application  |

|         | 113                                                                 |

| CHAPTER | 10                                                                  |

# LIST OF FIGURES

| Figure     |                                                         | Page |

|------------|---------------------------------------------------------|------|

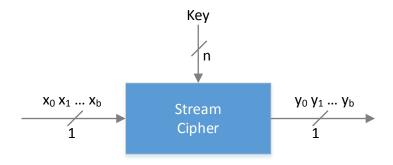

| Figure 2.1 | Stream Cipher [3]                                       | 9    |

| Figure 2.2 | Block Cipher [3]                                        | 9    |

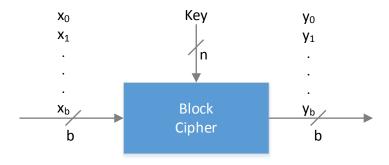

| Figure 2.3 | AES Block Cipher [3]                                    | 11   |

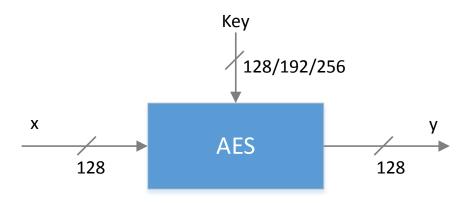

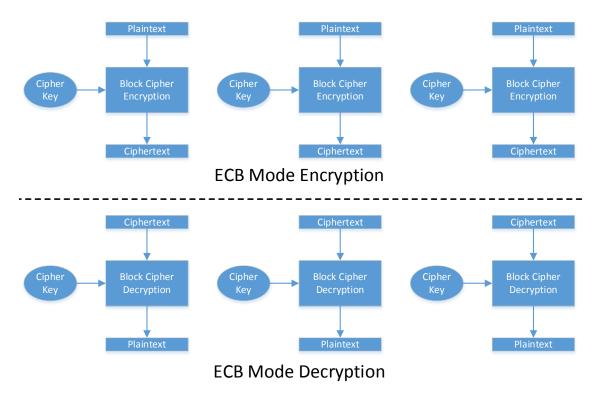

| Figure 2.4 | ECB Encryption/Decryption Block Diagrams                | 12   |

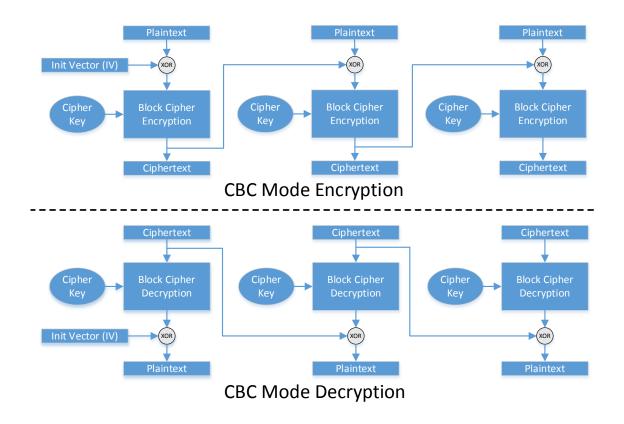

| Figure 2.5 | CBC Encryption/Decryption Block Diagrams                | 14   |

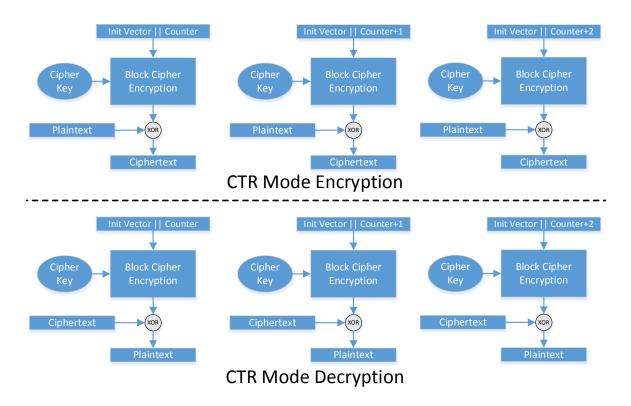

| Figure 2.6 | CTR Encryption/Decryption Block Diagrams                | 16   |

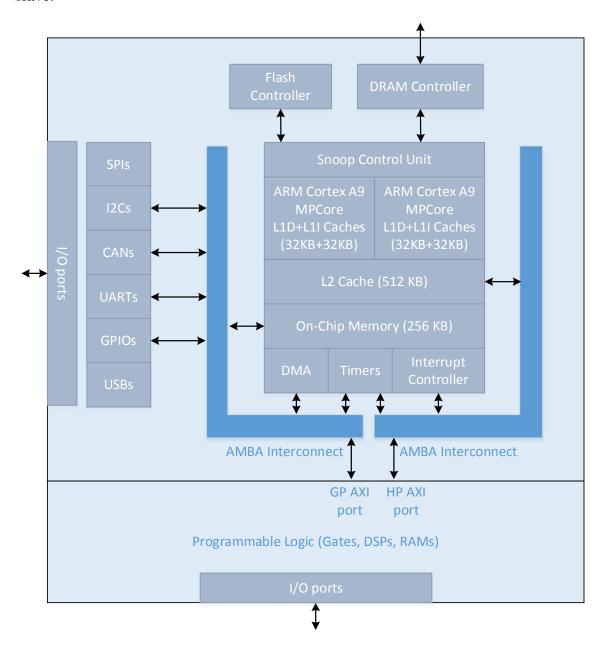

| Figure 2.7 | Zynq-7000 APSoC System Architecture                     | 19   |

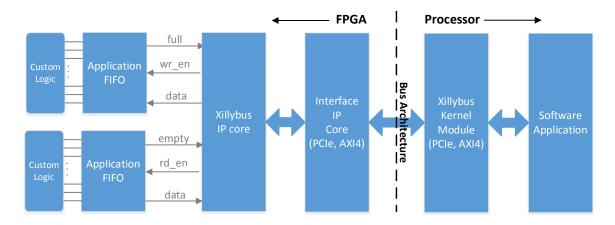

| Figure 2.8 | Xillybus Functional Block Diagram                       | 22   |

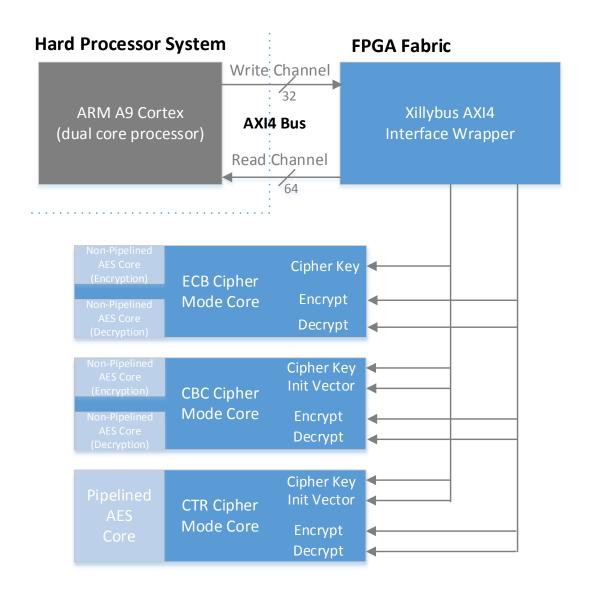

| Figure 5.1 | Top Level System View of Zedboard Embedded Design       | 34   |

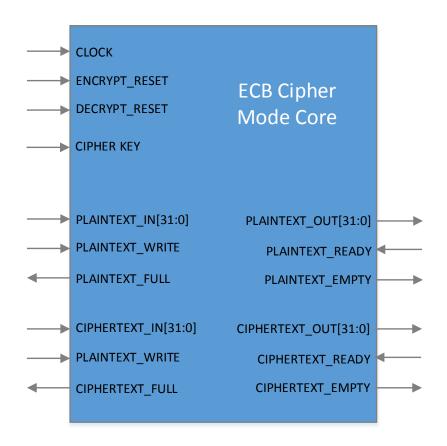

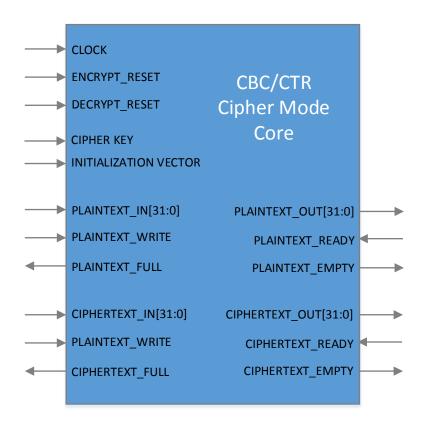

| Figure 5.2 | I/O Signals for ECB Cipher Mode IP Core                 | 43   |

| Figure 5.3 | I/O Signals for CBC and CTR Cipher Mode IP Cores        | 44   |

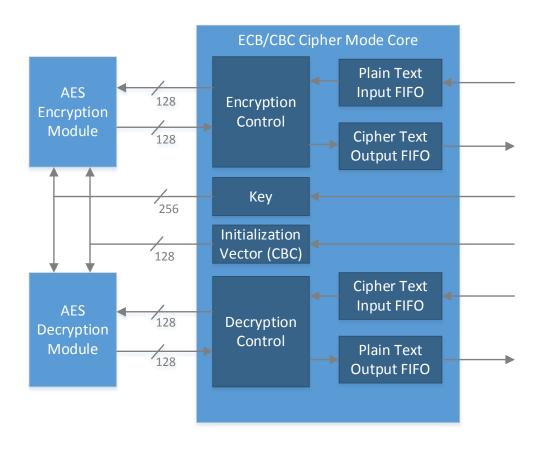

| Figure 5.4 | Control and Data Flow of the ECB/CBC Cipher Mode Cores  | 47   |

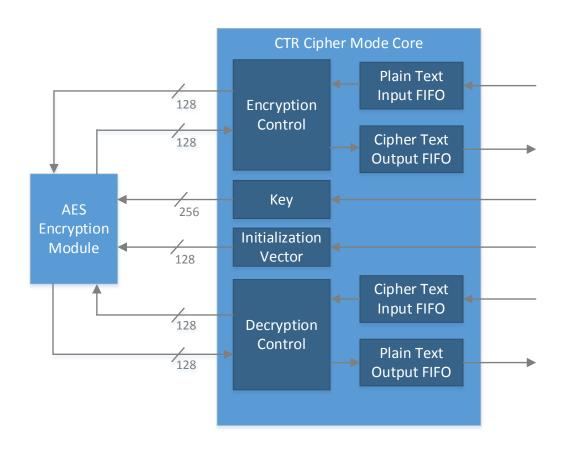

| Figure 5.5 | Control and Data Flow of the CTR Cipher Mode Core       | 48   |

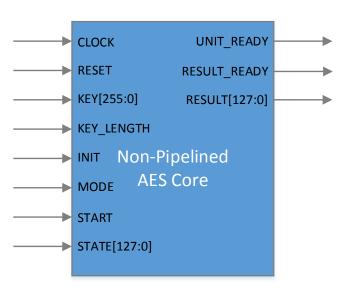

| Figure 5.6 | I/O Signals for Non-Pipelined AES IP Core               | 50   |

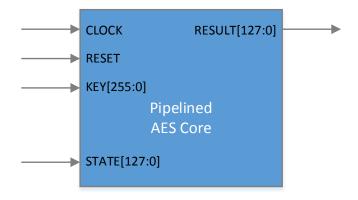

| Figure 5.7 | I/O Signals for Pipelined AES IP Core                   | 53   |

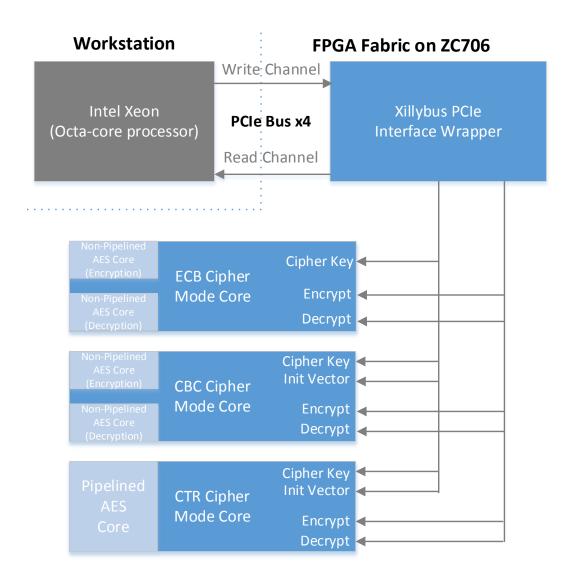

| Figure 5.8 | Top Level System View of Workstation Design             | 54   |

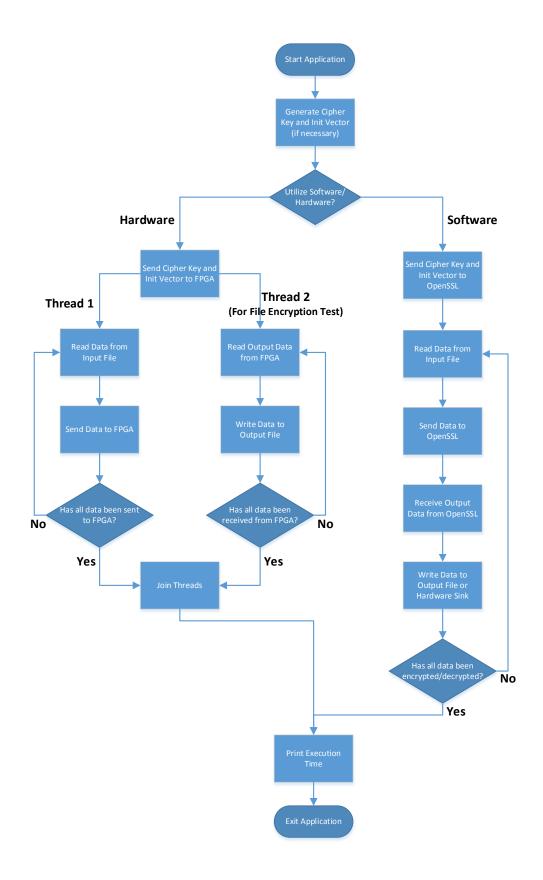

| Figure 6.1 | Flow Chart for Maximum Throughput Software Architecture | 61   |

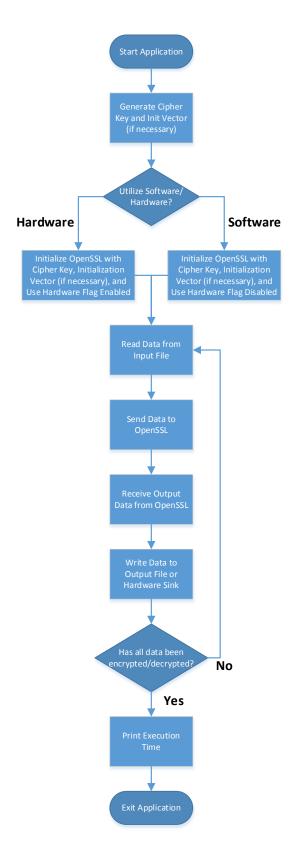

| Figure 6.2 | Flow Chart for OpenSSL Extension Software Architecture  | 63   |

| Figure 7.1 | Zedboard Development Board [29]                         | 65   |

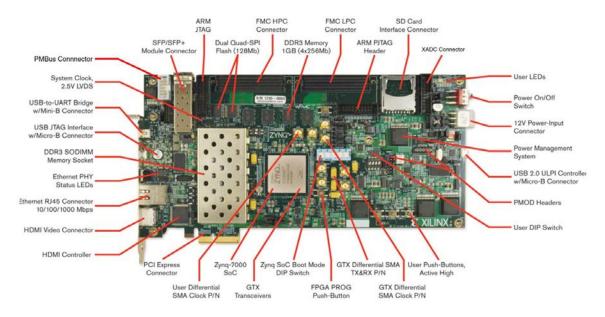

| Figure 7.2 | ZC706 Development Board [33]                            | 67   |

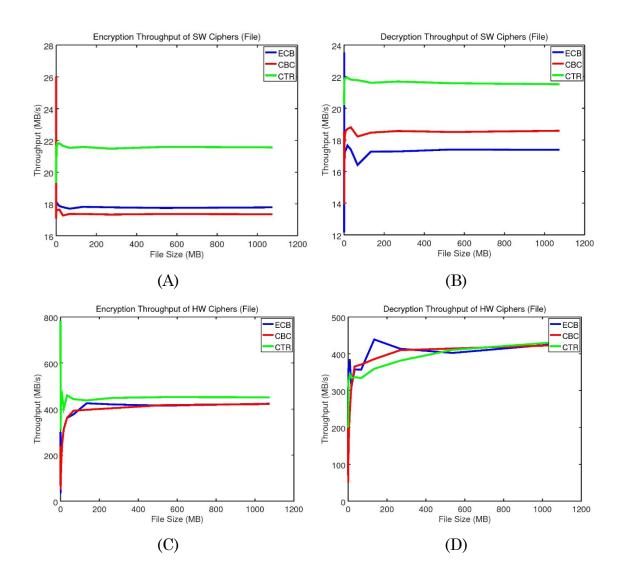

| Figure 9.1 (A) Encryption Throughput of Software Ciphers (File), (B) Decryption |

|---------------------------------------------------------------------------------|

| Throughput of Software Ciphers (File), (C) Encryption Throughput of Hardware    |

| Ciphers (File), (D) Decryption Throughput of Hardware Ciphers (File)82          |

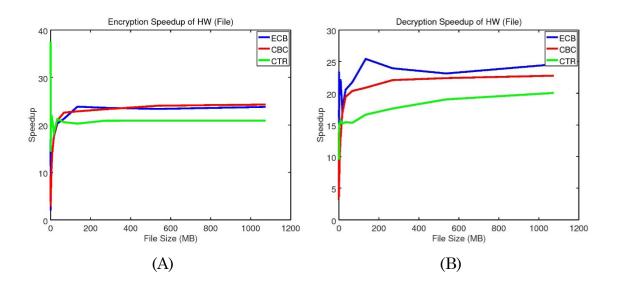

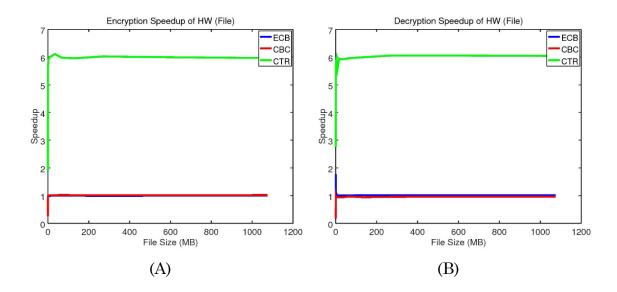

| Figure 9.2 (A) Encryption Speedup of Hardware Ciphers (File), (B) Decryption    |

| Speedup of Hardware Ciphers (File)                                              |

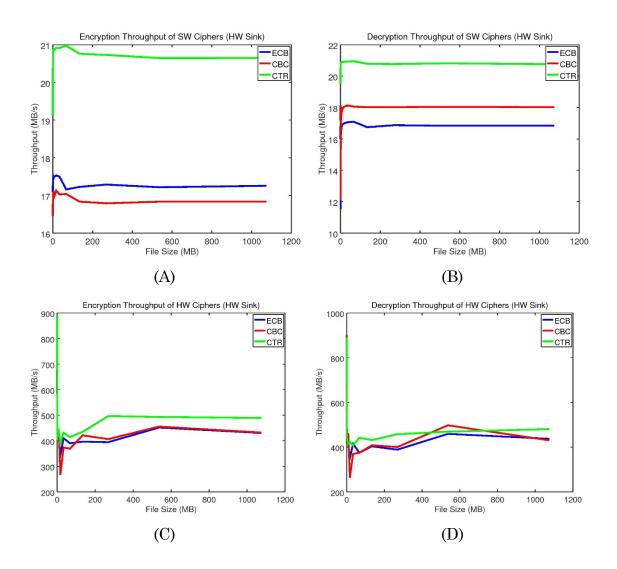

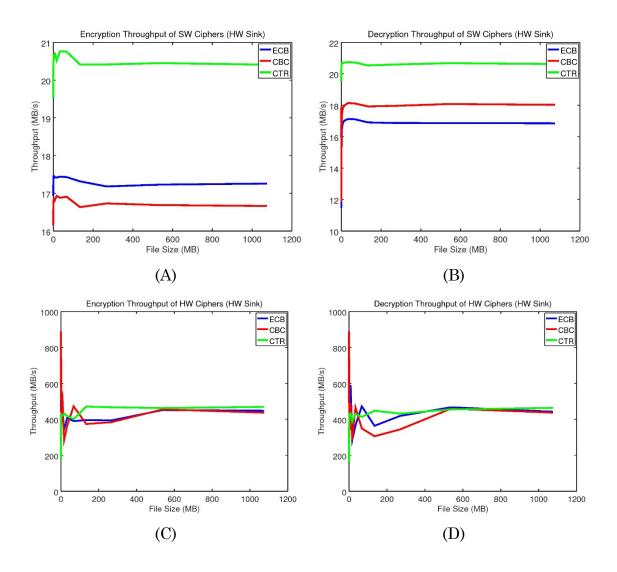

| Figure 9.3 (A) Encryption Throughput of Software Ciphers (HW Sink), (B)         |

| Decryption Throughput of Software Ciphers (HW Sink), (C) Encryption Throughput  |

| of Hardware Ciphers (HW Sink), (D) Decryption Throughput of Hardware Ciphers    |

| (HW Sink)86                                                                     |

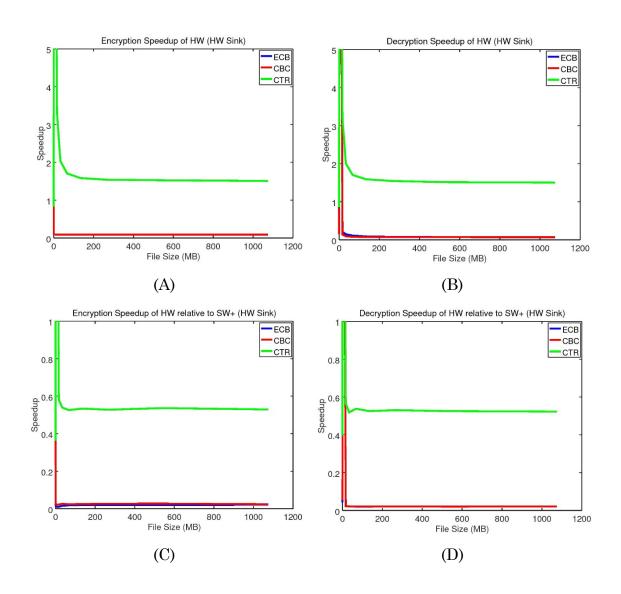

| Figure 9.4 (A) Encryption Speedup of Hardware Ciphers (HW Sink), (B) Decryption |

| Speedup of Hardware Ciphers (HW Sink)87                                         |

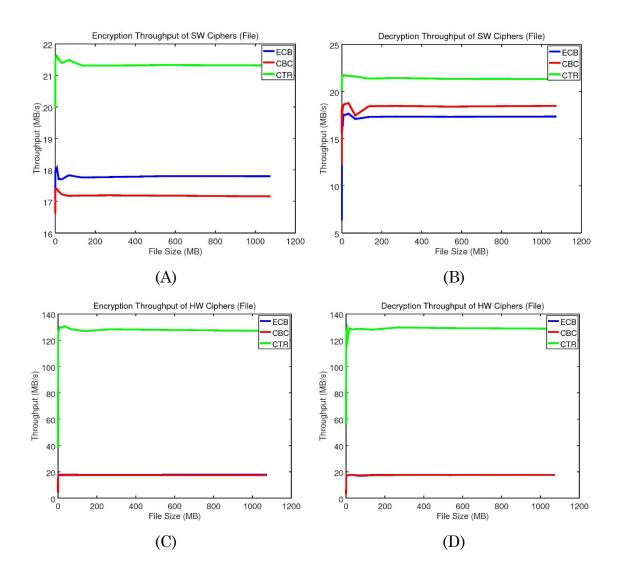

| Figure 9.5 (A) Encryption Throughput of Software Ciphers (File), (B) Decryption |

| Throughput of Software Ciphers (File), (C) Encryption Throughput of Hardware    |

| Ciphers (File), (D) Decryption Throughput of Hardware Ciphers (File)89          |

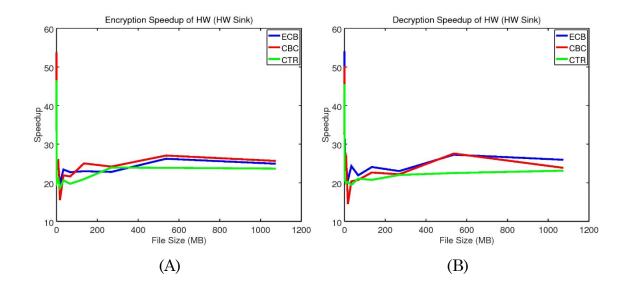

| Figure 9.6 (A) Encryption Speedup of Hardware Ciphers (File), (B) Decryption    |

| Speedup of Hardware Ciphers (File)90                                            |

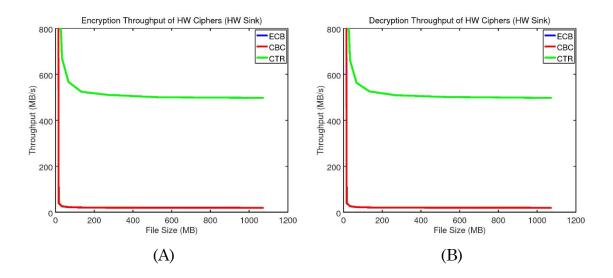

| Figure 9.7 (A) Encryption Throughput of Software Ciphers (HW Sink), (B)         |

| Decryption Throughput of Software Ciphers (HW Sink), (C) Encryption Throughput  |

| of Hardware Ciphers (HW Sink), (D) Decryption Throughput of Hardware Ciphers    |

| (HW Sink)92                                                                     |

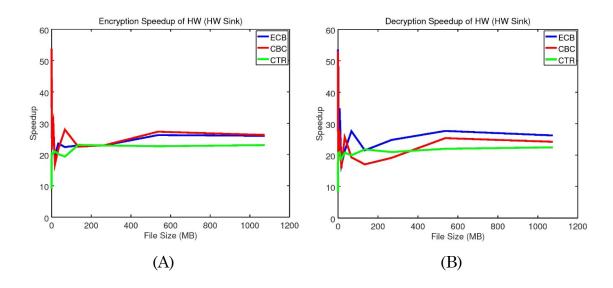

| Figure 9.8 (A) Encryption Speedup of Hardware Ciphers (HW Sink), (B) Decryption |

| Speedup of Hardware Ciphers (HW Sink)93                                         |

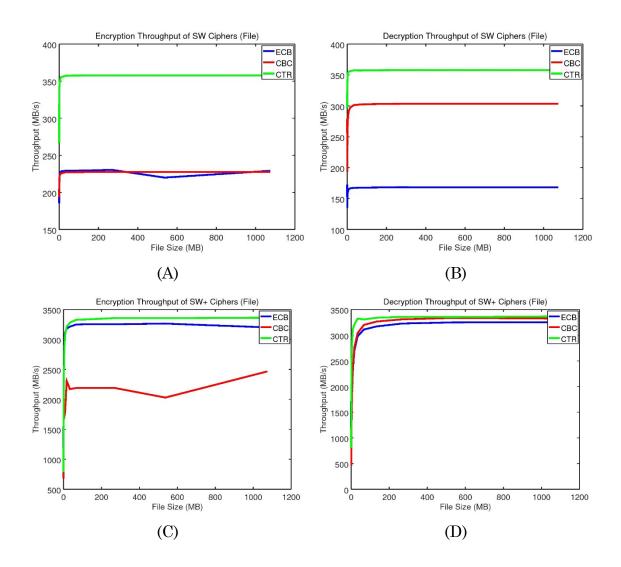

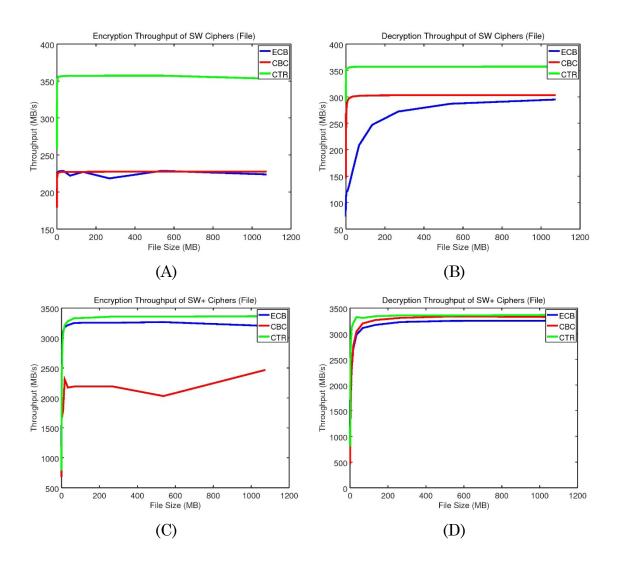

| Figure 9.9 (A) Encryption Throughput of Software Ciphers (File), (B) Decryption |

| Throughput of Software Ciphers (File), (C) Encryption Throughput of Software+   |

| Ciphers (File), (D) Decryption Throughput of Software+ Ciphers (File)98         |

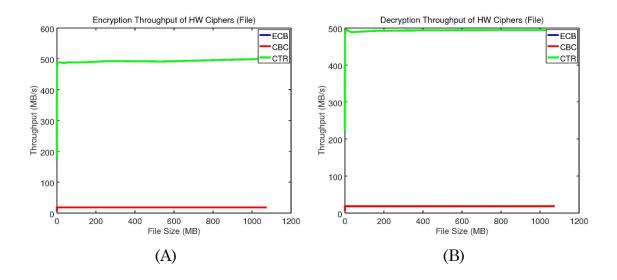

| Figure 9.10 (A) Encryption Throughput of Hardware Ciphers (File), (B) Decryption |

|----------------------------------------------------------------------------------|

| Throughput of Hardware Ciphers (Decryption)99                                    |

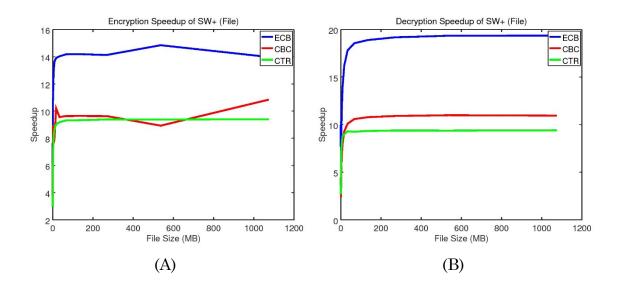

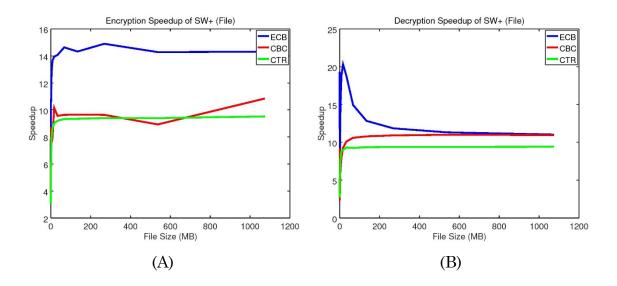

| Figure 9.11 (A) Encryption Speedup of Software+ Ciphers (File), (B) Decryption   |

| Speedup of Software+ Ciphers (File)                                              |

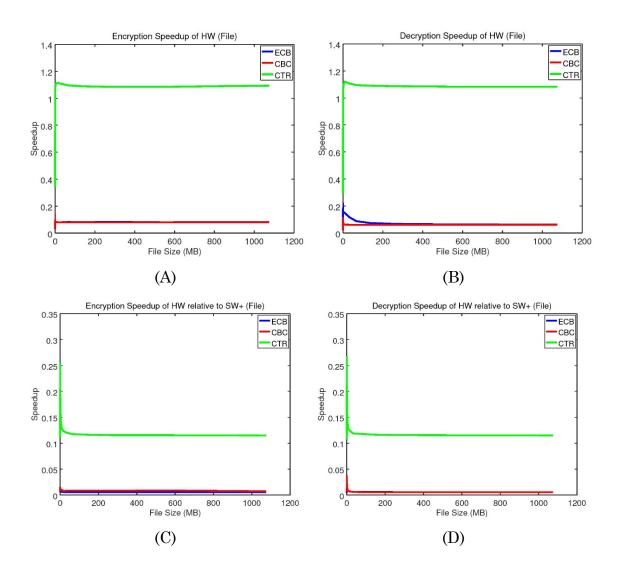

| Figure 9.12 (A) Encryption Speedup of Hardware Ciphers (File), (B) Decryption    |

| Speedup of Hardware Ciphers (File), (C) Encryption Speedup of Hardware Ciphers   |

| relative to Software+ Ciphers (File), (D) Decryption Speedup of Hardware Ciphers |

| relative to Software+ Ciphers (Decryption)                                       |

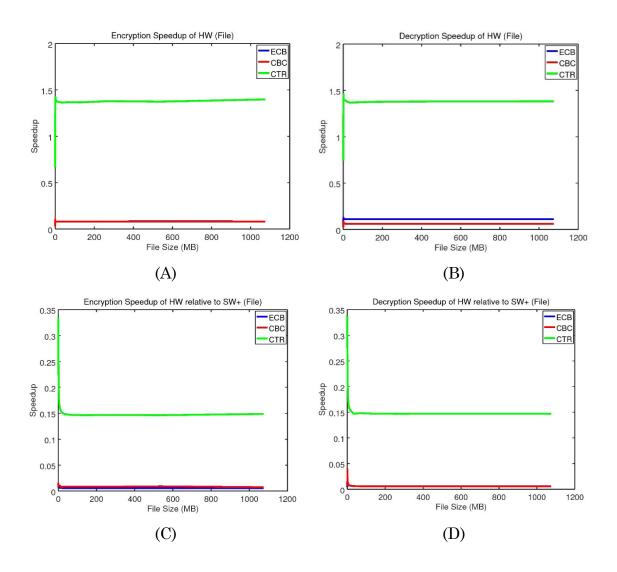

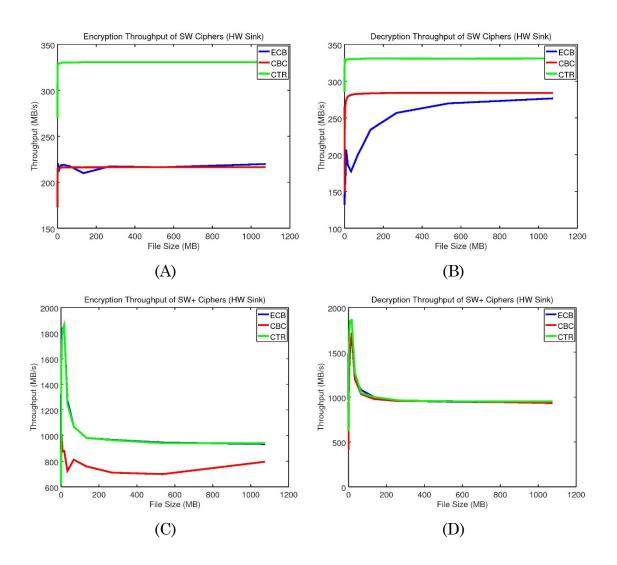

| Figure 9.13 (A) Encryption Throughput of Software Ciphers (HW Sink), (B)         |

| Decryption Throughput of Software Ciphers (HW Sink), (C) Encryption Throughput   |

| of Software+ Ciphers (HW Sink), (D) Decryption Throughput of Software+ Ciphers   |

| (HW Sink)                                                                        |

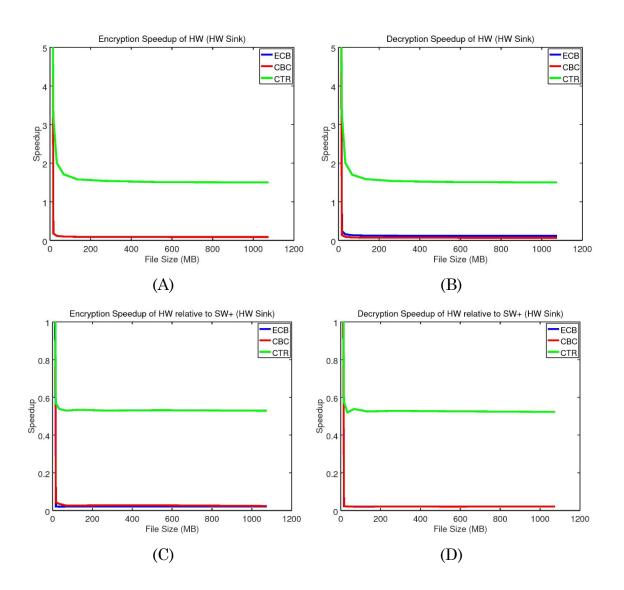

| Figure 9.14 (A) Encryption Throughput of Hardware Ciphers (HW Sink), (B)         |

| Decryption Throughput of Hardware Ciphers (HW Sink)105                           |

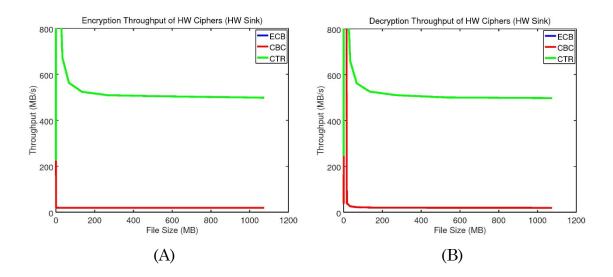

| Figure 9.15 (A) Encryption Speedup of Hardware Ciphers (HW Sink), (B)            |

| Decryption Speedup of Hardware Ciphers (HW Sink), (C) Encryption Speedup of      |

| Hardware Ciphers relative to Software+ Ciphers (HW Sink), (D) Decryption         |

| Speedup of Hardware Ciphers relative to Software+ Ciphers (HW Sink)106           |

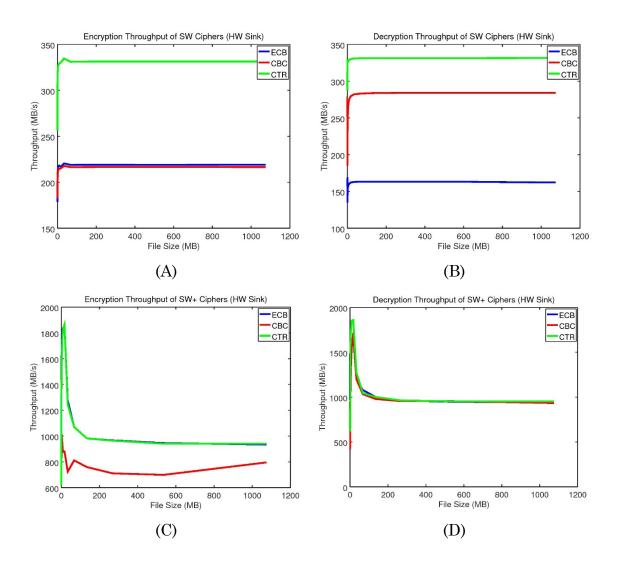

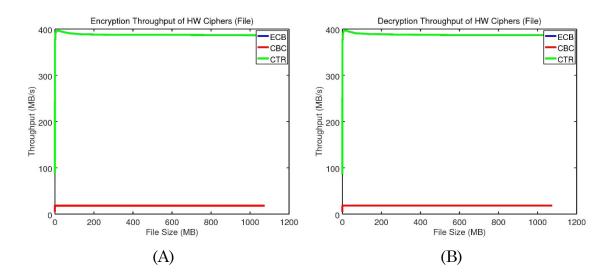

| Figure 9.16 (A) Encryption Throughput of Software Ciphers (File), (B) Decryption |

| Throughput of Software Ciphers (File), (C) Encryption Throughput of Software+    |

| Ciphers (File), (D) Decryption Throughput of Software+ Ciphers (File)109         |

| Figure 9.17 (A) Encryption Throughput of Hardware Ciphers (File), (B) Decryption |

| Throughput of Hardware Ciphers (File)                                            |

| Figure 9.18 (A) Encryption Speedup of Software+ Ciphers (File), (B) Decryption   |

| Speedup of Software+ Ciphers (File)                                              |

| Figure 9.19 (A) Encryption Speedup of Hardware Ciphers (File), (B) Decryption    |

|----------------------------------------------------------------------------------|

| Speedup of Hardware Ciphers (File), (C) Encryption Speedup of Hardware Ciphers   |

| relative to Software+ Ciphers (File), (D) Decryption Speedup of Hardware Ciphers |

| relative to Software+ Ciphers (File)                                             |

| Figure 9.20 (A) Encryption Throughput of Software Ciphers (HW Sink), (B)         |

| Decryption Throughput of Software Ciphers (HW Sink), (C) Encryption Throughput   |

| of Software+ Ciphers (HW Sink), (D) Decryption Throughput of Software+ Ciphers   |

| (HW Sink)                                                                        |

| Figure 9.21 (A) Encryption Throughput of Hardware Ciphers (HW Sink), (B)         |

|                                                                                  |

| Decryption Throughput of Hardware Ciphers (HW Sink)116                           |

| Decryption Throughput of Hardware Ciphers (HW Sink)                              |

|                                                                                  |

| Figure 9.22 (A) Encryption Speedup of Hardware Ciphers (HW Sink), (B)            |

# LIST OF TABLES

| Table                                           | Page |

|-------------------------------------------------|------|

| Table 7.1 File Sizes used for Test Applications | 70   |

#### CHAPTER 1

#### INTRODUCTION

The Digital Age has seen an ever increasing amount of data stored and transmitted across publicly accessed mediums, such as the Internet. A large portion of this data is confidential information that could harm individuals, corporations, and even governments if accessed by a malicious party. The critical importance of securing this data has led to the utilization of data encryption algorithms. Over time, there has been a multitude of cryptographic algorithms each designed with the goal of securing data more effectively. One such algorithm is the Advanced Encryption Standard (AES) which has emerged as a highly secure and easy to implement algorithm that is used by many corporations and government entities to secure their confidential information. AES, with the use of different cipher modes, has become the most widely used block cipher for securing information. Software implementations are the simplest and most common form of the AES algorithm; however, hardware implementations of the algorithm often improve speed, throughput, or save energy relative to their software counterparts, especially within an embedded computing environment with limited resources. The goal of this thesis is to explore any performance benefits of implementing hardware accelerated ciphers that use AES on an FPGA within an embedded and workstation environment. The rest of the Introduction section discusses the motivation, technology trends, the work done in the thesis and overview of the results, lists the contributions of this thesis, and gives the outline of the remainder of the thesis.

#### 1.1 Need for Data Encryption

The cyber hacking of data and information has become a common occurrence in the twenty first century. So many companies and even governments store confidential information about their customers and constituents, respectively. Also, with the increased use of the Internet for things such as shopping, etc. the sharing of personal information on the Internet is on the rise. Unfortunately, there are individuals and groups of people that exploit vulnerabilities in the computing systems that store and transmit this confidential information in order to gain access to the data for personal gain. It has become very difficult to identify and correct all possible vulnerabilities of a system that contains this data especially as attackers continue to invent new techniques for attacking systems and mediums. Therefore, it has become extremely important to be able to protect the data itself regardless of the system it resides on. This is accomplished through the use of data encryption. Data encryption is the process of using a private key to transform readable data into a code that cannot be read or understood by a human or computing device. The only way for the encrypted data to be placed back into a readable form is to decrypt the data using the original private key used to encrypt the data. Therefore, if the private key is kept secret then only the original user can view the actual data. Many different encryption algorithms have been developed in the past few decades, such as DES, AES, IDEA, MD5, SHA 1, and many more. Some of the algorithms have emerged as being more secure and harder to hack than others. Data encryption does not control who can access data and information, but rather it controls who can view it. Indeed, as long as data is correctly encrypted before being transmitted or stored

on an accessible medium or device then even if another party gains access to the data it will be in an unknown and unusable form.

# 1.2 Technology Trends

Software implementations of cipher modes and block ciphers have long been the most common and easiest form of protecting data. However, the requirements for higher bandwidth and performance and lower power consumption in modern applications led to more hardware implementations of these ciphers. Most notably, Intel introduced the AES New Instructions (AESNI) that extends the x86 instruction set architecture. AESNI instructions invoked by software rely on dedicated hardware in the chipset that is used to perform the cryptographic operations. This allows for the cryptographic operations to be performed much faster than in software implemented algorithms. The computing industry has also seen a significant rise in interest and manufacturing of heterogeneous computing systems that offer more flexibility to developers and can achieve higher computational and data throughputs than a homogeneous system. These heterogeneous platforms may have alternative processors on the same integrated circuit (IC) as the main processor or off-chip to the main processor. An example of an off-chip heterogeneous system is a workstation that contains a general purpose graphics processing unit (GPGPU) that resides on the PCIe bus. An example of an integrated heterogeneous platform is an All-Programmable System-on-a-Chip (APSoC), which contains a hard processor system and FPGA fabric on the same silicon die. These all-programmable chips allow designers to combine the strengths of the software programmability of a hard processor system and the hardware programmability of the FPGA fabric. A common design approach is to offload computational overhead from the hard processor

system to a hardware accelerator in the FPGA fabric to perform tasks faster and more efficiently.

#### 1.3 What Has Been Achieved

In this thesis, an experimental performance evaluation of software and hardware implementations of three AES-based cipher modes is performed. The ciphers are evaluated within an embedded and workstation environment. The three cipher modes that are implemented are the Electronic Codebook (ECB), Cipher Block Chaining (CBC), and Counter (CTR) mode. Each of the cipher modes uses AES as the block cipher. The OpenSSL open-source cryptographic library is used for the software implementation of each cipher and the hardware implementations are hosted on the FPGA fabric of the Zynq-7000 All-Programmable System-on-a-Chip. There are two software applications for testing the performance of the ciphers. One application is multithreaded whose purpose is to attempt to achieve maximum throughput for the hardware accelerated ciphers. The second application uses an extension added to OpenSSL to simplify the programming API used for accessing both software and hardware ciphers. Furthermore, there are two tests executed within each software application. A file encryption/decryption test and a hardware sink test. The file encryption/decryption test is designed to evaluate the performance of each cipher in the scenario of protecting data at rest and the hardware sink test is designed to test each cipher in the scenario of protecting data prior to sending data out from the computer. The performance of the software and hardware ciphers are compared using metrics of execution time, speedup, and throughput.

# 1.4 Contributions

This thesis makes the following contributions to the field of hardware accelerated cryptographic processing and heterogeneous computing on embedded and workstation computing environments:

- Provides an accurate performance comparison of highly optimized software cipher implementations and FPGA hardware accelerated cipher implementations using modern processors and FPGAs.

- Evaluates the potential performance improvements of hardware accelerated ciphers on embedded and workstation platforms through the use of heterogeneous computing.

- Evaluates the effects of bus architectures, system hard drives, and FPGA families on the performance of hardware accelerated ciphers.

- Creates environment for experimental-based evaluation of applications utilizing software and hardware accelerated ciphers.

#### 1.5 Outline of the Thesis

The remaining sections of this thesis are organized as follows. CHAPTER 2 discusses the background and motivation for the thesis. CHAPTER 3 discusses the related work from the open literature. CHAPTER 4 discusses the methodology for how the thesis work is accomplished. CHAPTER 5 discusses the specifics of the system designs for the embedded and workstation designs. CHAPTER 6 discusses the architecture and flow of the software applications used for testing and measuring the performance of the cipher implementations. CHAPTER 7 provides details regarding the embedded and workstation experimental environments for testing the implementations. CHAPTER 8 discusses the results of the micro-

benchmarking tests on different components of the system designs. CHAPTER 9 discusses the results for each test and software application combination. Finally, CHAPTER 10 discusses possible future work and conclusions drawn from the thesis work.

#### CHAPTER 2

#### BACKGROUND AND MOTIVATION

Data security is the process of protecting private or confidential information from being accessed by an unauthorized party on a public domain or private computer. Computers are owned in many more households and businesses now than ever before and they all contain personal information of individuals or proprietary information of companies and needs to be protected. Information is also transferred across public communication domains in extremely large amounts on a daily basis where some of the information transferred is not sensitive; however, much of the information is confidential to one or both of the communicating parties. Some of the information that is passed across the Internet domain includes banking information, personal identifiable information, tax information, and much more so it is very important to use data sharing techniques and algorithms in order to protect this information to guarantee that a malicious party that intercepts the data cannot read the information. A technique that has been used for many years is data encryption. There are many different data encryption algorithms and have all been successful at protecting the data entrusted to their algorithm. However, some have been more successful than others due to the evolution of more sophisticated software and hardware attacks against computers, networks, and the encryption algorithms themselves. Some examples of the software attacks are ciphertext only attack, known plaintext attack, chosen plaintext attack, chosen ciphertext attack, side channel attacks, brute force

attack, and birthday attacks. Examples of hardware attacks are man-in-the-middle attack, electromagnetic attack, and power analysis attacks [1].

Users can either use software-based or hardware-based encryption to protect data. Software encryption programs or much more prevalent than hardware solutions because it is cost effective, easily distributed, easy to use, upgrade, and update so it makes a good solution for individuals as well as large companies. Software encryption solutions are also readily available for all major operating systems. However, software solutions tend to only be as strong as the operating system of the base device and can also be very computationally intensive. Software solutions also have the possibility of being turned off by users or circumvented by attackers making them extremely vulnerable to attacks. The other option is hardware-based encryption solutions. Hardware solutions tend to be self-contained and does not require any additional software support making it essentially free from the possibility of contamination, malicious code infection, or vulnerability [2].

# 2.1 Advanced Encryption Standard (AES)

Symmetric cryptography is split into block ciphers and stream ciphers.

Stream ciphers encrypt bits individually, as shown in Figure 2.1. This is achieved by adding a bit from a key stream to a plaintext bit. On the other hand, block ciphers encrypt an entire block of plaintext bits at a time with the same key, as shown in Figure 2.2. This means that the encryption of any plaintext bit in a given block depends on every other plaintext bit in the same block. Block ciphers are much more common than stream ciphers for public communication domains such as the Internet. Stream ciphers are smaller, faster, and better suited for embedded devices

with little computational power; whereas, block ciphers require more compute and storage resources and are thus more suited for workstation environments [3].

Figure 2.1 Stream Cipher [3]

Figure 2.2 Block Cipher [3]

The Advanced Encryption Standard (AES) is the most widely used symmetric block cipher today. It is the standard block cipher for the US government and is also used in many industries and commercial systems. AES is used as the encryption standard for many protocols including Internet Protocol Security suite (IPsec), Transport Layer Security (TLS), the WLAN security protocols (IEEE 802.11i), and the secure shell network protocol (SSH) [3].

AES was developed by Joan Daemen and Vincent Rijmen and was adopted by the US National Institute of Standards and Technology (NIST) in 2001 as the new encryption standard for the US government. AES has three different key sizes of 128, 192, and 256 bits. The block size is 128 bits, or 16 bytes. A basic block diagram of AES is shown in Figure 2.3. The number of internal rounds of the cipher is a function of the key length and it is 10, 12, or 14 rounds for key length sizes of 128, 192, and 256 bits, respectively. The AES algorithm consists of so-called layers where each layer manipulates all 128 bits of the data block. The data block is also referred to as the state. There are three different layers and each round of the algorithm, with the exception of the first round, executes all three layers. The three layers are the Byte Substitution layer (S-Box), Diffusion layer, and the Key Addition layer. The Byte Substitution layer is where each byte in the state is substituted with another byte from a known lookup table that contains values with special mathematical properties. This byte substitution is a nonlinear transformation. The Diffusion layer has two sublayers of ShiftRows and MixColumn which perform linear operations on the state. The ShiftRows sublayer permutes the data on a byte level and the MixColumn sublayer is a matrix operation that combines blocks of four bytes used for mixing the data. Lastly, the Key Addition layer is where a 128-bit round key, derived from the main key, is XORed with the state. The round keys, or subkeys, for each round are generated by taking the original cipher key, any of the three lengths, and performing the key scheduling operation to produce a unique 128-bit subkey [3].

Figure 2.3 AES Block Cipher [3]

# 2.2 Cipher Modes of Operation

Block ciphers, such as AES, can be used as the base building block for a multitude of encryption schemes and to even create stream ciphers. The different ways of encryption are referred to as modes of operation. For this research, the modes of operation that were implemented were the Electronic Codebook (ECB), Cipher Block Chaining (CBC), and Counter Mode (CTR). AES is the block cipher used to implement the different modes of operation.

# 2.3 Electronic Codebook (ECB)

Electronic Codebook (ECB) is the most straightforward and simple way of encrypting data. Figure 2.4 shows the functional block diagram of the ECB cipher mode. ECB just uses the cipher key to encrypt each block of data. Each block of data is encrypted or decrypted independently from each other with the same key. Thus, data synchronization between the sender and receiver is not necessary for the ECB mode because even if some encrypted blocks are not fully received the rest of the encrypted data is not corrupted and can still be fully decrypted. ECB mode also has the ability to be parallelized since there are no data dependencies between different

blocks of data. However, for this research, the ECB mode was not parallelized due to hardware resource constraints which will be discussed in a later section. On the other hand, the ECB cipher has a few cryptographic weaknesses. The biggest weakness is that the cipher mode is highly deterministic. In other words, the same block of plaintext data will be encrypted identically to produce the same output ciphertext. Therefore, a potential attacker could perform a traffic analysis attack by just looking at the output ciphertext to determine if the same data was used multiple times. Next, due to the lack of data dependency between the data blocks and the absence of a message authentication code, the data blocks could be reordered or replaced by an attacker and the receiver would have no means to be able to detect it [3].

Figure 2.4 ECB Encryption/Decryption Block Diagrams

# 2.4 Cipher Block Chaining (CBC)

Cipher Block Chaining (CBC) is a mode in which encryption of all the blocks are chained together such that the current block is not only dependent on the previous encrypted block, but also on every other encrypted block before it. CBC uses a cipher key along with an initialization vector (IV) in order to encrypt the data. Figure 2.5 shows the functional block diagram of the CBC mode. The IV is used at the beginning of the encryption operation to XOR with the first plaintext block which is then passed through the block cipher, or AES in this case, to produce the output ciphertext. Furthermore, for each additional block of data to follow, the output ciphertext from the previous block is XORed with the current plaintext block before passed through the block cipher. The decryption process of CBC is just the inverse of the encryption process. The ciphertext is sent through the block cipher for decryption and then the output of the block cipher is then XORed with the input ciphertext from the previous data block. The last data block is XORed with the original IV to decrypt the data block. The end result is the original decoded data set. The strength of the CBC mode comes when a unique IV is used to encrypt each new data set. This is important because the same data set can be encrypted with a different IV and the resulting ciphertext outputs will be completely different which makes it impossible for an attacker to perform any sort of pattern detection. However, the IV does not have to be kept secret; only the cipher key must be kept secret [3].

Figure 2.5 CBC Encryption/Decryption Block Diagrams

# 2.5 Counter Mode (CTR)

The Counter Mode (CTR) uses a block cipher to implement a stream cipher. CTR mode uses a cipher key, an initialization vector (IV), and a counter value. Figure 2.6 shows the functional block diagram of the CTR cipher mode. The cipher key is used in the block cipher to perform the encryption operation on the input data into the block cipher. The input into the block cipher is a combination of the IV and the counter value. The values can be combined in one of two ways. Either the concatenation of the two values or by XORing the two values to create the 128-bit input into the block cipher. It is extremely important that the same counter value is not used more than once during the encryption of a data set because if an attacker knows one of two of the plaintext data blocks that were encrypted with the same

input to the block cipher (i.e. the same counter value) then he could compute the key to the block cipher and have the ability to decrypt all the other ciphertext output blocks. In order to guarantee a unique counter value for each block of data a large bit-width counter is used, such as 32 or 64 bits wide, so that a very large set of data (greater than ~32GB) can be encrypted before having to change the IV. The counter value is just incremented by one with each new block of data and then concatenated with the IV. The concatenated value is then encrypted by passing through the block cipher. The encrypted output from the block cipher is XORed with the input plaintext block of data which produces the output ciphertext. This process is completed for each input plaintext block. The CTR mode is highly parallelizable and does not contain any data dependencies or feedback requirements between the different blocks of data. The only requirement is that the same IV and counter value combination cannot be used to encrypt two different blocks of data within the same data set [3].

Figure 2.6 CTR Encryption/Decryption Block Diagrams

# 2.6 OpenSSL

The Secure Socket Layer (SSL) and Transport Layer Security (TLS) are used to secure applications that need to communicate over a network to ensure that the integrity of the data is upheld. OpenSSL is an open source library that implements the TLS and SSL protocols. OpenSSL is by far the most widely deployed, freely available implementation of these protocols. It also serves as a general-purpose cryptography library for numerous different types of block and stream ciphers [4]. The cryptographic library provides the most popular algorithms for symmetric key and public key cryptography, hash algorithms, and message digests, and a pseudorandom number generator. The library is full-featured and cross-platform, working on Windows, Linux, and Mac OS X operating systems (OS). The OS type is

detected at compile time so that the software is compatible and the compiler can optimize the library for the specific OS. The library is mainly used from within C and C++ applications, but can also be used within other languages such as Python, Perl, and PHP. One can also use OpenSSL from the command line [5].

In the context of this research, OpenSSL is used solely for its cryptographic functionality, specifically the highly optimized AES implementations. The reason OpenSSL is used is because it has become an industry standard for software implementations of cryptographic algorithms that can be used for both desktop and embedded environments. The library provides a high level Application Programming Interface (API) for interfacing to the different cryptographic functions. The high level API is known as EVP which provides the developer with similar function calls regardless of the cipher mode of operation in use. The library is also used for generating random cipher keys and initialization vectors during the encryption process by using a Password Based Key Derivation Function (PBKDF) available in the API. The PBKDF function implements a secure hashing algorithm for generating the cipher key and initialization vector [5]. The user has to then specify the correct password when decrypting data in order for the correct cipher key and initialization vector to be used to correctly decode the data.

# 2.7 All-Programmable SoCs (Zynq-7000)

Heterogeneous computing has emerged as computing platforms of choice that harness the Moore's Law to offer increased level of integration, customization, and computing power at minimal power consumption. Modern processor chips begin to reach their power consumption limits, which is inhibiting the clock rates from increasing any further. Heterogeneous computing allows for increasing

computational bandwidth, but does so with minimal power consumption compared to its homogeneous counterpart. An All-Programmable System-on-a-Chip (APSoC) is a type of heterogeneous computing platform that contains a hardened central processing unit (CPU) and a programmable logic fabric such as an FPGA. An example of an APSoC is the Zynq 7000 designed and manufactured by Xilinx, Inc.

The Zynq 7000 APSoC is a single integrated circuit that contains a hardened processor system (HPS) that includes a dual core ARM Cortex A9 and a programmable logic (PL) fabric to create a full heterogeneous computing system. Figure 2.7 shows an overview of the system architecture of the Zynq-7000 APSoC. The dual core ARM processors include multi-level cache hierarchy that maintains coherency between the two CPU cores, 256 KB of on-chip memory, 512 MB of DDR3 external memory, 8 channel DMA controller, vector processing units, and a large set of peripheral connectivity interfaces. Its peripheral interfaces include a gigabit Ethernet port, USB interfaces, CAN bus interfaces, SD card interface, and I2C interfaces. The PL, or FPGA fabric, on the Zyng 7000 is comparable to that of either the Artix-7 or Kintex-7 depending on the chip version. The FPGA fabric contains a host of block RAM units, hundreds of DSP slices, programmable I/O blocks, JTAG interface, PCI express block, high speed serial transceivers, and two analog-todigital converters. It provides a low power and high design flexibility for embedded designs with its large number of resources [6]. The ARM cores and the programmable logic communicate via a version of the Advanced Microcontroller Bus Architecture (AMBA) known as Advanced Extensible Interface (AXI). The AXI bus protocol provides a separate address and data channel for both the read and write operations and has a data width of up to 64 bits. The processors and FPGA can communicate in both directions simultaneously without any loss of throughput. The

Zynq contains both general purpose and high performance ports for communication with the FPGA fabric. The general purpose ports are 32 bits wide, where the ARM cores are the master and the PL is the slave. The high performance ports are 64 bits wide where the PL is the master and the memory interfaces on the HPS are the slave.

Figure 2.7 Zynq-7000 APSoC System Architecture

# 2.8 Xillybus

Xillybus is an open source Intellectual Property (IP) core developed by Xillybus, Ltd. that implements the necessary logic for the data transfer between IP cores implemented on a Field Programmable Gate Array (FPGA) and a host processor running Linux or Microsoft Windows [7]. Xillybus is provided with both a hardware IP core and a kernel driver module for full interaction between the host and FPGA. The host application and the FPGA design interact with well-known interfaces. The FPGA application logic connects to the Xillybus IP core through standard FIFO interfaces. The host application performs basic file I/O operations on pipe-like device files (i.e. open, read, write, close) such that there is no specific API for the Xillybus driver [8].

Xillybus works on both Xilinx and Altera FPGA's and System-on-a-Chip (SoCs). It is compatible with transport protocols of PCIe, AXI3, and AXI4. It can achieve maximum data throughput of 3.5 GB/s simultaneously in both directions depending on the FPGA and host capabilities [9]. It is compatible with Linux operating systems with kernel version greater than or equal to 2.6.36 and on Windows 7, 8, and 10. The applications that Xillybus is most suited for are data acquisition and playback, interfacing with hardware, custom computer peripherals, in-hardware logic verification, and coprocessing [7].

The AXI4 bus logic is for implementation on a Xilinx chip such as the Zynq-7000 APSoC and the PCIe bus version is for implementation within a workstation environment. The Xillybus IP core that resides in the FPGA has the ability to function as a slave or a master on the AXI4 bus. This dual functionality is very useful because Xillybus utilizes Direct Memory Access (DMA) in both the embedded

and workstation designs to move data between the processor and FPGA with minimal processor overhead [10]. Xillybus also provides a slower, memory mapped interface between the host and FPGA for basic register level access.

DMA is the process of transferring data to or from some destination without the interaction of the CPU. DMA not only decreases the computational load of the CPU, but also allows for an increase in the data throughput achieved by the communication interface because it makes use of burst transactions. With a burst transaction a large set of data is transferred from a source to a destination with a single address phase occurring on the bus, thus effectively increasing the effective bus throughput. If the CPU is involved in the data transfer it has to perform an addressing phase on the bus for every data transfer. This ultimately decreases the overall data throughput achieved on the bus which is why DMA is very appealing in high throughput applications.

Figure 2.8 shows a high level block diagram for Xillybus with the AXI4/PCIe bus. In the Xillybus design, the processor can initiate a DMA transaction when transferring data to the FPGA which behaves as the slave on the bus. The host processor will provide the DMA engine on the HPS with the memory address of the start of the data set to be transferred and a DMA burst transaction will transfer the data across the bus. A similar process is used for transferring data from the FPGA to the host processor. The user FPGA code just streams data into the provided Xillybus FIFOs, shown in Figure 2.8 as the Application FIFOs, and Xillybus uses an AXI DMA engine for initiating a DMA transfer across the bus. The data from the FPGA is transferred into a memory location in DRAM and the host processor can then access it. This means that the latencies experienced by the processor(s) when communicating with the FPGA is mainly affected by the latency of interfacing to the

DRAM and only when the DMA buffers are full is the latency affected by the actual bus latency. This significantly improves performance over the case where the processor is handling all transactions over the AXI4 bus since the processor does not have to wait for AXI4 transactions to complete before continuing with execution. Xillybus makes the communication across the AXI4 or PCIe bus transparent to the software/hardware developer which increases design simplicity and decreases development time. The only difference is in the bus protocol and possibly the DMA engine hardware on the host.

Figure 2.8 Xillybus Functional Block Diagram

The Xillybus website [7] provides a link called the IP Core Factory where one can create a custom IP core and kernel driver with any number of interfaces [11] [12]. The core designer can specify the interface names, bit widths, their purpose (i.e. coprocessing, data acquisition, video processing, etc.), and their expected bandwidth requirements. The website then uses this information to auto generate the VHDL and Verilog code for the FPGA IP core along with the kernel software driver code for interfacing with the FPGA core. This provides the user with the software and

hardware interface solutions for efficient communication between the processor and FPGA for a wide range of applications.

For this research, both the Xillybus AXI4 and PCIe versions are used for implementation on the Zynq-7000 APSoC on the Zedboard and ZC706 development boards, respectively. The use of the Xillybus IP core and kernel driver software greatly simplify the design process for the cipher hardware acceleration because all the necessary code for communicating between the processor and FPGA is provided, so more time and effort is spent on the development of the other system components.

# 2.9 Opportunity: Cryptographic Hardware Acceleration

Hardware accelerated cryptographic functionality is appealing because it not only can provide a stronger and more resilient form of security, but can also improve system performance and power consumption when performing cryptographic operations. Embedded computing is the most common form of computing, but it contains the least amount of resources and computing power compared to workstations, servers, etc. Therefore, the task of performing cryptographic operations on large amounts of data can be a very consuming task for embedded processors. Therefore, the possibility of offloading these cryptographic operations from the embedded CPU onto another form of computing platform can return large dividends in terms of performance and power consumption. Heterogeneous computing platforms provide and ideal environment for offloading such operations to a secondary computing platform. In this specific example, the cryptographic operations can be offloaded onto the secondary processing unit. Modern heterogeneous platforms, such as the Zynq-7000 APSoC, offer chipsets containing both a CPU and FPGA on the same die. The FPGA fabric of the Zynq can be used to

implement the cryptographic operations which has the potential to perform the operations faster while consuming considerably less power than the CPU.

#### CHAPTER 3

#### RELATED WORK

There has been an exceptionally large amount of research work done in the area of hardware acceleration for cryptographic operations, specifically AES. The majority of the accelerator implementations were completed on an FPGA and others on a general purpose graphics processing unit (GPGPU). Most of the implementations included multiple cipher modes such as ECB, CBC, CTR, GCM, and XTS that use AES as the block cipher.

Some of the prior AES coprocessor designs used soft-core processors in an FPGA for interfacing to an AES hardware core. Hodjat et. al. [13] [14] used the LEON soft processor in the ThumbPod SoC to implement the ECB, CBC, and OFB ciphers through a memory-mapped interface. They used a non-pipelined AES core clocked at 330 MHz to achieve a maximum throughput of 3.84 Gbit/s. Baskaran et. al. [15] implemented the AES block cipher using the Picoblaze microprocessor and other hardware cores on a Spartan 3E in order to achieve a very low-cost resource cryptographic design of only 460 slices on the FPGA. These softcore design approaches used the FPGA for the microprocessor and AES implementations with custom software executed on the soft-core microprocessor specifically designed for interfacing to the AES or cipher hardware implementations.

Other designs extended certain cryptographic software libraries to target the hardware accelerators as opposed to developing custom software for accessing and utilizing hardware coprocessors. Pedraza et. al. [16] ran Linux on a PowerPC hard

processor core using a Virtex II FPGA and extended the functionality of the CryptoAPI Linux cryptographic library to utilize the AES and DES hardware accelerators for implementing a secure file system. They were able to achieve a maximum throughput of 100 MB/s. Nambiar et. al. [17] extended the encryption function of the OpenSSL cryptographic library on the NIOS II soft-core microprocessor running uClinux real-time operating system (RTOS). It utilized a memory-mapped interface to the AES core inside the FPGA running at 50 MHz. They achieved a 2-3 times improvement over the full software implementation of OpenSSL. Hodjat et. al. [18] interfaced a hard CPU processor to an AES FPGA hardware accelerator for use in VPN and IPSec applications. They implemented the ECB, CBC, CTR, and CCM ciphers. They were able to achieve a throughput of 3.43 Gbit/s with a power consumption of 86 mW. Irwansyah et. al. [19] extended the instruction set of the Nios II reduced instruction set computer (RISC) processor to support AES encryption and decryption. The designs in [17] and [19] only implement the base AES encryption and decryption algorithms and not full cipher modes such as ECB or CBC.

An initial version of just the embedded design from this research was completed and published by myself et. al. [20] at an ACM Southeast Conference. This initial design did not have the ability to dynamically provide a private key or initialization vector to the FPGA from software, was only implemented on the Zedboard embedded platform, and did not include the necessary hardware and software for conducting the hardware sink test present in this Thesis.

The research presented in this Thesis is different than the previously mentioned designs in several different areas. The differences include that it uses a more modern and powerful chipset in the Zynq-7000 APSoC, it uses direct memory

access (DMA) for transferring data to/from the hardware ciphers, implements the design in both an embedded and workstation environment, utilizes two different bus architectures for data transfer. The Zyng-7000 APSoC contains both a hardened dual core ARM processor with an FPGA fabric on the same chip. Pedraza et. al. [16] used a PowerPC RISC hard processor on a Virtex II FPGA, but this research utilizes the ARM cores of the Zyng-7000 which are more powerful and full featured than the PowerPC processor. The FPGA fabric of the Zynq-7000 is also larger with more modern fabric technology than the legacy FPGAs that were used in the previously discussed designs. Another difference between this research and past research is the use of DMA for transferring data to/from the FPGA hardware accelerator. Most of the previous work used some form of a memory-mapped interface for interfacing the processor to the FPGA cores that caused the CPU to play a role in the transfer of data. The use of DMA in this research allows for data to be transferred to/from the FPGA without the CPU having to participate in the transfer. This increases the effective throughput of the data transfer and decreases the load on the CPU. This research also implements the same hardware acceleration design on both an embedded and workstation platform. The embedded implementation uses a Zedboard and the workstation implementation uses a Dell Precision Tower 7910 with the ZC706 development board. Both designs use the Zynq-7000 APSoC for implementing the hardware acceleration on the FPGA with either the ARM cores or Intel cores as the host processors for the embedded and workstation implementations, respectively. All the previously discussed research implemented the designs within an embedded environment, but did not attempt to implement the designs on multiple platforms. Based on the platform that the design is implemented on also determines the bus architecture that is used for transferring the data to/from the FPGA hardware accelerator. The embedded platform utilized the AXI4 bus within the Zynq-7000 SoC, but the workstation platform utilized the PCIe bus. Even though a different bus architecture is used for each platform implementation, the overall system design and architecture of the hardware acceleration and the software for driving the experimental setup is the same. This portability of the design is possible through the use of Xillybus. This portability is unique to this research as none of the previously discussed research made any mention as to their designs being compatible on multiple computing platforms. This research also implements multiple ciphers; ECB, CBC, and CTR ciphers, whereas, some of the previous work only implemented and tested the AES block cipher independent of any cipher implementation. Nambiar et. al. [17] extended just the encryption function of the AES block cipher with the OpenSSL library; however, this research extends both the encryption and decryption function of the ECB, CBC, and CTR ciphers.

#### CHAPTER 4

#### **METHODOLOGY**

The main goals of this research is to experiment with the possible performance improvements of hardware accelerated ciphers compared to the equivalent software-only counterparts. There are three cipher modes implemented and tested for this research; the ECB, CBC, and CTR cipher modes with the 256-bit key AES as the block cipher. All three of the cipher modes are implemented in both software and hardware. The software ciphers use the OpenSSL cryptographic library while the hardware ciphers reside on the FPGA fabric of the Zynq-7000 APSoC. In order to test the software and hardware ciphers, two different tests are executed inside the software applications. One test is used for performing file encryption and decryption while the second test is used for sending encrypted/decrypted data to a hardware sink. The file encryption/decryption test evaluates the full functionality of the cipher modes implemented in software and hardware along with the performance of each. It is also used to test the use case of encrypting/decrypting data at rest on a computing platform, such as data on the hard drive. On the other hand, the test for sending encrypted/decrypted data to a hardware sink is used to experiment with the use case where raw data is sent to a hardware peripheral, such as an Ethernet port, and the cryptographic operations are performed in the hardware prior to arriving at the peripheral. This situation eliminates the case where the CPU has to wait for the return of the data from the hardware. The performance results of each test for the software and hardware

ciphers are recorded and then compared in order to analyze any performance improvements achieved by the hardware ciphers over the software ciphers.

Each of the two tests, file encryption/decryption and hardware sink test, are contained inside a single software application. Furthermore, there are two different software applications, or architectures, that are used for testing the software and hardware ciphers. Each software application can execute both types of tests. One software architecture is designed to maximize the data throughput of the hardware acceleration; whereas, the second software architecture is designed to present a more simplistic programming API to the software developer by extending the well-established OpenSSL EVP API. These two software architectures are used to conduct the tests on the ciphers using different programming models.

There are also two different hardware setups used for implementing the software and hardware ciphers. There is an embedded and workstation hardware setup. The embedded environment is hosted on the Zynq-7000 APSoC on the Zedboard development platform which uses the dual ARM core processors for the software ciphers and the FPGA for the hardware accelerated ciphers. The workstation hardware setup uses an Intel CPU to host the software ciphers and also uses the FPGA fabric of the Zynq-7000 APSoC to host the hardware accelerated ciphers similar to the embedded hardware setup. The workstation hardware setup uses the ZC706 development board, which contains a Zynq-7000 APSoC, to interface to the Intel CPU for the hardware acceleration.

### **CHAPTER 5**

#### SYSTEM DESIGNS

There are two main system designs for this research. There is an embedded design and a workstation design. Both designs utilize the Zynq-7000 APSoC heterogeneous platform for implementing the hardware accelerated cipher modes on the FPGA fabric, but each system design consists of a different processor host for the software. The embedded design is implemented on the Zedboard development platform so it uses the dual ARM core processor to host the software portion of the system and communicates with the hardware accelerator via the AXI4 bus. The workstation design has the hardware accelerated ciphers implemented on the ZC706 development board and an Intel Workstation platform hosts the software portion of the system and communicates with the hardware accelerator via the PCIe bus.

The architecture of the system is similar between the two system designs with the exception of the bus architecture and host CPU. The embedded design utilizes the AXI4 bus and an ARM CPU; whereas, the workstation design utilizes the PCIe bus and an Intel CPU. The overall data flow and control of the systems are the same between the two designs. The main components of the system designs are the host processor, the Xillybus interface solution, the cipher mode cores, and the AES block cipher IP cores. The host processors and the Xillybus software and hardware cores are different between the embedded and workstation designs, but the cipher mode cores and AES IP cores are the exact same between the two designs. The software that executes on the host processor for each design is the same as well

with the exception of the memory mapped interface for providing the cipher key and initialization vector to the FPGA. The one feature of the designs that allows for this compatibility in functionality across the two design environments is the use of the Xillybus interface solution. Xillybus provides a full software and hardware solution for interfacing across the AXI4 and PCIe buses and provides the same software and hardware interfaces to the developer regardless of the bus type. Therefore, the same system architecture can be applied around the Xillybus solution transparent to the target platform.

There are two different AES block cipher IP cores used in the designs. There is a non-pipelined and a fully pipelined core. The non-pipelined core is used for the ECB and CBC cipher modes. Two instantiations of the non-pipelined core are present in each of the ECB and CBC cipher mode cores. One instantiation is used solely for the encryption process and the other is used solely for the decryption process. This allows for the simultaneous use of both the encryption and decryption process for these cipher modes. The fully pipelined core is used for the CTR cipher mode. Only one instantiation of the AES core is present for the CTR mode because the pipelined core consumes a large amount of resources so there was not enough resources in the FPGA fabric on the Zedboard. Therefore, the encryption and decryption processes can only be executed one at a time for the CTR cipher.

The following two sections, Section 3 and Section 5.2, will discuss both the embedded and workstation system designs in more detail. Each section will discuss details of each of the main components of the system and the roles each played in the overall design. The section discussing the workstation design will only elaborate on the parts of the system that is different from the embedded system.

# 5.1 Embedded System Design

The embedded system design is implemented on the Zedboard development platform and uses the onboard Zynq-7000 APSoC for hosting the software and hardware portions of the system design. The top level functional block diagram for the embedded system is shown in Figure 5.1. It shows how the dual ARM core processor is connected to the FPGA fabric via the AXI4 bus. The design uses the hardened DMA engine for transferring data from the CPU to the FPGA which uses a 32-bit General Purpose (GP) port for the data transfer. For transferring data from the FPGA to the CPU, the Xillybus IP core implemented in the FPGA design uses an AXI DMA engine. This DMA engine interfaces to the HPS of the Zynq-7000 via a 64-bit Accelerated Coherency Port (ACP) which allows the FPGA to transfer data directly into the DRAM memory without having to go through the CPU. The Xillybus IP core interfaces to each of the three cipher mode cores and the cipher mode cores interface to an AES block cipher IP core. The ECB and CBC cipher mode cores interface to the non-pipelined AES core and the CTR cipher mode core interfaces to the pipelined AES core.

Figure 5.1 Top Level System View of Zedboard Embedded Design

# 5.1.1 ARM Cores

The hardened processor system (HPS) of the Zynq-7000 APSoC consists of a dual ARM Cortex A9 Application Processor Unit (APU). It has a computation throughput of 2.5 Dhrystone Million Instructions per Second (DMIPS)/MHz per CPU. Each CPU can be clocked at a maximum clock frequency of 1 GHz. Therefore, at 2.5 DMIPS/MHz, if each CPU was clocked at 1 GHz then each CPU would ideally

achieve 2.5\*1000 = 2,500 DMIPS. This produces a combined throughput of 5000 DMIPS across both cores. For the design implemented for this research, each core was provided a clock at a rate of 666 MHz. The Zynq also maintains memory coherency across both processors. The Cortex A9 cores implement the ARMv7-A hardware architecture which contains TrustZone security features and the Thumb-2 instruction set architecture (ISA). The cores also contain the NEON vector processing unit for high throughput vector processing. It contains both single and double precision Vector Floating Point Unit (VFPU). It has three watchdog timers, one global timer, and two triple-timer counters. Each CPU core contains a separate instruction (L1I) and data (L1D) caches that are 32 KB each with a 4-way set-associativity. Both CPU cores share a level 2 unified cache (L2U) that is 512 KB with an 8-way set-associativity [6].

The dual ARM core processors are the supporting hardware for executing the software test applications. The ARM cores are booted with a version of the Ubuntu 12.04 kernel known as Xillinux. Xillinux is a Xillybus produced kernel and will be discussed in more detail in Section 7.2. The Xillinux OS is used for developing and executing the test software necessary for testing the software and hardware ciphers of the system design. The OS is also where the OpenSSL cryptographic library is installed and accessed for the software ciphers. The OS also has the Xillybus kernel driver software installed for access while interfacing to the hardware ciphers.

# 5.1.2 Xillybus Kernel Driver

Xillybus offers both a software and hardware package for interfacing across the AXI4 bus. The software package, in the form of a kernel module driver, is designed to present the Linux host with a simple and well-known interface. The host

kernel driver generates device files that behave like named pipes. They are opened, read from and written to just like any file, but behave much like pipes between processes or TCP/IP streams. To the program running on the host, the difference is that the other side of the stream is not another process (over the network or on the same computer), but a FIFO in the FPGA. Just like a TCP/IP stream, the Xillybus stream is designed to work well with high-rate data transfers as well as single bytes arriving or sent occasionally [21].

The interface to the Xillybus driver software from any user application is done through device files. The device files are auto generated by the kernel driver when it is loaded into the OS and detects a Xillybus compatible device on the bus. Also at driver load, the DMA buffers for bus communication are allocated in DRAM and their location(s) are provided to the Xillybus IP core for all the Xillybus streams present. During application execution, a handshake protocol between the FPGA and host makes an illusion of a continuous data stream. However, behind the scenes, DMA buffers are filled, handed over, and acknowledged in both directions, thus hiding the latency experienced by the transfer of data across the bus [21].

For the embedded design on the Zedboard, there are seven Xillybus interfaces present. One of the interfaces is a Xillybus Lite interface, which is the memory-mapped interface, for providing the cipher key and initialization vector to the hardware ciphers after being generated in software. The memory-mapped transactions are handled by the CPU and not the DMA engine. The other six interfaces are stream interfaces for sending and receiving data to and from the hardware ciphers. There is a separate interface for the encryption process and an interface for the decryption process for each cipher. Thus, each cipher has two separate full-duplex interfaces. The AXI4 bus is a full duplex bus so data can be

transferred in both directions without a decrease in bandwidth. Since there are separate interfaces for each of the ciphers and separate interfaces for the encryption and decryption process, multiple operations can be executed simultaneously. However, by performing multiple operations on the hardware accelerated ciphers the overall throughput of each operation will be diminished since the bus is shared for all data streams. Each of the stream interfaces are configured to achieve maximum bandwidth on the AXI4 bus and in order to do so Xillybus reserves DMA buffers in the DRAM. For each of the six stream interfaces in the embedded design there are 32 x 128 KB, or 4 MB, buffers reserved for the DMA buffers.

The host processor sends data to the FPGA through the use of DMA transactions. A DMA transaction is initiated by the processor by providing the DMA engine with the DRAM memory location for the beginning of the data set to be transferred across the bus. The DMA engine then initiates a DMA transaction on the AXI4 bus and transfers the entire data set to the FPGA, or at least a data block for which there is room in the FPGA FIFOs. The data is transferred from the host to the FPGA via the 32-bit general purpose (GP) AXI ports where the DMA engine is the master and the FPGA is the slave. If there is not enough room in the FPGA FIFOs to receive all the data from the processor then the DMA only transfers what it can and waits until the next transaction to send the remaining data.

#### 5.1.3 AXI4 Bus

The Advanced eXtensible Interface (AXI) protocol is part of the ARM

Advanced Microcontroller Bus Architecture (AMBA) which is proprietary to ARM.

The AXI protocol is designed and used for inter device communication via a bus interface for high throughput communication. The first version of AXI was released

in 2003 and the second version (AXI4) was released in 2010. The Zynq-7000 APSoC uses the AXI4 architecture. There are three types of AXI4 interface; AXI4, AXI4-Lite, and AXI4-Stream. The base AXI4 interface is used for high-performance memory-mapped interfaces, the AXI4-Lite interface is for simple, low-throughput memory-mapped interfaces, and the AXI4-Stream interface is for high-speed data streaming [22].

The AXI bus protocol allows for any number of devices to reside on the bus. Furthermore, for any transaction to occur on the bus, there has to be a master that initiates the transaction and a slave that is the recipient of the transaction from the master node. Both the AXI4 and AXI4-Lite interfaces consist of five different signal channels: read address channel, write address channel, read data channel, write data channel, and write response channel. Data can be transferred in both directions on the bus between the master and slave devices simultaneously. The separate address and data lines for both the read and write channels is what allows for this simultaneous bidirectional communication [22].

The bus transactions for memory-mapped interfaces, AXI4 and AXI4-Lite, involve the idea of a destination address within a system memory space; therefore, each transaction that occurs on the bus includes an address phase and a data phase. The address phase specifies that target address for the data and the data phase provides the data for the target address. The AXI4-Lite interface only allows a single data transfer per transaction which makes it ideal for register access type interfaces. The AXI4 interface allows a burst transaction of up to 256 data transfers per transaction. The AXI-Stream interface is different from the memory-mapped interfaces in that it does not require an address phase in a transaction and the AXI4-Stream interface is unidirectional. The write channel of the AXI4-Stream

interface is modeled after the AXI4 interface, except there is no address channel and the Stream interface can burst an unlimited amount of data in any transaction [22].

The embedded design implemented on the Zedboard utilizes both the AXI4-Lite and AXI4-Stream interfaces. The AXI4-Lite interface is used for providing the hardware accelerator cores with the cipher key and initialization vector prior to executing the cipher modes. The AXI4-Lite interface is used for this functionality because the basic register level access needed for providing this information to the hardware did not call for a high throughput interface, so the simplistic Lite interface is adequate. The AXI4-Stream interface is used for streaming the raw data to and from the hardware for performing the cipher operations on the data. The AXI4-Stream interfaces provided the ability to burst an unlimited amount of data in any given transaction on the bus which allowed the system to achieve maximum throughput for the bus. It is also worth noting that the AXI4 bus has a maximum clock frequency of 125 MHz and the design implemented for this research uses a clock frequency of 100 MHz.

#### 5.1.4 Xillybus IP Core

The Xillybus IP core is the full solution for interfacing with the host ARM processor via the AXI4 bus from the FPGA fabric of the Zynq-7000 APSoC. The overall Xillybus FPGA solution includes multiple sources and core modules all connected together, but for simplicity it will all be referred to as a single block box module which is how the solution is used in the design. The purpose of Xillybus is to provide the developer with a well-known and easy-to-use interface for communicating with the ARM processors via the AXI4 bus.

Xillybus contains three main components: the AXI4 slave interface, the AXI4 master interface, and the interface to the backend user application. The AXI4 slave interface is used for receiving data from the host ARM processors through the memory-mapped or data stream interfaces. The data is received on this interface through the 32-bit GP ports. The memory-mapped transactions across the slave interface are basically just passed straight through to the user application with all the necessary signals for the user design to react to the transactions, but the Xillybus core still handles all the low level AXI4 handshaking. The data stream interface(s) from the CPU to the slave interface is handled much differently than the memory-mapped interface. Each Xillybus interface present in the design has its own FIFO of at least 2 KB deep in each direction to help hide the latencies of the bus transactions. These FIFOs are used to receive a stream of data from the processor through DMA transactions. The FIFOs help buffer data as it is received from the bus in the burst transactions just in case the backend user logic is not consuming the data at the same rate as the data transfer. However, eventually, if the user logic is consuming data too slow and the Xillybus FIFOs become full, then the DMA engine on the HPS will stall due to backpressure from the FPGA slave interface. The master AXI4 interface of the Xillybus core is naturally just the reverse of the slave interface. Xillybus implements an AXI DMA engine inside the core for interfacing to the 64-bit Accelerated Coherency Port (ACP) of the HPS. The ACP provides direct access to the DRAM. Therefore, the AXI DMA engine can transfer data from the FPGA back to the DRAM (and host processor) through the ACP interface. Thus, all the user logic must do when transferring data to the host is move data into the outgoing data FIFO provided by Xillybus and the AXI DMA engine will transfer the data into the DMA buffers present in the DRAM. As eluded to, the interface signals

that are provided to the backend user application logic are the memory-mapped interface signals and standard FIFO interface signals for the data stream interfaces for communicating in both directions. The FIFO interfaces are standard FIFOs without the first-word-fall-through (FWFT) feature. The entire Xillybus module is clocked off of the 100 MHz AXI4 bus clock. This makes the entire core synchronous to the AXI4 bus [23].