# HARDWARE DATA VALUE TRACING IN MULTICORES

by

# MOUNIKA PONUGOTI

# A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

HUNTSVILLE, ALABAMA

2019

| In presenting this dissertation in partial | fulfillment of the requirements for a Doctor  |

|--------------------------------------------|-----------------------------------------------|

| of Philosophy degree from The Universit    | y of Alabama in Huntsville, I agree that the  |

| Library of this University shall make      | it freely available for inspection. I further |

| agree that permission for extensive copy   | ying for scholarly purposes may be granted    |

| by my advisor or, in his/her absence, by   | the Chair of the Department or the Dean of    |

| the School of Graduate Studies. It is als  | so understood that due recognition shall be   |

| given to me and to The University of A     | alabama in Huntsville in any scholarly use    |

| which may be made of any material in th    | is dissertation.                              |

|                                            |                                               |

|                                            |                                               |

|                                            |                                               |

| (student signature)                        | (date)                                        |

|                                            |                                               |

# DISSERTATION APPROVAL FORM

Submitted by Mounika Ponugoti in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the dissertation committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this dissertation. We further certify that we have reviewed the dissertation manuscript and approve it in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering.

|                             |        | Committee Chair  |

|-----------------------------|--------|------------------|

| (Dr. Aleksandar Milenkovic) | (date) |                  |

| (Dr. Rhonda Gaede)          | (date) | Committee Member |

| (D1. Iviolita Gaette)       | (date) |                  |

| (Dr. Mohammad Haider)       | (date) | Committee Member |

|                             |        | Committee Member |

| (Dr. Tauhidur Rahman)       | (date) |                  |

| (Dr. Earl Wells)            | (date) | Committee Member |

| (DI. Barr World)            | (dave) |                  |

| (D. D. : C.                 | (1 + ) | Department Chair |

| (Dr. Ravi Gorur)            | (date) |                  |

| (Dr. Shankar Mahalingam)    | (date) | College Dean     |

|                             |        | Graduate Dean    |

| (Dr. David Berkowitz)       | (date) | Gradate Dean     |

# ABSTRACT

# The School of Graduate Studies The University of Alabama in Huntsville

| Degree <u>Doctor of Philosophy</u>        | College/Dept. Engineering/Electrical & |

|-------------------------------------------|----------------------------------------|

|                                           | Computer Engineering                   |

|                                           |                                        |

| Name of Candidate <u>Mounika Ponugoti</u> |                                        |

| Title Hardware Data Value Tracing in Mu   | ulticores                              |

Embedded computing systems powered by modern systems-on-a-chip (SoCs) running sophisticated software applications are indispensable in modern communication, transportation, infrastructure, medicine, military, and entertainment. Semi-conductor technology trends have enabled the design of SoCs that often combine multiple processor cores, hardware accelerators, direct memory controllers, and peripheral interfaces, all connected through an on-chip interconnect. Faster, cheaper, and smaller SoCs have in turn enabled new applications that may have tens of millions of lines of code. These trends have led to rising software engineering costs in modern embedded systems that currently account for over 80% of the total engineering costs. Recent studies found that software developers spend over 50% of their time finding and fixing software bugs. Thus, software debugging is one of the most challenging aspects of embedded system development due to growing hardware and software complexity, limited visibility of system components, and tightening time-to-market. Providing powerful debugging tools to software developers is thus critical to expedite software development and improve software reliability.

To find software bugs faster, developers often rely on on-chip trace modules with large buffers to capture program execution traces with minimum interference with program execution. However, high volumes of trace data and the high cost of

trace modules limit visibility into the system operation to only short program segments that are often insufficient to locate software bugs. This dissertation introduces a new hardware/software technique for capturing and filtering read data value traces in multicores that enables a complete reconstruction of parallel program execution. The proposed technique called mcFiltrate (multicore cache filtered read data trace) utilizes tracking of data reads in data caches and cache coherence protocol states to minimize the number of trace messages that needs to be streamed out of the target platform to the software debugger. The effectiveness of the proposed technique is determined by analyzing the required trace port bandwidth and trace buffer sizes as a function of the data cache size and the number of processor cores. The experimental environment utilizes architectural execution-driven simulator running benchmarks from two suites, Splash2 and Parsec. The results of the experimental evaluation show that the proposed technique significantly reduces the required trace port bandwidth, from 12.2 to 59.6 for a single core processor and from 13.4 to 73.9 times for an octa core processor, when compared to the state-of-the-art Nexus-like read data value tracing. The proposed technique reduces the requirements for the on-chip trace buffers by several orders of magnitude and the number of required trace port pins by up to 16 times when compared to the state-of-the-art Nexus-like tracing. Consequently, mcFiltrate enables continuous on-the-fly data tracing while requiring modest changes on the hardware platform and the software debugger.

Abstract Approval: Committee Chair

(Dr. Aleksandar Milenkovic)

Department Chair

(Dr. Ravi Gorur)

Graduate Dean

(Dr. David Berkowitz)

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my deepest gratitude to my advisor, Dr. Aleksandar Milenkovic. I would not be in this position without his continuous support, guidance, and encouragement. He always inspired me with his patience even in the very odd times. He has shared profound knowledge with me since I started working with him. I feel lucky to work with a professor like him who can understand the educational background and personality of the student from different countries and guide them accordingly. I sincerely hope to be like him professionally and personally in my future and continue to collaborate with him.

I would like to thank Dr. Rhonda Gaede, Dr. Mohammad Haider, Dr. Tauhidur Rahman, and Dr. Earl Wells for serving on my committee. I would like to thank Dr. Ravi Gorur, Chair of the Electrical and Computer Engineering Department, for supporting me financially with a teaching assistantship. I would like to thank teaching and non-teaching staff members for teaching me valuable skills and helping whenever required during my time at the University of Alabama in Huntsville.

Also, I would like to thank Mr. Igor Semenov, Mr. Prawar Poudel, and Mr. Ranjan Hebbar for sharing their knowledge and answering questions whenever I ask them without judging the level of the question. I would like to thank Mr. Amrish K. Tewar who always inspires and teaches me new things whenever I approach him.

Finally, I would like to thank Mr. Srinivas R. Mynampally and his family for taking care of me since my arrival to the USA. I would like to express my deepest gratitude to my parents, Bhagavanth R. Ponugoti and Vimala Ponugoti, and my husband, Vamshi K. Vanapally, for their unconditional love and support.

# TABLE OF CONTENTS

|           | P                                                        | age |

|-----------|----------------------------------------------------------|-----|

| LIST OF F | FIGURES                                                  | ix  |

| LIST OF T | TABLES                                                   | xv  |

| CHAPTER   | R 1 INTRODUCTION                                         | 16  |

| 1.1 M     | lotivation                                               | 19  |

| 1.2 	 m   | acFiltrate: Multicore Cache-Filtered Read Data Trace     | 20  |

| 1.3 M     | Iain Contributions                                       | 21  |

| 1.4 D     | issertation Outline                                      | 23  |

| CHAPTER   | R 2 BACKGROUND AND MOTIVATION                            | 24  |

| 2.1 So    | oftware Tracing                                          | 25  |

| 2.1.1     | Software Tracing Frameworks                              | 27  |

| 2.2 H     | ardware Tracing                                          | 32  |

| 2.2.1     | Types of Hardware Tracing                                | 32  |

| 2.2.2     | Trace and Debug Infrastructure                           | 34  |

| 2.3 St    | tate-of-the-art Commercial Hardware Trace Solutions      | 37  |

| 2.4 M     | Iotivation                                               | 43  |

| 2.4.1     | Memory Read Data Value Tracing to Detect Race Conditions | 43  |

| 2.4.2     | Memory Read Data Value Tracing Challenges                | 46  |

| CHAPTER   | R 3 RELATED WORK                                         | 51  |

| 2.1 D     | agord and Ponlay                                         | 59  |

| 3.2   | Tra | ace Compression                                       | 53  |

|-------|-----|-------------------------------------------------------|-----|

| 3.    | 2.1 | Software Trace Compression                            | 53  |

| 3.    | 2.2 | Hardware Trace Compression                            | 56  |

| CHAP' | TER | 4 PROPOSED TECHNIQUE: mcFiltrate                      | 59  |

| 4.1   | Sys | stem View of mcFiltrate                               | 59  |

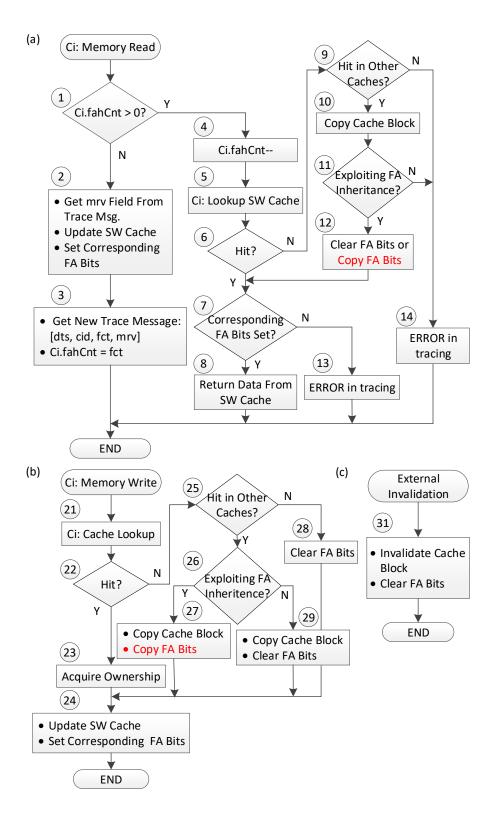

| 4.2   | mc  | Filtrate Operation on Target Platform                 | 62  |

| 4.3   | mc  | Filtrate Operation on the Software Debugger           | 68  |

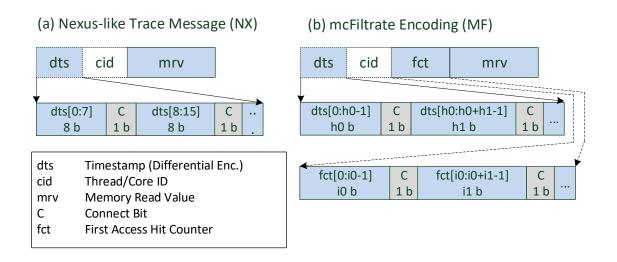

| 4.4   | En  | coding of Trace Messages                              | 71  |

| 4.5   | An  | Illustrative Example                                  | 73  |

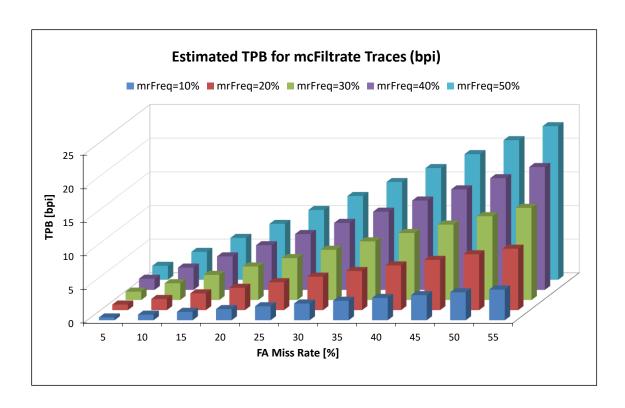

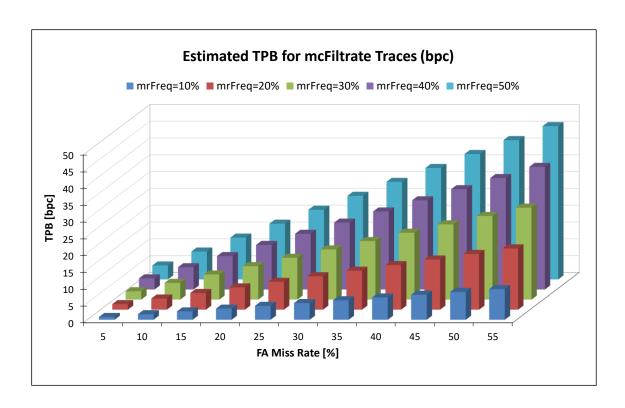

| 4.6   | mc  | Filtrate Analytical Model                             | 77  |

| CHAP' | TER | 5 EXPERIMENTAL ENVIRONMENT                            | 81  |

| 5.1   | Me  | etrics                                                | 81  |

| 5.2   | Ex  | perimental Flow                                       | 82  |

| 5.3   | Bei | nchmarks                                              | 85  |

| 5.4   | Ex  | perimental Parameters                                 | 90  |

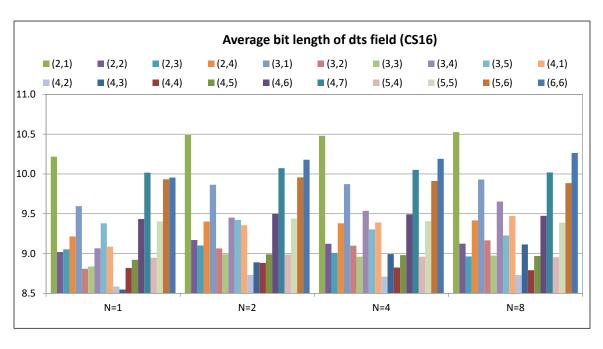

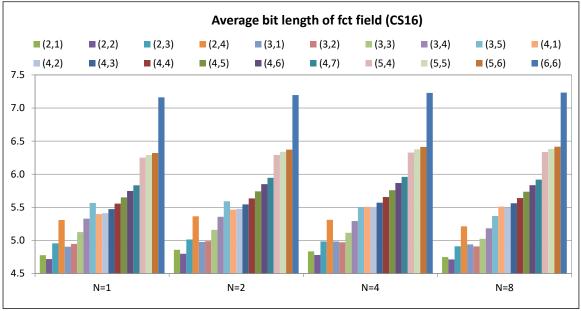

| 5.    | 4.1 | Impact of Granularity Size on Trace Port Bandwidth    | 90  |

| 5.    | 4.2 | Impact of Encoding Parameters on Trace Port Bandwidth | 92  |

| CHAP' | TER | 6 RESULTS                                             | 95  |

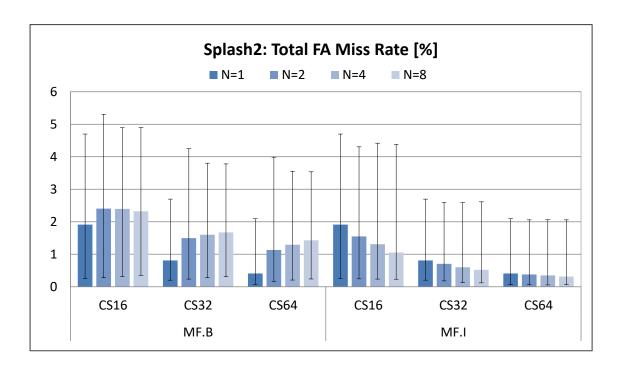

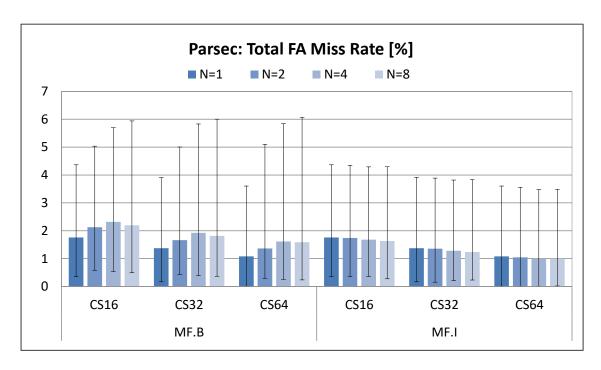

| 6.1   | Fir | rst-access Miss Rate                                  | 95  |

| 6.2   | Tra | ace Port Bandwidth in BPI                             | 100 |

| 6.3   | Tra | ace Port Bandwidth in BPC                             | 110 |

| 6.4   | Dynamic Trace Port Bandwidth Analysis            | 112 |

|-------|--------------------------------------------------|-----|

| 6.5   | Trace Buffer Size Analysis                       | 116 |

| 6.6   | Hardware Complexity Analysis                     | 122 |

| СНАРТ | ER 7 DICTIONARY ANALYSIS                         | 125 |

| 7.1   | Preliminaries                                    | 125 |

| 7.2   | Operation of <i>mcFiltrate</i> with Dictionaries | 129 |

| 7.3   | Experimental Evaluation                          | 133 |

| 7.4   | Results                                          | 134 |

| 7.4   | 1.1 Nexus-like (NX)                              | 134 |

| 7.4   | 1.2 mcFiltrate                                   | 139 |

| СНАРТ | ER 8 CONCLUSIONS AND FUTURE WORK                 | 143 |

| APEND | DIX A                                            | 146 |

| A.1   | Trace Port Bandwidth in BPI                      | 147 |

| A.:   | 1.1 Granularity Size is 4 (G=4)                  | 147 |

| A.:   | 1.2 Granularity Size is 32 (G=32)                | 148 |

| A.2   | Trace Port Bandwidth in BPC                      | 151 |

| A.2   | 2.1 Granularity Size is 4 (G=4)                  | 151 |

| A.2   | 2.2 Granularity Size is 32 (G=32)                | 154 |

| A.3   | Compression Ratio with Dictionaries              | 157 |

| аттая | FNCES                                            | 150 |

# LIST OF FIGURES

| Figure                                                                             |

|------------------------------------------------------------------------------------|

| Figure 2.1 Multicore SoC with Trace and Debug Infrastructure                       |

| Figure 2.2 Memory Read Data Value Tracing Example                                  |

| Figure 2.3 Estimation of Required Average TPB in bpi for Nexus-like Memory Read    |

| Data Value Traces                                                                  |

| Figure 2.4 Estimation of Required Average TPB in bpc for Nexus like Memory Read    |

| Data Value Traces                                                                  |

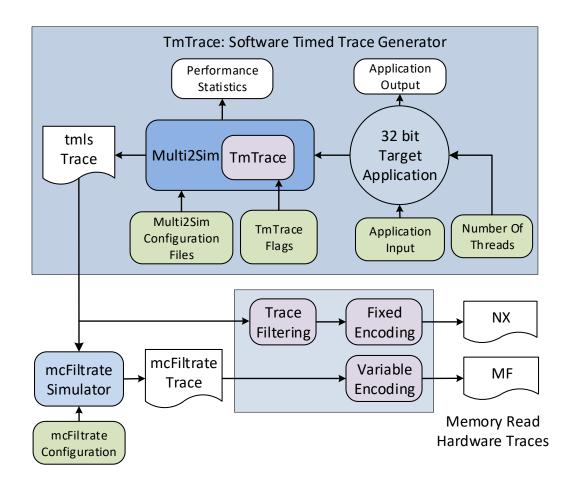

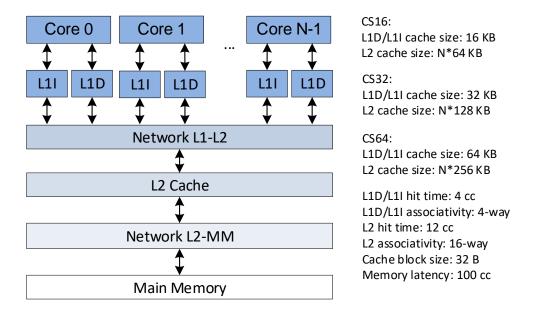

| Figure 4.1 System View of mcFiltrate61                                             |

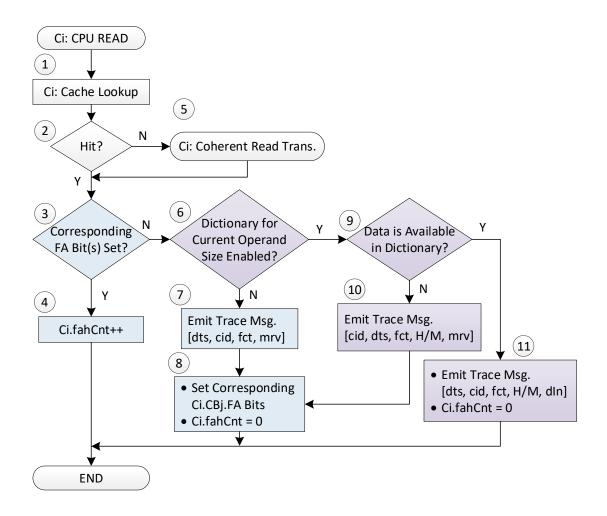

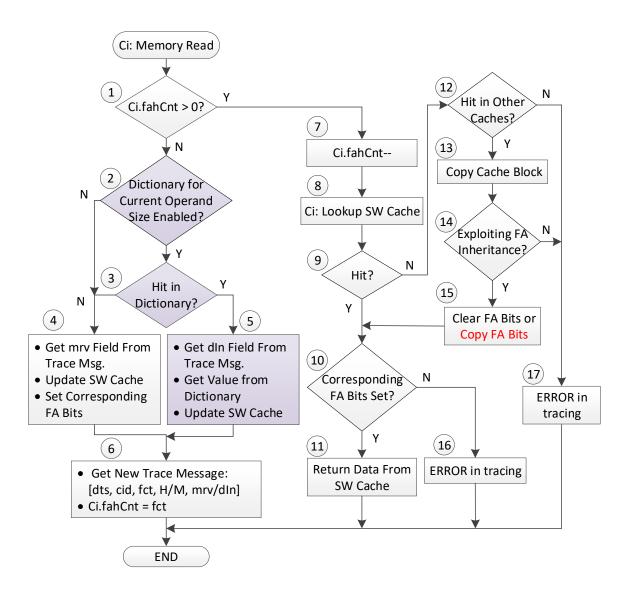

| Figure 4.2 $mcFiltrate$ Operation on Target Platform Core $i$ for a Memory Read64  |

| Figure 4.3 $mcFiltrate$ Operation on Target Platform Core $i$ for a Memory Write67 |

| Figure 4.4 mcFiltrate Operation on Software Debugger (a) a Memory Read (b) a       |

| Memory Write (c) an External Invalidation                                          |

| Figure 4.5 Encoding of Trace Messages                                              |

| Figure 4.6 An Illustrative Example of Data Tracing with <i>mcFiltrate</i> 76       |

| Figure 4.7 Estimation of Required Average TPB in bpi for $mcFiltrate$ when N=879   |

| Figure 4.8 Estimation of Required Average TPB in bpc for $mcFiltrate$ when N=880   |

| Figure 5.1 Experimental Environment                                                |

| Figure 5.2 Multicore Model                                                         |

| Figure 5.3 Encoding Parameter Selection for Splash2 with MF.I and CS1694           |

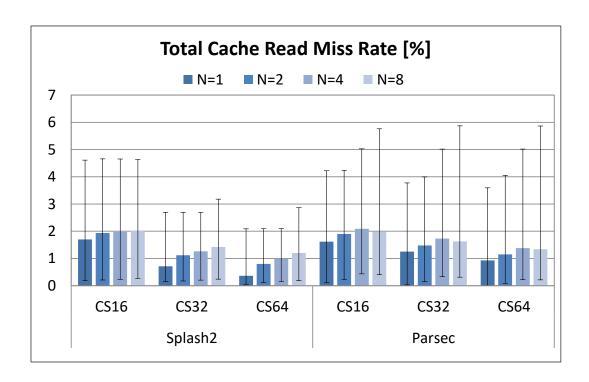

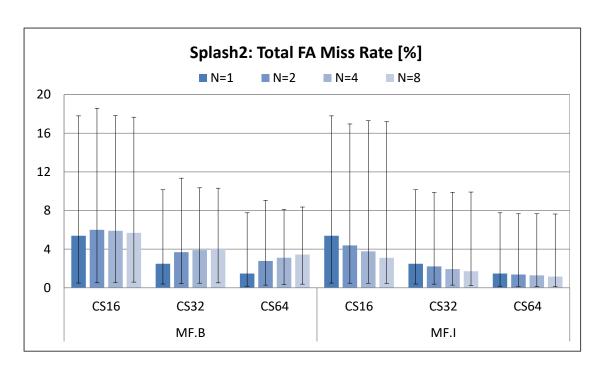

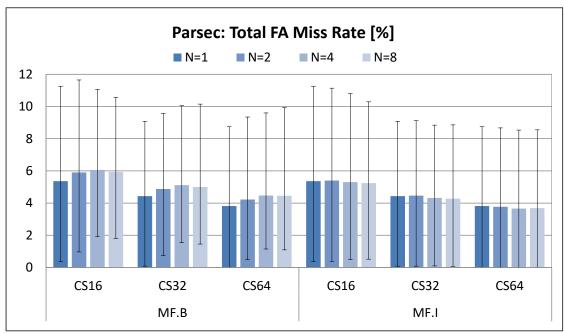

| Figure 6.1 Total L1 Data Cache Read Miss Rate                                      |

| Figure 6.2 Total First-access Miss Rate of Splash2 (top) and Parsec (bottom)99     |

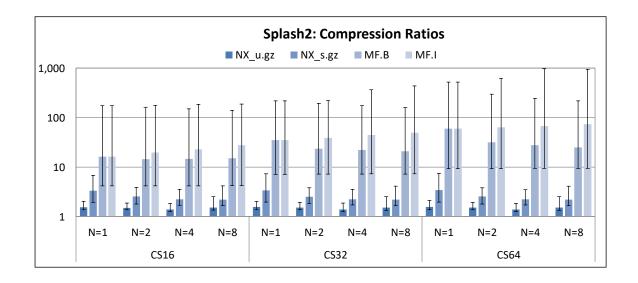

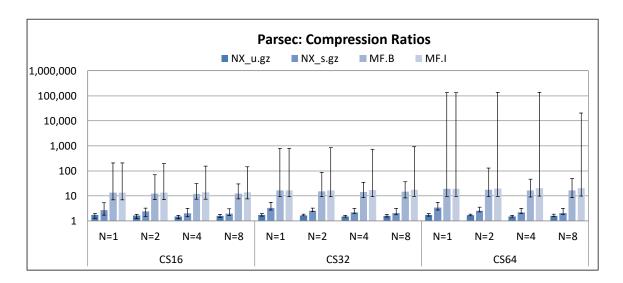

| Figure 6.3 Compression Ratios of Splash2 (top) and Parsec (bottom)                 |

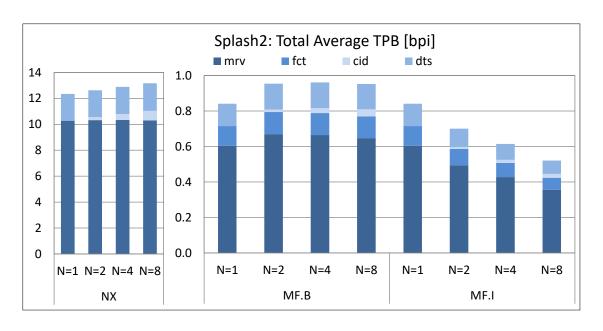

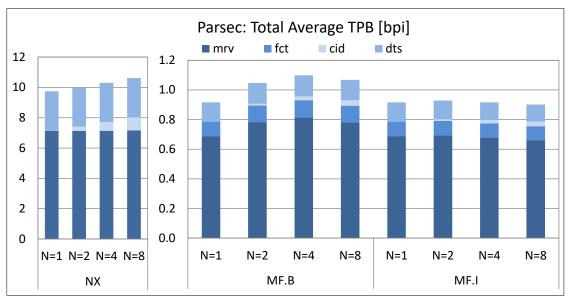

| Figure 6.4 Break down of TPB in bpi for Splash2 (top) and Parsec (bottom) for CS64 |

|------------------------------------------------------------------------------------|

|                                                                                    |

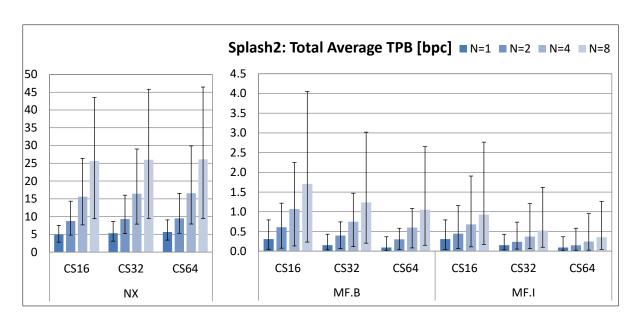

| Figure 6.5 Trace Port Bandwidth in bpc for Splash2 (top) and Parsec (bottom)112    |

| Figure 6.6 Dynamic TPB in bpc for Characteristic Benchmarks                        |

| Figure 6.7 On-chip Trace Buffer Size for Splash2 (top) and Parsec (bottom) for NX  |

|                                                                                    |

| Figure 6.8 On-chip Trace Buffer Size in KB for Splash2120                          |

| Figure 6.9 On-chip Trace Buffer Size in KB for Parsec                              |

| Figure 7.1 System View of a Dictionary-Based Trace Compressor                      |

| Figure 7.2 Format of Trace Messages Supporting Dictionaries                        |

| Figure 7.3 $mcFiltrate$ Operation with Dictionary on Target Platform Core $i$ for  |

| Memory Read                                                                        |

| Figure 7.4 mcFiltrate Operation with Dictionary on Software Debugger for Memory    |

| Reads                                                                              |

| Figure. A.1 Total First-access Miss Rate of Splash2 (top) and Parsec (bottom) with |

| G=32146                                                                            |

# LIST OF TABLES

| Table                                                                       | Page     |

|-----------------------------------------------------------------------------|----------|

| Table 5.1 Benchmark Characteristics for Splash2                             | 86       |

| Table 5.2 Benchmark Characteristics for Parsec                              | 87       |

| Table 5.3 Distribution of Memory Read Operands in Splash2                   | 89       |

| Table 5.4 Distribution of Memory Read Operands in Parsec                    | 89       |

| Table 5.5 TPB for MF.I with CS64, N=8 as a Function of Granularity          | Size for |

| Splash2                                                                     | 91       |

| Table 5.6 TPB for MF.I with CS64, N=8 as a Function of Granularity Size for | r Parsec |

|                                                                             | 92       |

| Table 5.7 Encoding Parameters                                               | 93       |

| Table 6.1 Average TPB in bpi for Splash2 with CS16                          | 101      |

| Table 6.2 Average TPB in bpi for Splash2 with CS64                          | 102      |

| Table 6.3 Average TPB in bpi for Parsec with CS16                           | 103      |

| Table 6.4 Average TPB in bpi for Parsec with CS64                           | 104      |

| Table 6.5 Compression Ratios for Splash2 with CS64                          | 107      |

| Table 6.6 Compression Ratios for Parsec with CS64                           | 108      |

| Table 6.7 Hardware Complexity Estimation                                    | 124      |

| Table 7.1 Hybrid Dictionary Data Header Encoding (Method 1): An Example     | 129      |

| Table 7.2 Hybrid Dictionary Data Header Encoding (Method 2): An Example     | 129      |

| Table 7.3 Compression Ratio for Splash2 with Static Dictionary (DS=256)     | for NX   |

| (CS64)                                                                      | 136      |

| Table 7.4 Compression Ratio of Splash2 with Dynamic Dictionary (DS=256)     | for NX   |

| (CS64)                                                                      | 137      |

| Table 7.5 Compression Ratio of Parsec with Static Dictionary (DS=   | =128) for NX  |

|---------------------------------------------------------------------|---------------|

| (CS64)                                                              | 138           |

| Table 7.6 Compression Ratio of Parsec with Dynamic Dictionary (DS   | =256) for NX  |

| (CS64)                                                              | 139           |

| Table 7.7 Compression Ratio of Splash2 with Static Dictionary (DS=2 | 256) for MF.I |

| (CS64)                                                              | 140           |

| Table 7.8 Compression Ratio of Splash2 with Dynamic Dictionary (DS= | 256) for MF.I |

| (CS64)                                                              | 141           |

| Table 7.9 Compression Ratio of Parsec with Static Dictionary (DS=2  | 256) for MF.I |

| (CS64)                                                              | 141           |

| Table 7.10 Compression Ratio of Parsec with Dynamic Dictionary (DS= | 256) for MF.I |

| (CS64)                                                              | 142           |

| Table. A.1 Average TPB in bpi for Splash2 with CS32 (G=4)           | 147           |

| Table. A.2 Average TPB in bpi for Parsec with CS32 (G=4)            | 147           |

| Table. A.3 Average TPB in bpi for Splash2 with CS16 (G=32)          | 148           |

| Table. A.4 Average TPB in bpi for Splash2 with CS32 (G=32)          | 148           |

| Table. A.5 Average TPB in bpi for Splash2 with CS64 (G=32)          | 149           |

| Table. A.6 Average TPB in bpi for Parsec with CS16 (G=32)           | 149           |

| Table. A.7 Average TPB in bpi for Parsec with CS32 (G=32)           | 150           |

| Table. A.8 Average TPB in bpi for Parsec with CS64 (G=32)           | 150           |

| Table. A.9 Average TPB in bpc for Splash2 with CS16 (G=4)           | 151           |

| Table. A.10 Average TPB in bpc for Splash2 with CS32 (G=4)          | 152           |

| Table. A.11 Average TPB in bpc for Splash2 with CS64 (G=4)          | 152           |

| Table. A.12 Average TPB in bpc for Parsec with CS16 (G=4)           | 153           |

| Table, A.13 Average TPB in bpc for Parsec with CS32 (G=4)           | 153           |

| Table. A.14 Average TPB in bpc for Parsec with CS64 (G=4)                       |

|---------------------------------------------------------------------------------|

| Table. A.15 Average TPB in bpc for Splash2 with CS16 (G=32)                     |

| Table. A.16 Average TPB in bpc for Splash2 with CS32 (G=32)                     |

| Table. A.17 Average TPB in bpc for Splash2 with CS64 (G=32)                     |

| Table. A.18 Average TPB in bpc for Parsec with CS16 (G=32)                      |

| Table. A.19 Average TPB in bpc for Parsec with CS32 (G=32)                      |

| Table. A.20 Average TPB in bpc for Parsec with CS64 (G=32)                      |

| Table. A.21 Compression Ratio of Splash2 with DS=256 and DES = 4 and 8 for MF.I |

| (CS64)                                                                          |

| Table. A.22 Compression Ratio of Parsec with DS=256 and DES = 4 and 8 for MF.I  |

| (CS64)                                                                          |

# CHAPTER 1

#### INTRODUCTION

Embedded systems are computer systems designed to meet the computational requirements of a specific task. They are typically a part of a bigger cyber-physical system, embedded in the environment they operate in, sensing the environment, processing the information, storing information, communicating with other systems, and acting upon the environment. Energy efficiency, low cost, and small form factors are often primary design constraints for embedded systems. They range from lowend to high-end and are found in many application domains, such as medical, transportation, military, industrial, and consumer applications.

Every product has a time window to launch in the market. If the product misses that crucial time window, the sales targets may be missed, resulting in financial losses and missed opportunities. Thus, it is extremely important to reduce the cost and time-to-market, while meeting or exceeding user expectations. To meet the growing performance requirements while maintaining the energy efficiency, hardware designers are incorporating complex hardware structures with multiple processor cores, on-chip interconnect, hardware accelerators, memory controllers, and a range of input/output interfaces on a single chip. As a result, the complexity of modern systems-on-a-chip is increasing, which in turn results in diminished visibility of the system internals.

At the same time, software complexity is also growing rapidly to support higher levels of functionality to meet user expectations and win market share. For example, today's high-end cars include many functions which were not possible a decade ago. To achieve this, they may run over 100 million lines of code [1]. As we move toward autonomous cars, the code size will continue to increase. Due to shorter development cycles, companies are failing to test the software rigorously to provide reliable software. A recent study shows that recalls in medical devices [2] [3] and automotive devices [4] [5] [6] are mainly due to software bugs. Frequent recalls of products to fix software bugs often hurt companies' reputations, customer trust, and stocks revenue in the long term. Software bugs in cyber-physical systems are even more challenging as they may lead to significant damage and even loss of life [7].

A study from the Judge Business School at the University of Cambridge [8] shows that software developers spend 50% of their development time finding and fixing software bugs, incurring costs of around \$312 billion per year. These costs are likely to increase further due to growing system complexity. In addition, more than 80% of development costs in modern embedded systems come from software engineering [9]. With the increased complexity of hardware and software, challenges and costs incurred by software debugging are continually increasing. The current market conditions and trends make it impossible to redesign the development cycles to accommodate additional time for software testing to deliver bug-free software. Hence, it is imperative to provide better tools for software developers to use to locate bugs in the software quickly and cheaply.

The most common debugging techniques include printf debugging, software tracing, and run-control debugging. Printf debugging adds temporary printf statements to track the flow and values used in sections of code under debug. This technique is effective at finding software bugs related to algorithms. However, it is a time-consuming process and that is not feasible when the source code reaches mil-

lions of instructions. Moreover, it is inefficient for finding problems related to time sensitivity, memory allocation, and interrupts. Additionally, outputting the data to a host computer over any communication port can be slow and may impact the behavior of the program. All these reasons make printf debugging not suitable for real-time embedded systems.

Tracing is a method of recording the details of the program as it executes. In software tracing, static and/or dynamic binary and/or source code instrumentation is used to monitor events of interest at the application and/or kernel level. The recorded trace data is either stored in the system memory or streamed through a communication port to the host. The traces are later used for debugging, validation, performance analysis, and performance optimization. Popular examples of software tracing tools include Ftrace [10], Dtrace [11], LTTng [12], eBPF [13], Systemtap [14], WPP [15], Pin [16], among others. Ideally, software tracing can be used in any system as it does not require an external trace debugger. However, instrumentation may affect the performance and/or execution flow of the system/program under inspection. Moreover, these methods are unavailable or ineffective in helping the developers to pinpoint hard-to-find software bugs on resource constrained platforms.

Run-control debugging gives better control over processor execution and is widely used by embedded software developers. In this type of debugging, developers can get control over the program to run step by step, to set watch points or break points, to change, or to observe the content of registers and memory locations when the processor is halted. However, run-control debugging is not practical in many real-time applications – e.g., engine controls, hard disks, robotics, avionics, and automotive, or any application where the processor must run continuously to maintain mechanical stability. First, the sequence of events on the target platform may

change due to run-control debugging, and in the case of multicores, it may not be practical to halt all the processors at the same time. Second, the problems related to external events which are caused when the system is running at full speed cannot be identified. Finally, there is no support to examine the history of the program and thus visibility into the system is either limited or absent when the application is executing. Because of the dependence on external peripherals and the lack of bug reproducibility, run-control debugging is insufficient for real-time embedded systems.

To address this problem, modern processors and systems-on-a-chip (SoCs) include dedicated hardware resources to support hardware tracing and debugging. In hardware tracing, a processor discloses the detailed and accurate internal information at the instruction level granularity with minimal or no performance degradation.

#### 1.1 Motivation

The most common types of hardware traces that can be collected from a processor are control-flow and data-flow. A control-flow trace records the execution path of the program and helps developers understand how the program reached a certain point in execution. It captures information related to branches, subroutine calls, returns, and exceptions. A data-flow trace captures the address and/or value of every memory read and write instruction. Data-flow traces enable developers to replay the program offline and locate bugs in the program under test.

Existing trace modules produce several MB of trace data in a second and they require an average trace port bandwidth of ~0.3 bits per instruction executed for control-flow tracing [17], and 8-16 bits per instruction executed for data-flow tracing for a single core [18]. Since the transfer rate of trace data off-chip is slower than the

rate at which the trace data is produced by the processor, dedicated on-chip trace buffers are used to temporarily hold the trace data. A 2 KB dedicated on-chip trace buffer can hold control-flow traces for about 54 kilo instructions and data-flow traces for about 2 kilo instructions on a single core. In the case of multicores, the buffer space is shared among cores, plus additional bits are required to report the core id. Thus, existing commercial trace modules allow the user to set filters to capture data-flow traces for only a limited range of addresses or instructions. Unfortunately, the traces captured in trace buffers on limited program segments may not be sufficient to locate bugs as a software bug origin and its manifestation may span millions of instructions. To capture data-flow traces for an entire program, it is required either to halt the program when the trace buffer is full or use deep on-chip trace buffers or wider trace ports (i.e. dedicated physical pins) to empty the trace data faster. However, these options are not attractive since deep on-chip trace buffers or wider trace ports increase the system cost for the end user and halting the processor in real-time systems is not feasible.

# 1.2 *mcFiltrate*: Multicore Cache-Filtered Read Data Trace

This dissertation introduces and evaluates mcFiltrate, a new technique for capturing and filtering read data value traces in multicores. mcFiltrate stands for multicore filtered memory read data trace. This technique captures and filters the memory read data traces by using L1 data caches and first-access tracking bits on the target processor core. In addition, it requires the software debugger to maintain L1 data cache structures in software identical to those in the target core. The main goal of this technique is to filter out redundant trace messages that can be inferred by the software debugger. The first-access tracking bits associated with sub-blocks of

an L1 data cache block (or line) are used to determine whether the trace data can be inferred by the software debugger. In addition, *mcFiltrate* can exploit cache coherence protocols to minimize the number of redundant trace messages for cache blocks that are actively shared by multiple processor cores.

This dissertation experimentally evaluates the effectiveness of mcFiltrate relative to the state-of-the-art Nexus-like data tracing as a function of the number of cores and cache configurations. As metrics of interest, the average and dynamic required trace port bandwidth measured in bits per instruction executed (bpi) and bits per processor clock cycle (bpc) are used. In addition, the worst-case analysis concerning the maximum depth of the trace buffer as a function of trace port emptying rate is performed. The results show that mcFiltrate offers a significant reduction in the required trace port bandwidth relative to the existing Nexus-like memory read data value tracing. It reduces the trace port bandwidth in the range of 13.4 to 59.6 times for a single core processor, and from 12.2 to 73.8 times for an octa core processor, depending on the size of data caches.

# 1.3 Main Contributions

The main contributions of this dissertation are as follows:

• It characterizes trace port bandwidth requirements in bits per instruction and bits per clock cycle in multicores for Nexus-like timestamped read data value traces. The results demonstrate that this type of tracing is practical for only very short program segments and that it becomes cost-prohibitive in both required trace port bandwidth and the number of dedicated trace port pins as program size increases.

- It introduces a hardware/software technique called *mcFiltrate* to capture and compress memory read data value traces in multicores. This technique relies on first-access tracking bits attached to L1 data cache blocks and cache coherence protocol states to determine when memory reads need to be traced out to ensure that the program is replayed offline faithfully. This technique is an extension of previous research [19][20][21].

- It experimentally evaluates the trace port bandwidth required by *mcFiltrate*, while varying the number of processor cores and data cache sizes, when running parallel benchmarks from Splash2 [22] and Parsec suites [23].

- In addition to analyzing the average required trace port bandwidth, dynamic changes in the trace port bandwidth requirements during benchmarks' execution are evaluated. Moreover, a detailed analysis is performed to determine the maximum required size of the trace buffers needed for on-the-fly tracing while varying the actual trace port bandwidth.

- To further reduce the required trace port bandwidth, a dictionary-based compression technique for Nexus-like and *mcFiltrate* traces is proposed. The results of the experimental evaluation show that even though overall trace compression achieved with dictionaries are modest, some individual benchmarks benefit significantly.

#### 1.4 Dissertation Outline

The remaining of the dissertation is organized as follows: CHAPTER 2 briefly discusses various software and hardware tracing techniques. It describes the challenges in data tracing using an analytical model. CHAPTER 3 reviews the literature and state-of-the-art solutions for compressing trace data. CHAPTER 4 introduces mcFiltrate and details its operation on a target core and on the software debugger side. CHAPTER 5 discusses the experimental environment used in the evaluation and CHAPTER 6 discusses the results from the experimental evaluation. CHAPTER 7 discusses the dictionary analysis which can be used to further reduce the trace port bandwidth requirements and CHAPTER 8 summarizes this work.

#### CHAPTER 2

#### BACKGROUND AND MOTIVATION

Tracing can be treated as a slow-motion video of the real-time program execution. It involves recording program details that can be used for debugging, performance analysis, performance optimization, or security analysis. Depending on how these traces are recorded, two types of tracing exist: (a) software tracing, where software is responsible for capturing and handling traces; and (b) hardware tracing, where dedicated hardware resources are responsible for capturing traces.

In software tracing, the operating system and/or user application programs are instrumented statically and/or dynamically with code to capture and record traces. With instrumentation, any instruction can be trapped to collect the required information. Depending on the configuration, a typical software trace can record various details such as current process identifier (pid), call arguments, stack trace, time, return value of system calls, register values, instruction addresses, and other data. More details about software tracing and the most widely used software tracing facilities at kernel level and application level are discussed in Section 2.1.

In hardware tracing, a processor gives the complete history of the executed instructions with minimal or no overhead. Ideally, the real-time behavior of the program is not affected by the tracing operation. Depending on the level of support and required type of trace, a processor can record various details such as time, processor/thread identifier, instruction addresses, memory values and memory addresses in the case of memory accessing instructions, and other information for executed instructions. Section 2.2 describes hardware tracing and introduces terminology used

throughout the dissertation. Section 2.3 discusses existing commercial hardware tracing solutions. Finally, Section 2.4 discusses how hardware traces can be used in debugging and why it is important to filter and/or compress hardware data traces.

# 2.1 Software Tracing

In software tracing, the operating system, a program under debug by itself, or an observer program records the trace data. To record the traces, instrumentation of the source code or binary of the operating system and/or user application program is required. Depending on when the instrumentation is performed, it can be classified into: (a) static instrumentation or (b) dynamic instrumentation. With static instrumentation, the kernel or a user application program includes the dedicated code which helps in recording the traces when enabled. With dynamic instrumentation, instrumentation code is inserted or attached dynamically at runtime during the execution of the application.

A probe point is a debug statement that assists in collecting execution characteristics of a program; e.g. the state of the executing program is captured when the probe point is reached [24]. Probe points can be inserted and enabled statically and dynamically. With probe points, the kernel or a user application program is instrumented with code and this instrumentation code is run when the specified probe point is executed by the processor, i.e. when the probe is fired. However, there are other user space dynamic binary instrumentation frameworks where application binary is modified on-the-fly and modified code is executed to capture the details of the execution [16] [25].

Static probe points are inserted by the kernel or application developer at important locations while writing the code. To enable or insert static probe points, e.g.,

inserting printh statements, recompilation of the source code is required. However, some static probe points can be enabled or disabled dynamically and a probe handler function can be attached to record the data. Dynamic probe points can be inserted at any address in the kernel and application code without the need for recompilation of the source code. In dynamic probing, a trap instruction is inserted at the desired locations. When the trap instruction is executed, the interrupt is generated and the corresponding handler for that probe is called. Once the handler is finished, the original code continues with normal execution. In dynamic probing the overhead for each instrumented site execution is larger than for static probing because of the trap mechanism. In Linux, tracepoints, kprobes, uprobes, and USDT probes are the main sources of collecting information. Static kernel space probe points are referred to as tracepoints and static user space probe points are referred to as USDT probes (User Statically Defined Tracing points). Kprobe and uprobe are dynamic methods of inserting probe points to any kernel space and user space code, respectively.

There are many open source tools and frameworks available to collect and analyze information from kernel and user application programs. Some of these frameworks support frontend tools to provide an interface (scripting or programming), to insert dynamic probe points, and to enable or disable some of the static probe points. They differ in the level of detail that they can capture, sources of information, and how they handle setting the probes, executing the probe handler, data collection, and frontend tool interface if the probe points are data sources (Section 2.1.1).

#### 2.1.1 Software Tracing Frameworks

Ptrace. Ptrace, process trace, is a system call in Unix and Unix-like operating systems that enables one process (controller process, parent) to observe or control the execution of another process (target process) [26]. It can be attached or detached from the process being traced at any time. With ptrace, the ability of the control process to change registers and memory of the target process allows it to set breakpoints, run step-by-step, and inject code to a running target process. The controller process can observe and intercept the system calls and signals to and from the target. Thus, ptrace is used by debuggers – gdb and dbx, tracing tools – strace and ltrace, and by code coverage tools. Since the communication between the control process and the target process requires at least two context switches, the performance overhead of ptrace is significant. It is supported by OpenBSD, FreeBSD, NetBSD, IBM AIX, and Linux.

Strace. Strace, system call tracer, is a lightweight diagnostic, debugging and instructional user space utility for Linux to trace the interactions of a program with the operating system [27]. Strace uses the ptrace system call to register itself as a control process (tracer). It is notified of all the system calls and signals and can get the details such as, the type of a system call, arguments passed, stack of the target process, return value, and the time spent in the system call. This is quite useful when debugging the programs where source code is not available.

Ltrace. Ltrace, library call tracer, is used to trace calls and returns from a dynamic library function executed by the target process [28]. In addition, it can also trace system calls and signals like strace. Ltrace uses ptrace to place the breakpoints by hooking into the procedure linkable table (PLT). It is supported by Linux.

Ftrace. Ftrace, function tracer, is a tracing framework built into the Linux kernel to understand the internals of the kernel [10]. This utility can be used in debugging and to analyze latencies and performance issues which come from kernel space. Although the name of the tracer is function call tracer, the framework includes several tracing utilities. With the hundreds of available tracepoints (static events) that can be enabled via the tracefs file system in the kernel, ftrace can trace scheduling events, interrupts, virtual guest connections with host, and file systems. More elaborately, it can disclose the information to answer the questions such as what happens when the interrupts are disabled and enabled and when is the task actually scheduled after waking up. The dynamic ftrace can trace any functions of the kernel and it also allows the filtering of functions by using globs. It can generate call graphs and provide stack usage reports. It can consume tracepoints, kprobes, and uprobes trace sources.

LTTng. LTTng, Linux Trace Toolkit Next Generation, is a set of LTTng-tools, LTTng-UST, and LTTng-modules tools [12]. These tools can be used to instrument the Linux kernel (LTTng-modules, includes the modules to instrument and trace the Linux kernel), user applications (LTTng-UST), and to trace control e.g., starting and stopping of the tracing and enabling and disabling of event rules. The optimized events in LTTng have low overhead compared to existing trace solutions and can be used to analyze the scheduling decisions, context switches, execution of various background tasks, actual execution time of the process and blocked time. It is supported by Linux and FreeBSD.

**Dtrace.** DTrace, Dynamic tracing, was developed by Sun Microsystems to examine the behavior of applications and the kernel on production systems in real-

time [11]. DTrace can be configured to record the additional data like function arguments, stack trace, and other data whenever the probe of interest is fired. The probes used by DTrace are not defined by the tool itself, rather, they come from the kernel modules called providers. Each provider is independent and reports the list of data points (set of probes) that it can instrument. All the instrumentation in DTrace is dynamic, i.e. the probes are enabled only when they are utilized – there is no overhead when they are disabled, and no instrumentation code is added for the inactive probes. D language (inspired by C and awk) is used to write the scripts which include the list of probes to enable and the associated action of the probe, probe handler. The scripts are converted to a simplified instruction set, Dynamic Intermediate Format (DIF), by using the compiler which is in libdtrace library and they are interpreted by the virtual machine at the kernel level when the probe fires. DTrace is supported on Solaris, Illumos, MacOS, FreeBSD, NetBSD, Oracle Linux, and Microsoft Windows.

eBPF. eBPF, extended Berkeley Packet Filter, is an in-kernel virtual machine native to Linux [13]. In the original BPF, network packets are captured and filtered by attaching a filter program which runs on a virtual machine to any socket. eBPF is enhanced over BPF to give better performance through an expanded set of registers, instructions, helper functions that can be called inside the programs. Additionally, global storage called eBPF maps allow sharing of data between eBPF kernel and user space programs and between eBPF kernel programs. The eBPF programs written in C are converted to bytecode and attached to the path of the execution, kprobes, uprobes, and tracepoints as in DTrace. The eBPF virtual machine per-

forms a sanity check to ensure security before executing the bytecode. With eBPF, applications can be traced with low overhead.

Sysdig. Sysdig is a high-performance system call tracer which also supports tracing of containerized processes [29]. Instrumentation is done by using a device driver as an external kernel module, sysdig\_probe. Sysdig uses static tracepoints to intercept system calls and does not support kprobes, uprobes, and USDT. However, a newer version of sysdig incorporates support for using eBPF for event collection as a backend instead of a kernel module. In addition to tracing, Sysdig includes many diagnostic tools such as tcpdump, strace, fuser, lsof, iostat, htop, lspci, ethool, and netstat.

SystemTap. SystemTap is a tool for dynamically instrumenting a Linux kernel based operating systems to monitor the kernel [14]. The scripts are written in the SystemTap language; however, they are translated to C language to create a kernel module from it. SystemTap does not have in-kernel virtual machine; instead, kernel modules are loaded dynamically. When the event specified in the script occurs, the Linux kernel runs the corresponding handler as a quick sub-routine. Probes in the script are disabled when the SystemTap session expires. It can consume, kprobes, uprobes, kernel tracepoints, and USDT.

ETW. ETW, Event Tracing for Windows, is a tracing facility on the Windows operating system which allows logging the events of user applications and kernel device drivers [15]. The application which is to be traced should contain event tracing instrumentation. Even though ETW allows tracing to turn on or off dynamically, it does not have the ability to insert trace points at runtime. The events – metadata, localizable message strings, and schematized data payloads are logged to a separate

buffer for each processor stored on disk and/or delivered to the consumer in realtime.

**Pin.** Pin is a dynamic binary instrumentation framework that allows analysis of user space applications on Linux, Windows, and OS X [16]. It provides APIs to write instrumentation tools called *pintools* in C/C++ to profile or trace an application [25]. Pin APIs allows pintools to access architecture specific details and support IA-32, x86-64, and MIC instruction-set architectures. The injector loads the pin binary into the address space of an application by using the Unix Ptrace API and starts it running. Pin intercepts the execution of the application at the very first instruction and loads the pintool. Once the pintool initializes itself, it requests pin to start the application. Depending on the instrumentation APIs used in pintool, pin generates new instrumented code for one trace at a time using just-in-time (JIT) compiler by feeding actual executable as input. A trace is defined as a set of consecutive instructions which terminates at one of the conditions: (a) an unconditional control transfer (branch, call, or return), (b) a pre-defined number of conditional control transfers, or (c) a pre-defined number of instructions have been fetched in the trace. After generating new code, pin transfers control to the generated sequence and it make sure to regain the control when the branch exists the sequence. After regaining control, pin generates more code for the branch target and continues execution. To speed up the instrumentation, pin employs various optimization techniques such as code cache, trace linking, inlining, register re-allocation, liveness analysis, and instruction scheduling.

In software tracing, event tracing is most widely used since collecting traces for every instruction gives the greater performance overhead. Even though software tracing provides high flexibility to analyze and debug the applications and operating system, these methods are not suitable for real-time embedded system where very intrusive software modules for tracing interfere with normal program behavior. Adding instrumentation code may increase the footprint of the executable in memory, may affect cache access patterns, and is intrusive. Moreover, most of these frameworks cannot be used to debug the firmware and boot time issues because the necessary libraries are not initialized.

# 2.2 Hardware Tracing

Hardware traces provide a complete history of the instructions executed on a processor and are collected by dedicated hardware trace modules in modern processors. Thus, tracing a processor gives better visibility of the system at any given point than does software. The beauty of hardware tracing is that information is captured with zero or very low overhead as it uses dedicated hardware circuitry. However, hardware tracing produces vast amounts of data in a short period of time.

# 2.2.1 Types of Hardware Tracing

Depending on the type of information collected by the trace module, hard-ware tracing can be classified into two types, control-flow tracing and data-flow tracing. A control-flow trace records information related to control-flow instructions and a data-flow trace records information related to memory read and write instructions executed by a processor.

Control-Flow Tracing. A basic block is a portion of the program with a single entry and a single exit. Branch instructions transfer control from the exit of one basic block to the entry of another basic block. These are usually used to analyze

program behavior, for example, to find hot regions [30], in security (control-flow integrity), and by compilers (profile guided optimization).

Tracing each and every executed instruction to reconstruct the flow of the program is expensive as it produces a lot of trace data. In most cases, it is sufficient to record changes in the path of the program (basic block entries) to determine and reconstruct the actual execution. Hence, a control-flow trace involves recording traces for jumps, calls, returns, interrupts, and exceptions, while executing on the target processor. State-of-the-art commercial tracing solutions support capturing the control-flow traces of a program and compress the trace data by filtering the statically available data from the program binary, for example, direct unconditional branches.

Control-flow traces can be used in debugging a program to understand how it reached any given execution point or what path it took to arrive to the given execution point [31] [32]. These traces can also be useful to profile the instructions, detect latencies [33], perform path based optimizations, path sensitive prediction techniques such as branch prediction, to understand the behavior of the malware, and in security [34] [35] [36] [37] [38]. Additionally, these traces can be used to identify the isolating bugs while varying the input since the program behavior changes.

**Data-Flow Tracing.** Control-flow traces are helpful for uncovering various types of bugs. However, control-flow traces alone cannot help to uncover the problems related to memory accesses, such as data race conditions or memory access patterns in the case of multicores.

A data-flow trace records information about memory read and memory write instructions. A full data-flow trace records instruction address, addresses of memory read and memory write operation, size of operand, and value of memory read and write operation. However, depending on the intended use and tracing requirements,

a subset of these fields can be traced out. For example, the addresses of memory reads and writes are useful (a) to analyze cache performance, internal memory, and data transfer operations, (b) to identify data locality, which can help to find cache conscious data layouts, (c) to develop data prefetching techniques, and (d) to find data race conditions in multicores. The data values are significant in enabling faithful replay of the program offline. Replay of the program enables software developers to find bugs with minimal effort as they can move forward and backward in time. In addition, it is really important to know what data value a processor is reading at a given point of time in security (data integrity) [39] and to solve problems with external inputs in real-time systems. For example, in the case of a sensor malfunctioning, it is not possible to determine the cause for the crash without actually knowing the value it read [40].

# 2.2.2 Trace and Debug Infrastructure

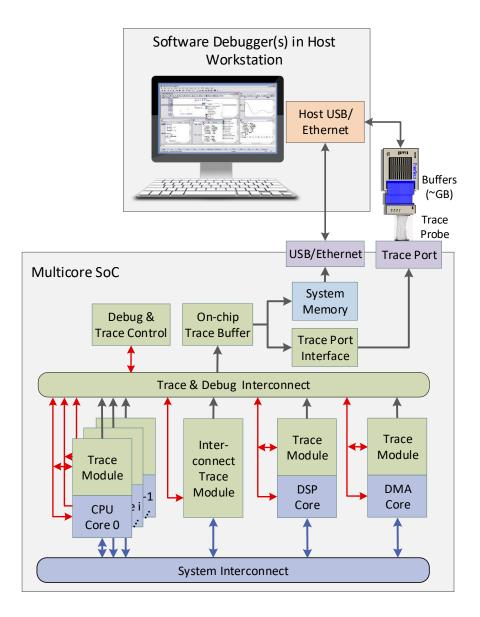

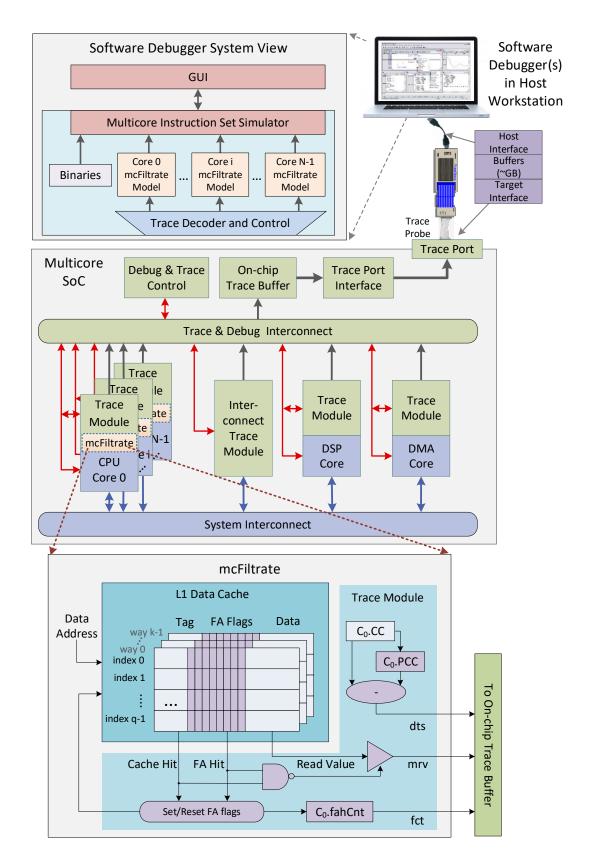

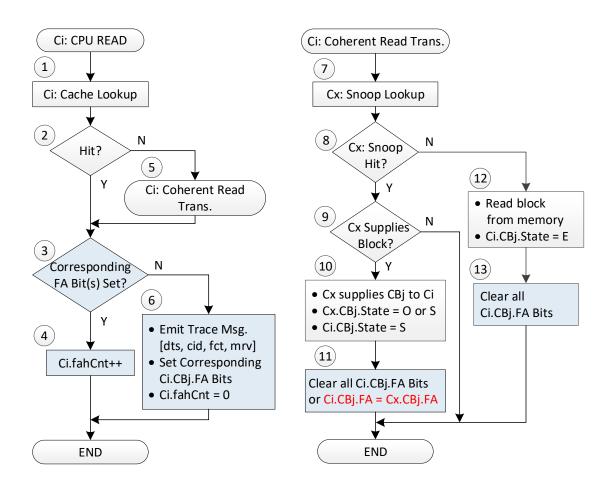

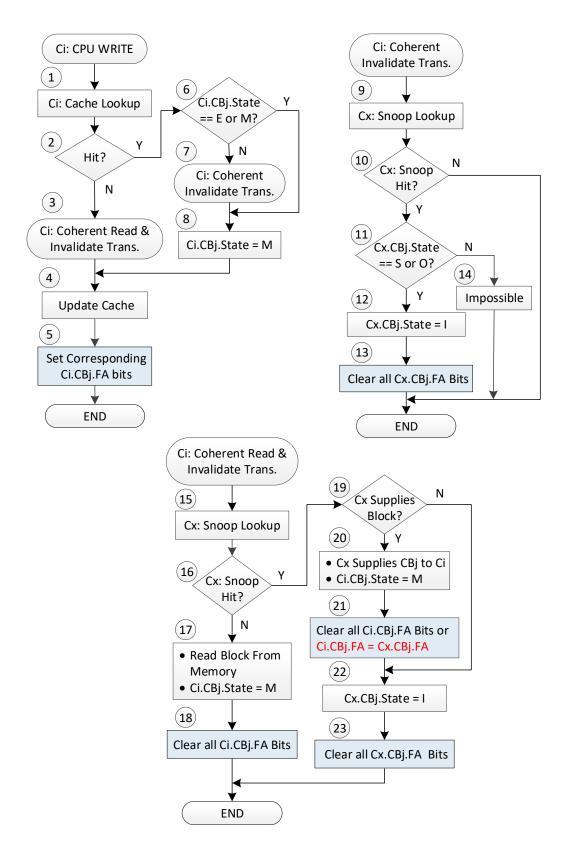

Figure 2.1 shows a typical multicore system-on-a-chip (SoC) with trace and debug infrastructure. It has N processor cores, a DSP core, and a DMA core. All the cores are connected through a system interconnect. Each processor core is connected to a private trace module for on-chip tracing and debugging support. This trace module is responsible for capturing and possibly filtering the trace data. As processors run at very high speeds, megabytes of trace data are generated within a fraction of a second making it difficult to emit the trace data off-chip.

To continuously emit trace data for longer periods of time, a dedicated highspeed trace port (parallel or serial) is used. However, dedicated trace ports require dedicated physical pins which increases the system cost. An external trace probe that reads traces from the target system includes large buffers, typically in Gigabytes and it is connected to the development workstation via standard interfaces such as USB or Ethernet [41] [42] [43] (see Figure 2.1). Most commonly available commercial trace probes are HSSTP (High Speed Serial Trace Probe) from ARM [44], SuperTrace Probe from GreenHills [41], PowerTrace Serial from Lauterbach [42], and Ultra-XD from Ashling [45].

To reduce the packaging size and/or cost introduced by the number of dedicated physical pins to stream the generated trace data off-chip, on-chip trace buffers are used to store the trace data temporarily. In that case, data from the trace buffer is either streamed through a low speed trace port like JTAG or a low pin-count trace port or copied to the target's system memory with the help of the operating system. The latter approach burdens the memory bus and system memory, affecting system performance. Hence, it is not well suited for embedded systems where performance degradation cannot be tolerated, and system memory is limited. In our work, we focus on data tracing through trace ports, though our proposed technique can help reduce the obtrusiveness of tracing in system memory.

The software debugger on the host workstation can use this information to understand the interactions between different software components and answer questions such as

- When are interrupts and context switches occurring?

- What is the execution path of the program?

- What events drive the program to a crash?

- Which parts of the program are taking most of the time?

- What memory address and values are accessed for memory operations?

In addition, replay of program execution allows software developers to move forward and backward in time while investigating bugs.

Figure 2.1 Multicore SoC with Trace and Debug Infrastructure

Recognizing the importance of hardware tracing in debugging, hardware vendors are adding on-chip support to capture and emit program traces for offline analysis. State-of-the-art hardware trace capturing technologies include ARM's

CoreSight [46], MIPS's PDtrace [47], Intel's Processor Trace [48], Infineon's Multicore Debug Solution (MCDS) [49], Synopsys's Real-Time Trace (RTT) [45], Altera [50], NXP [51], and others.

The IEEE Nexus 5001 standard [52] provides a standard interface to trace and debug embedded systems. It is a packet-based protocol and can use either a JTAG port or a high-speed dedicated Aurora or Auxiliary trace port to emit trace messages. It defines four classes of debugging capabilities depending on the level of details traced and exposed. Class 1 supports traditional run-control debugging – single stepping, analyzing and changing the memory values, and setting breakpoints through JTAG. Class 2 supports capturing control-flow traces and Ownership traces (task identifier). Class 3 includes support for capturing memory read and memory write traces. Class 4 adds an advanced capability for emulating memory and I/O accesses through a trace port. Each level progressively supports the features of lower classes. Thus, higher levels require more on-chip resources and wider trace ports, both of which increase system cost.

# 2.3 State-of-the-art Commercial Hardware Trace Solutions

ARM CoreSight. CoreSight is an advanced trace and debug solution for complex SOC based on the ARM architecture [46]. It is a collection of hardware components for tracing and debugging. Depending on the level of required debugging capabilities, a chip designer can choose individual modules and integrate them in the system. It includes tracing modules such as embedded trace macrocell (ETM), program trace macrocell (PTM), and system trace macrocell (STM). The collected trace data is either stored to a circular on-chip trace buffer, embedded trace buffer

(ETB), or emptied through a high-speed dedicated trace port interface or debug port (serial debug port or JTAG).

ARM STM. The STM module is designed to collect traces of system activity generated by both software and hardware events. A unique pair of master and channel are assigned to each hardware and software trace source. The number of available masters and channels is limited. In auto-instrumentation mode, STM can utilize existing static tracepoints in the kernel and built-in Linux tracing frameworks. By enabling the STM device driver and existing tracing framework [53], all the collected trace information is sent to STM hardware. To instrument applications, an application developer should define the instrumentation statement templates called tracers (like printf) to include in the source code. Tracers can be grouped into subsystems and each subsystem can be assigned to a single STM channel [53]. Every instrumentation statement includes the name, subsystem, and template details. The traces collected by STM can be interpreted and visualized by existing tracing frameworks such as LTTng on the host.

ARM PTM. The PTM module collects control-flow traces of a program [54]. To reduce the amount of trace data while enabling off-line reconstruction of the program flow, PTM avoids outputting the static information available in the program binary, program counter for example, and traces the flow changes such as indirect branches (with address and condition code), direct branches (condition code), context ID changes, exceptions, instruction barriers, changes in the processor instruction and security state, and entry and exit to the debug state. The PTM can collect differential timestamps (the number of clock cycles spent between the current and the previous trace), global system timestamps, and the destination of direct branches, if

required. The trace streams are stored in a FIFO buffer that when full sets an overflow signal that prevents further tracing.

ARM ETM. The ETM module can collect instruction and possibly data traces, memory address and value, for instructions executed by the processor. The ETM can be configured to generate only control-flow traces as in PTM instead of generating the traces for every instruction. The data-flow trace in ETM can be either memory address or memory address and value for load and/or store instructions. To enable efficient use of ETB and increase the trace coverage, ETM incorporates filtering and compression capabilities. For example, while collecting control-flow traces continuously, data-flow traces can be triggered for ranges of address or for a certain address or when the address bus sees a certain data value. In addition, ETM employs multiple trace compression techniques such as encoding multiple traces to a single stream when possible, excluding the program address for all the traces and target of direct branches, and avoiding the traces for some branches, when possible by including the return stack in the trace unit and in the trace analyzer.

Altera Nios II. Like the ARM ETM tracing module, the Nios II trace module supports tracing instructions and data [50]. To reduce the volume of trace data, Nios II provides filtering capabilities similar to ARM ETM. For example, it supports triggers to start and stop capturing control-flow and data-flow traces. The on-chip trace buffer size can be set to any size from 28 to 64 K trace frames, using OCI (on-chip instrumentation) On-chip Trace. A trace frame can store the execution trace for more than one instruction and a frame is defined as a unit of allocated memory for trace data and does not represent the absolute trace depth. The larger trace buffer consumes more on-chip M4K RAM blocks and every M4K RAM block can store up to 128 trace frames.

Infineon MCDS. Multicore Debug Solution (MCDS) is a trace and debug solution for Infineon chips [49]. It complies with the Nexus-5001 standard and supports program and data-flow tracing. Similar to other tracing solutions, MCDS employs trace compression and filtering (called trace qualification) to reduce trace data size. Instead of reporting full addresses, it only reports the changes in the address from last address in case of indirect branches, single bit for direct branches, and suppresses repeated zeros and ones in the MSB for data traces. An exception is synchronization traces which occur every few hundreds of clock cycles. Since the data traces produce large amounts of data, MCDS supports context aware compression techniques, for example, enabling capturing of data-traces when required.

Intel LBR. Last Branch Record (LBR) logs taken branches, interrupts, and exceptions to an LBR stack which is generally a set of model specific registers (MSRs) [55]. For every branch, LBR stores the branch-from address, branch-to address, and some additional metadata depending on the format address stored on the LBR stack. These registers act as a ring buffer and can store up to 32 branches depending on the CPU generation. There is no performance overhead for recording the branches, however, there is some overhead when reading trace records from these registers.

Intel BTS. The Branch Trace Store (BTS) provides additional capability to store branch trace messages (BTMs) to some monitoring device or the system memory allocated by the user. The format of the BTM record is similar to LBR: it includes the branch-from address, branch-to address, and a control word in which bit 4 is used to indicate whether the taken branch was predicted or not predicted. The size and location of the BTS buffer can be specified by the user and it can be configured as circular buffer (similar to an LBR stack) or to trigger an interrupt

when it is nearly full. Thus, BTS can store a larger number of branch records compared to LBR. However, this facility comes with overhead as the processor needs to enter special debugging mode in which processor speed drops by 25-30 times [56].

Intel PT. Intel Processor Trace (Intel PTrace) is an advanced version of Intel BTS which records control-flow traces with low runtime overhead (<5%) [57]. To improve the performance compared to BTS, it stores the encoded and more compact trace packets temporarily in the internal buffer before copying these to the memory subsystem. Intel PT supports various types of packets and only records the minimal information required to reconstruct the program flow. For example, it records only 1-bit to indicate whether the conditional branch was taken or not taken and it excludes the unconditional branches, as this information can be extracted from the program binary. With the support of hardware instruction pointer filtering, it can be configured to record traces for the instructions which are in or out of a range of addresses. Along with control flow traces, it also records certain processor mode changes (32/64-bit execution mode, VMCS pointer, TSX transaction state) and periodic synchronization points (TSC, mode frequency, SW context). It can be configured to report the cycle count either for every instruction in the trace or periodically.

MIPS PDtrace. PDtrace provides instruction and data trace capability for the MIPS architecture [47]. The trace logic on the processor outputs traces to a trace control block (TCB) which is responsible for writing these traces to either on on-chip or an off-chip trace buffer. When the trace buffer is full, it stalls the pipeline. To reduce the amount of trace data, PDtrace only captures the control-flow traces that are further compressed with synchronization trace except at the beginning of the process and after buffer overflow. For unpredictable branches, it reports changes in the PC (difference between the instruction address just before the branch and the branch

target). For conditional predictable branches, it either reports a single bit (taken or not taken). Nothing is reported for direct predictable branches. The synchronization trace addresses are reported periodically. Data address traces are compressed by reporting the delta difference and data values can be compressed with bit-block compression. Moreover, data-flow traces (address and value) can be collected only for the addresses which match with hardware breakpoint addresses.

Synopsys RTT. RTT, Real-Time Trace, is an optional hardware tracing module for Synopsys' ARC based processor cores. RTT generates trace messages which are compliant with Nexus 5001 Class 3. Based on power, area, and performance constraints, the RTT module can be configured at design time to capture different traces necessary for debugging. Trace modules are classified as small trace, medium trace, and full trace depending on their capabilities. Small trace modules record only the changes in the program-flow and use the dedicated on-chip trace buffer to store the traces. A medium trace module records program-flow changes and memory reads and writes and uses either dedicated on-chip memory or system shared memory or external storage on trace probes to save the traces. Full trace modules record auxiliary register reads and writes and CPU register writes in addition to the capabilities of medium trace modules. Full trace module can store trace messages on shared system memory or external storage. To store traces on external trace probes, support for the high-speed dedicated trace port, auxiliary Nexus port, is required. Just like any other trace module, RTT supports address range, data, and address trigger filters to reduce the amount of trace data.

### 2.4 Motivation

Hardware data traces are often necessary to faithfully replay a program under test offline. Generally, hardware data traces (a.k.a., data-flow traces) are generated by capturing relevant information about memory-referencing instructions, e.g., instruction addresses, data addresses, data values, and data sizes and types. However, not all of this information is necessary to replay a program offline. For example, a software debugger can infer memory write values under certain conditions from the program binary and memory read operations. Thus, to faithfully replay a parallel program offline, a software debugger requires only memory read data value traces along with (a) an instruction set simulator for the target platform; (b) the executable of the parallel program; (c) the initial state of the target's general- and special-purpose registers; and (d) exception traces. The exception traces and the memory read data value traces thus need to be captured on the target platform during program execution and streamed out through the target trace port. The following section illustrates the use of memory read data value traces in software debugging, specifically in the detection of race conditions in parallel programs.

### 2.4.1 Memory Read Data Value Tracing to Detect Race Conditions

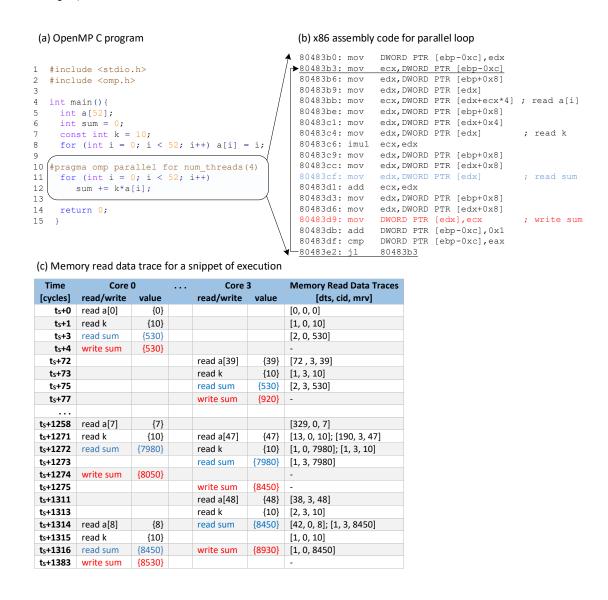

Figure 2.2 illustrates memory read data value tracing with a simple multithreaded OpenMP C program. The program shown in Figure 2.2a accumulates the scaled elements of an array, a[], to a shared variable sum, by using four threads running on four cores (C0-C3). Each thread in the program accumulates 13 elements of the array. The shared variable sum is intentionally not guarded by any locks to illustrate how memory read data value traces can be useful to detect data race conditions. A data race condition is observed on a shared variable when a memory read followed by a write operation in one thread is interspersed by a memory read or a memory write operation in another thread on the same variable (e.g., *sum* in this example).

Figure 2.2 Memory Read Data Value Tracing Example

Figure 2.2b shows the assembly instructions corresponding to the parallel for loop. In one iteration of the parallel for loop the following memory reads occur: (a) loop counter i, (b) element of the array a[i], (c) constant k, and (d) variable sum. The

memory writes are as follows: (a) updating loop counter i and (b) updating sum. Figure 2.2c shows the snippet of parallel execution of the for loop on cores C0 and C3 that execute threads 0 and 3, respectively, starting from the time ts. Threads 0 and 3 sum up elements a[0]-a[12] and a[39]-a[51], respectively. In Figure 2.2c, the first column shows the timestamp in which the corresponding instruction is retired, and the last column shows the hardware trace messages corresponding to memory reads. Each memory read results in a trace message composed of timestamp (dts), thread/core identifier (cid), and memory read value (mrv) similar to the Nexus 5001 standard [52]. The timestamp, dts, reports the number of clock cycles expired since the last trace message is reported from the same core/thread.

In the initial iteration of the *for* loop for C0, a[0], k, and sum are read and sum is updated at ts+4. The trace messages corresponding to memory read operations are shown in the last column of the first 3 rows. The memory write operation does not result a trace message as it can be inferred by the software debugger while replaying. Similarly, C3 reads array element a[39], as well as k and sum and updates the sum with a new value at ts+77. As we proceed in time, C0 reads a[7], k, and sum and writes a new value of the sum at ts+1274. However, C3 reads the sum at ts+1273 before it is updated by C0. Thus, C0 and C3 read the same value of sum and calculate its new values that are written into sum at ts+1274 by C0 and at ts+1275 by C1. This is a data race condition. While replaying the program in the software debugger, the situation where C1 reads the value of sum before it is updated by C0 is detected when read data traces of the program are supplied. One may argue that, by using data address access patterns we could also detect the race con-

dition. That can be true for this example however it is invaluable when the data is fed from an external source such as a sensor.

# 2.4.2 Memory Read Data Value Tracing Challenges

As discussed in Section 2.3, some commercial products support hardware tracing up to Class 3 [45] [46] [47] [49] [50] [51]. The trace port bandwidth required for these products is in the range of ~0.3 bits per instruction [17] for control-flow tracing and 8-16 bits per instruction for data-flow tracing [18] for a single core. In multicores, trace port bandwidth increases even further due to the need for reporting the processor identification number and timestamp in which the instruction is retired. With the limited size of on-chip-trace buffers, it is possible to capture traces only for short program segments. Usually the commercial products support collecting control-flow traces continuously and enables data-flow traces only for a range of addresses or for a memory address of interest or when a particular value from memory is read. In modern complex systems, the origin of a bug and its manifestation may be millions of instructions apart. Thus, it is important to capture traces for longer program segments or ideally for the entire program execution.

As a metric for quantitative evaluation of demands placed on designers of debug infrastructure, the required average trace port bandwidth (TPB) measured in bits per instruction (bpi) and bits per clock cycle (bpc) is used. The analytical model given in Eq.(2.1) and Eq.(2.2) can be used to estimate the average required TPB for read data value traces.

$$Average\ NX\_TPB\ [bpi] = mrFreq * (dtsSize + [log_2N] + mrvSize)$$

(2.1)

$$Average NX\_TPB [bpc] = Average NX\_TPB [bpi] * IPC$$

(2.2)

where

- *mrFreq* is the frequency of instructions that read data from memory

- *dtsSize* is the average size of the differential timestamp field in bits

- *mrvSize* is the average size of the data read from memory in bits

- *N* is the number of processor cores

- IPC is the number of instructions executed per clock cycle when all the cores are considered together

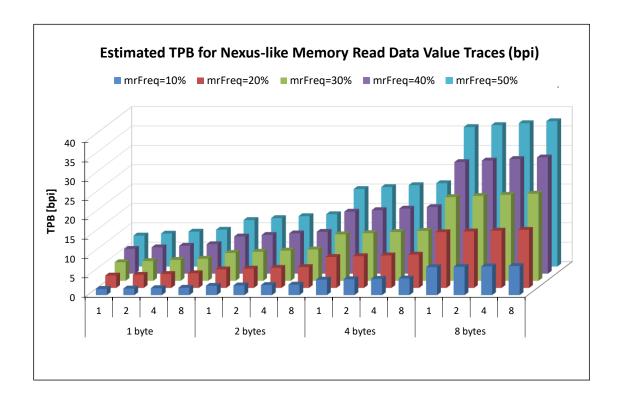

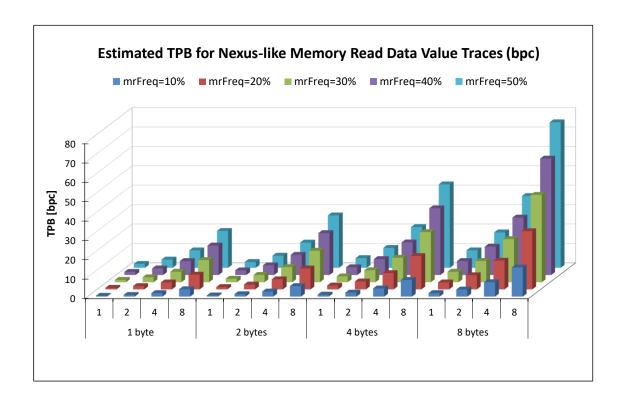

Figure 2.3 shows the estimated TPB in bpi while varying the frequency of instructions that read data from memory (10% to 50%), the number of cores (N = 1, 2, 4, and 8), and the average size of data items read from memory (1-byte to 8-bytes). Please note that, for simplicity, the average required TPB is often referred to just TPB. The TPB is calculated by using the Eq. (2.1); the number of bits to encode the timestamp, dts, is set to 8 bits. Figure 2.3 shows how the TPB increases with respect to the frequency of memory reads and the average size of the data read. As the average data size read from memory varies from 1 byte to 8 bytes, the TPB ranges from 1.6 bpi to 7.2 bpi when N=1 and from 1.9 bpi to 7.5 bpi when N=8, when 10% of the instructions are memory reads. For any given configuration, as the number of cores increases, the required TPB increases slightly due to the additional bits used to report core id. However, when the frequency of memory reads increases, the TPB in-

creases gradually as shown by the different rows in the Figure 2.3. When the frequency of memory reads reaches 50% (which is possible in memory intensive applications), the TPB is as high as 37.5 bpi for 8-byte data. As the number of cores increases, the pressure on the trace port increases due to the reduced execution time and multiple trace producers. However, this trend is not captured well using TPB measured in bits per instruction executed.

Figure 2.3 Estimation of Required Average TPB in bpi for Nexus-like Memory Read

Data Value Traces

Figure 2.4 shows the estimated TPB in bpc while varying the frequency of instructions that read data from memory (10% to 50%), the number of cores (N = 1, 2, 4, and 8), and the average data size read from memory (1-byte to 8-bytes). The TPB shown in Figure 2.4 is calculated by using Eq. (2.2) with IPC set to N/4. It ranges

from 0.4 bpc (N=1) to 3.8 bpc (N=8) when *mrvSize* is 1-byte and from 3.6 bpc (N=1) to 30 bpc (N=8) when *mrvSize* is 8-byte when 10% of the instructions are memory reads. When the frequency of memory reads is 50%, the required TPB is as high as 75 bpc. For TPB estimation, we assumed that memory reads are evenly distributed over the execution of the program. However, there is a possibility of having skewed data reads. In that case, the pressure on the trace port will be even higher.

Figure 2.4 Estimation of Required Average TPB in bpc for Nexus like Memory Read

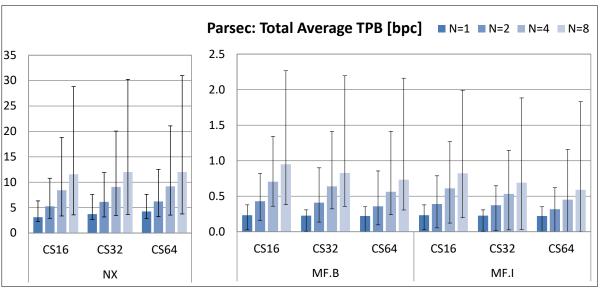

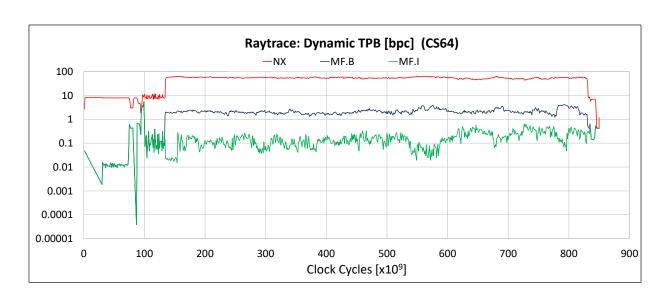

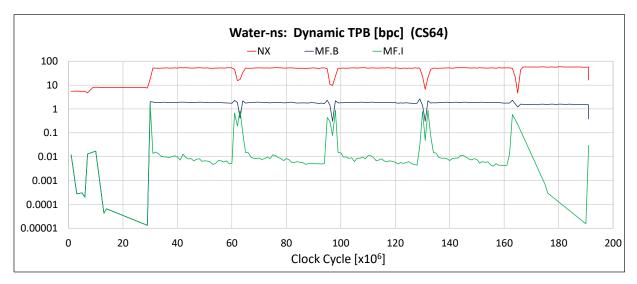

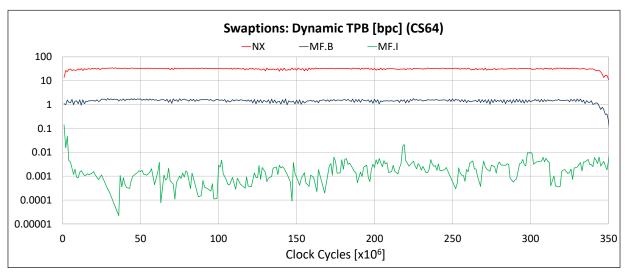

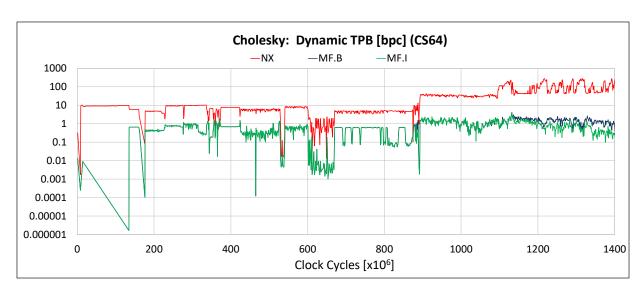

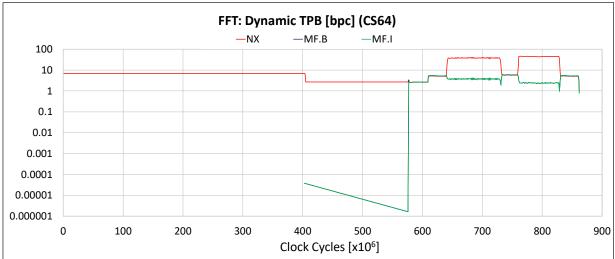

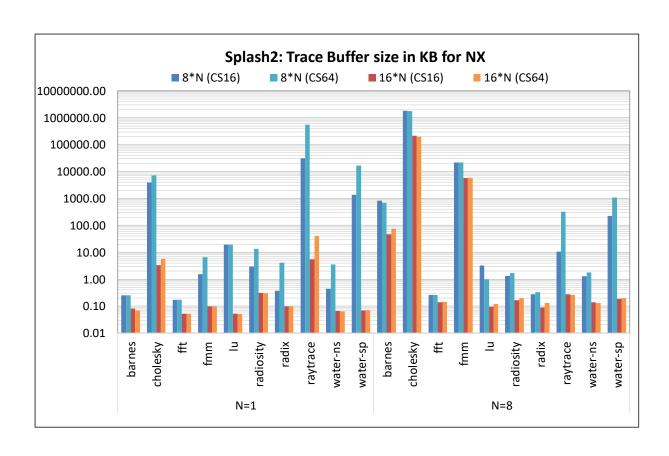

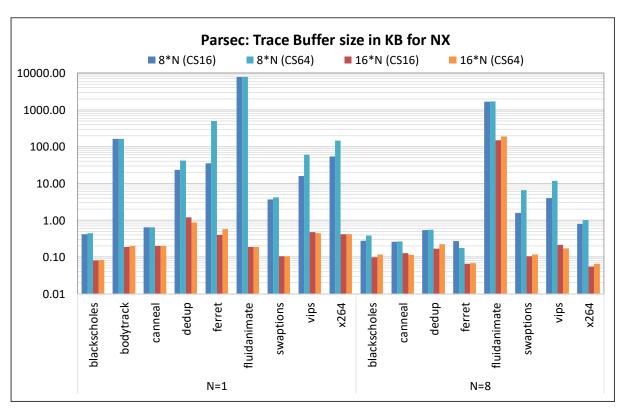

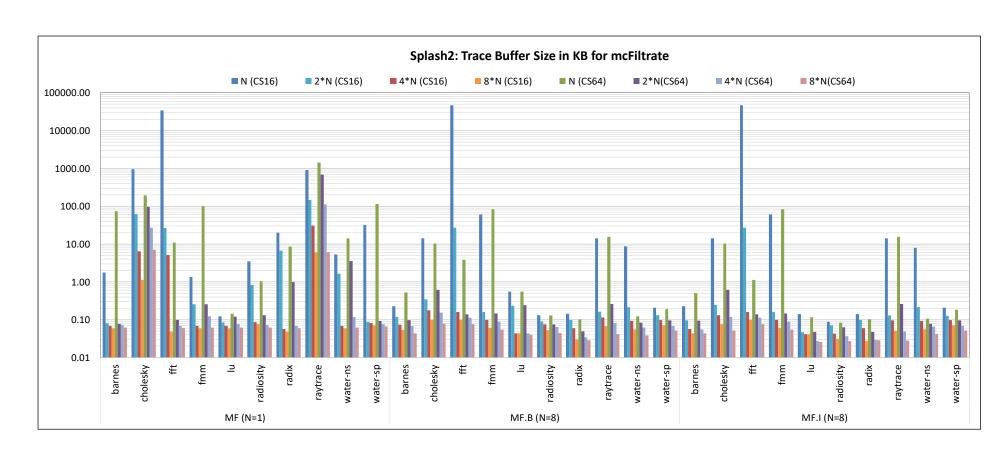

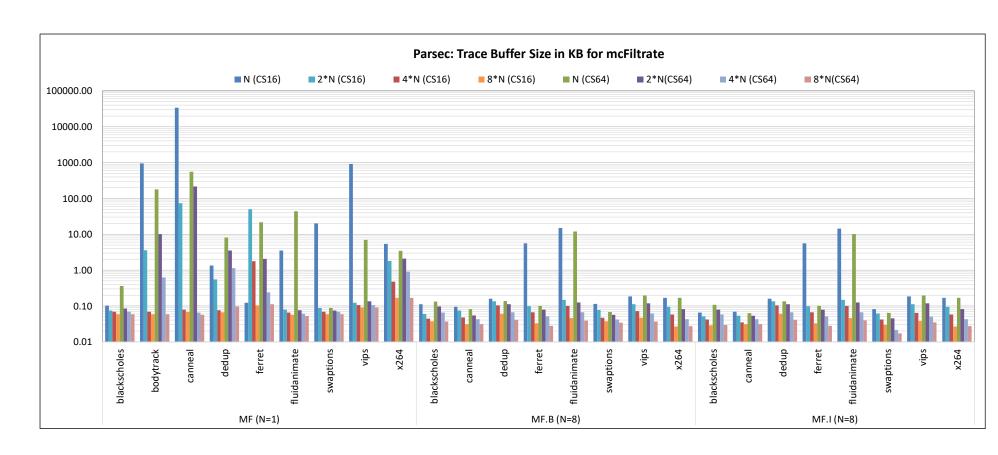

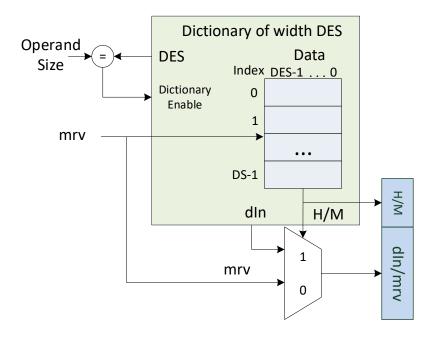

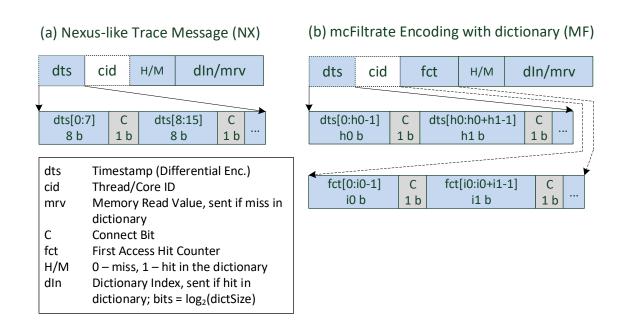

Data Value Traces