# ARCHITECTURES FOR RUN-TIME VERIFICATION OF CODE INTEGRITY

by

# MILENA MILENKOVIC

## A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in The Shared Computer Engineering Program of The University of Alabama in Huntsville The University of Alabama at Birmingham to The School of Graduate Studies of The University of Alabama in Huntsville

# HUNTSVILLE, ALABAMA

2005

In presenting this dissertation in partial fulfillment of the requirements for a doctoral degree from The University of Alabama in Huntsville, I agree that the Library of this University shall make it freely available for inspection. I further agree that permission for extensive copying for scholarly purposes may be granted by my advisor or, in his absence, by the Chair of the Department or the Dean of the School of Graduate Studies. It is also understood that due recognition shall be given to me and to The University of Alabama in Huntsville in any scholarly use which may be made of any material in this dissertation.

(student signature)

(date)

### **DISSERTATION APPROVAL FORM**

Submitted by Milena Milenkovic in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the dissertation committee.

We, the undersigned members of the Graduate Faculty of the University of Alabama in Huntsville and the University of Alabama in Birmingham, certify that we have advised and/or supervised the candidate on the work described in this dissertation. We further certify that we have reviewed the dissertation manuscript and approve it in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering.

Committee Chair

(Date)

Department Chair

College Dean

Graduate Dean

#### ABSTRACT

#### The School of Graduate Studies The University of Alabama in Huntsville

| Degree Doctor of Philo | osophy |

|------------------------|--------|

|------------------------|--------|

College/Dept. Engineering/Electrical and Computer Engineering

Name of Candidate Milena Milenkovic

Title Architectures For Run-Time Verification of Code Integrity

With the exponential growth of the number of interconnected computing platforms, computer security becomes a critical issue. As software continues to grow in size and complexity, so does the number of security vulnerabilities: According to the US-CERT Coordination Center, the number of vulnerabilities reported has grown from 171 in 1995 to 4,129 in 2002. One of the major security problems is the execution of unauthorized and potentially malicious code. This problem can be addressed at different levels, from more secure software and operating systems, down to solutions based on hardware support. The majority of the existing techniques tackle the problem of security flaws at the software level, lacking generality, often inducing prohibitive overhead in performance and cost, or generating a significant number of false alarms. On the other hand, a further increase in the number of transistors on a single chip will enable integrated hardware support for functions that were so far restricted to the software domain. Hardware-supported defense techniques have the potential to be more general and more efficient than solely software solutions. This dissertation proposes new architectural extensions to ensure trusted program execution in both high-end and embedded computing platforms. The eight proposed techniques have low performance overhead, low hardware complexity, and minimal or no compiler support.

| Abstract Approval: | Committee Chair  |

|--------------------|------------------|

|                    | Department Chair |

|                    | Graduate Dean    |

#### ACKNOWLEDGMENTS

"I thank you for making this day necessary." Yogi Berra

I wish to express my deepest gratitude to many persons who made my PhD dissertation possible.

I thank my advisor, Dr. Emil Jovanov, for his constant support and guidance. I will be always grateful to Dr. Reza Adhami, Chair of the Electrical and Computer Engineering Department, for encouraging me to pursue PhD studies, and for providing me with financial support through the teaching assistantship during the Spring 2002 semester. Many thanks to Dr. Jeff Kulick for inspiring talks about malicious attacks and hardware-supported security. Thanks go out also to other members of my committee, Dr. Gary J. Grimes, Dr. Peter Slater, Dr. B. Earl Wells, and Dr. Seong-Moo Yoo, for their invaluable feedback. Dr. Yale Patt from the University of Texas in Austin first introduced me to the wonderful philosophy of Yogi Berra, and has been a source of inspiration for all my research work. Last but not least, this dissertation would not be possible without my husband, Dr. Aleksandar Milenkovic, who encouraged me to pursue the PhD research, collaborated with me on secure architectures, and provided me an inspirational work environment in the LaCASA laboratory.

I also thank my family in Serbia, for their unconditional love and support.

# TABLE OF CONTENTS

|     |          |                                                                   | Page |

|-----|----------|-------------------------------------------------------------------|------|

| LIS | ST OF FI | GURES                                                             | VIII |

| LIS | ST OF TA | ABLES                                                             | X    |

| CH  | IAPTER   |                                                                   |      |

| 1   | INTRO    | DUCTION                                                           | 1    |

|     | 1.1      | Background and Motivation                                         | 1    |

|     | 1.2      | Existing Techniques for Defense Against Code Injection Attacks    | 2    |

|     | 1.3      | Architectures For Instruction Block Signature Verification        | 3    |

|     | 1.4      | Main Contributions                                                | 4    |

|     | 1.5      | Dissertation Outline                                              | 4    |

| 2   | SOFTW    | VARE VULNERABILITIES AND CODE INJECTION ATTACKS                   | 5    |

|     | 2.1      | Stack-Based Buffer Overflow Attacks                               | 5    |

|     | 2.2      | Heap-Based Buffer Overflow Attacks                                | 6    |

|     | 2.3      | Format String Attacks                                             | 7    |

|     | 2.4      | Integer Error Attacks                                             | 8    |

|     | 2.5      | Double free() attacks                                             | 8    |

|     | 2.6      | A Format String Attack Example                                    | 9    |

| 3   |          | ING TECHNIQUES FOR DETECTION AND PREVENTION OF CODE INJECTION CKS | 12   |

|     | 3.1      | Static Software-Based Techniques                                  | 12   |

|     | 3.2      | Dynamic Software-Based Techniques                                 | 17   |

|     | 3.3      | Defense Techniques With Hardware Support                          | 31   |

|    | 3.4   | Other Related Work                                    |     |

|----|-------|-------------------------------------------------------|-----|

| 4  | PROPC | OSED ARCHITECTURES FOR INSTRUCTION BLOCK VERIFICATION | 41  |

|    | 4.1   | Basic Mechanism of Proposed Techniques                | 41  |

|    | 4.2   | Taxonomy of Proposed Techniques                       | 44  |

|    | 4.3   | Details of SIGCE Techniques                           | 50  |

|    | 4.4   | Details of SIGCT Techniques                           | 57  |

|    | 4.5   | Details of SIGB Techniques                            | 61  |

|    | 4.6   | Discussion                                            | 70  |

| 5  | EXPER | RIMENTAL METHODOLOGY                                  | 74  |

|    | 5.1   | Evaluation of Proposed Techniques                     | 74  |

|    | 5.2   | ELF Format                                            | 75  |

|    | 5.3   | Secure Installation of Files in ELF Format            | 78  |

|    | 5.4   | SimpleScalar Simulator                                | 79  |

|    | 5.5   | SimpleScalar Modifications                            | 82  |

|    | 5.6   | Custom-Made Trace-Driven Simulator                    | 82  |

|    | 5.7   | Simulator Parameters                                  | 86  |

|    | 5.8   | Benchmarks                                            | 89  |

| 6  | EVALU | JATION RESULTS                                        | 94  |

|    | 6.1   | SIGC Evaluation                                       | 94  |

|    | 6.2   | SIGB Evaluation                                       | 124 |

| 7  | CONC  | LUSION                                                | 134 |

| RE | FEREN | CES                                                   | 137 |

# LIST OF FIGURES

| Figure | Page                                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------|

| 2.1    | An illustration of a buffer overflow attack on the stack                                                                      |

| 2.2    | An illustration of the use of the %n format character7                                                                        |

| 2.3    | Allocated and free memory chunk organization, GNU C library malloc()9                                                         |

| 2.4    | An example of a vulnerable program10                                                                                          |

| 2.5    | Malicious input and the corresponding output for the above program, and the stack content (SP – stack pointer)                |

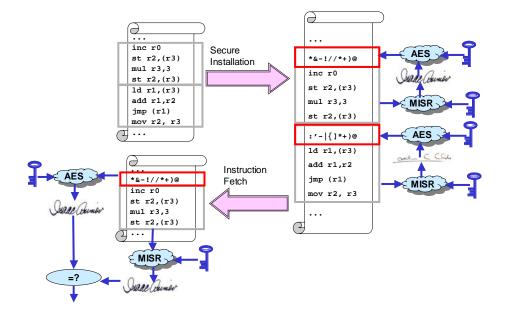

| 4.1    | Mechanism for trusted instruction execution                                                                                   |

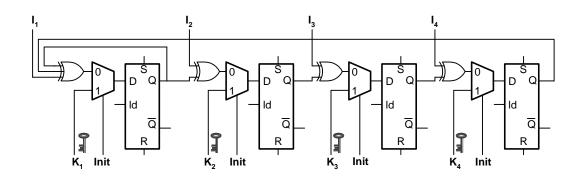

| 4.2    | An implementation of a 4-bit MISR                                                                                             |

| 4.3    | Processor components                                                                                                          |

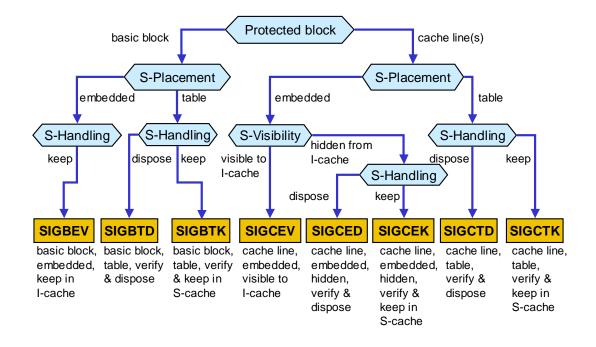

| 4.4    | Taxonomy of proposed instruction block verification techniques45                                                              |

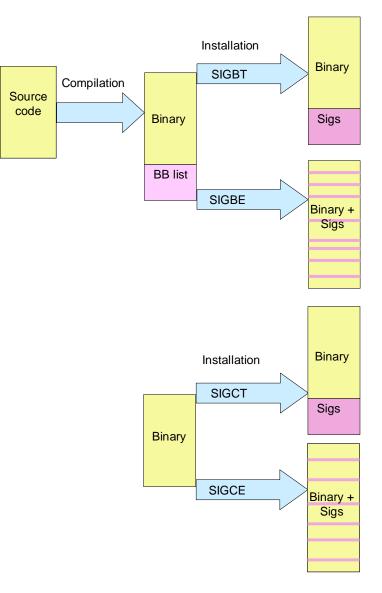

| 4.5    | Modification of executable code                                                                                               |

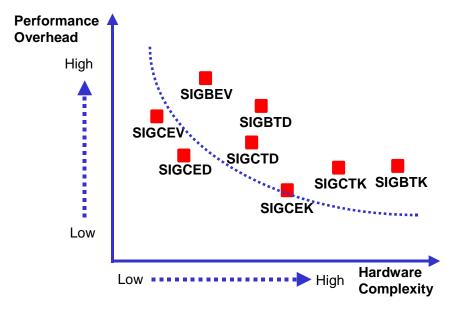

| 4.6    | Qualitative assessment of signature verification techniques in the performance overhead -<br>hardware complexity design space |

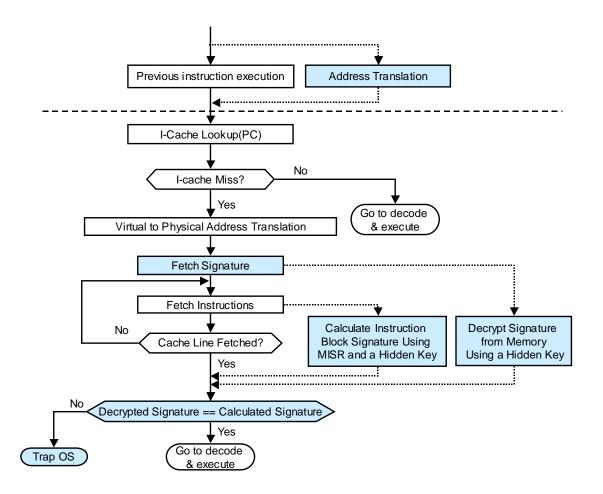

| 4.7    | SIGCED: Signature verification control flow                                                                                   |

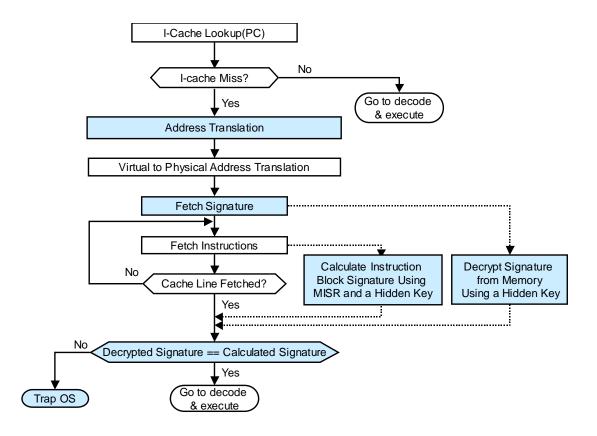

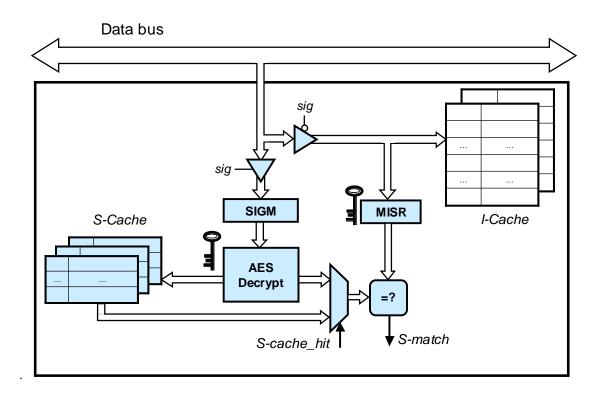

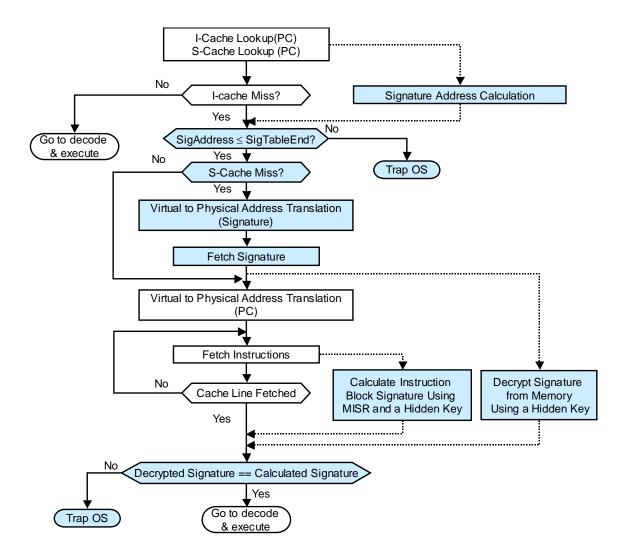

| 4.8    | SIGCED: Instruction Block Signature Verification Unit                                                                         |

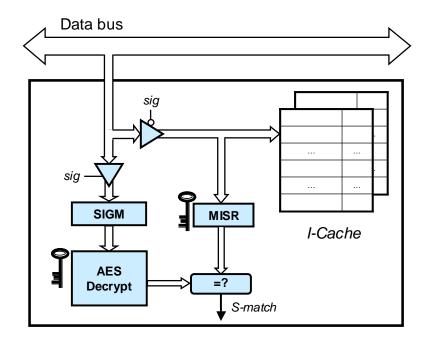

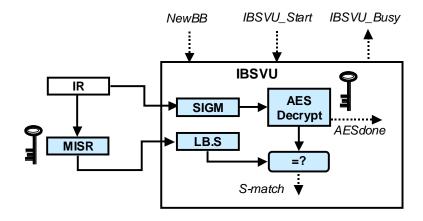

| 4.9    | SIGCEK: Signature verification control flow                                                                                   |

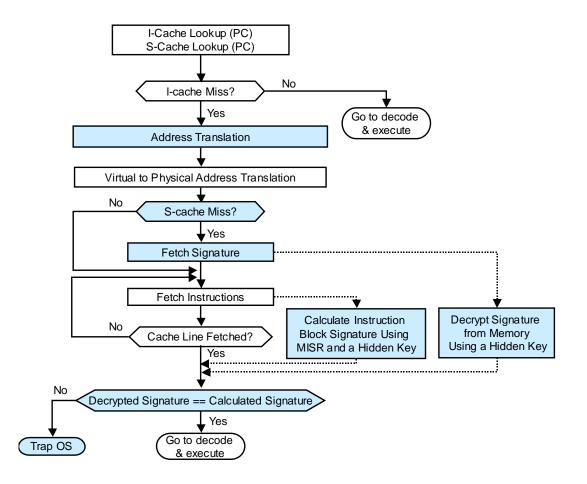

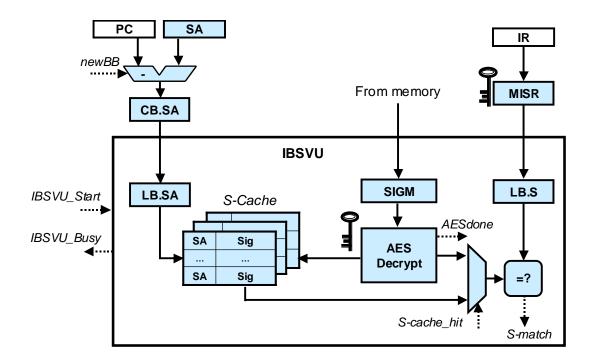

| 4.10   | SIGCEK: Instruction Block Signature Verification Unit                                                                         |

| 4.11   | SIGCEV: Signature verification control flow                                                                                   |

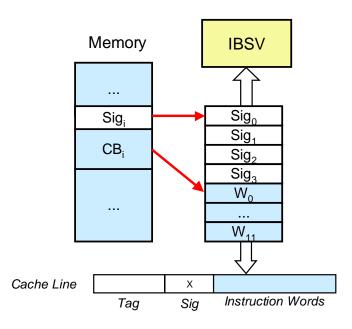

| 4.12   | The content of an I-cache line with the SIGCEV technique                                                                      |

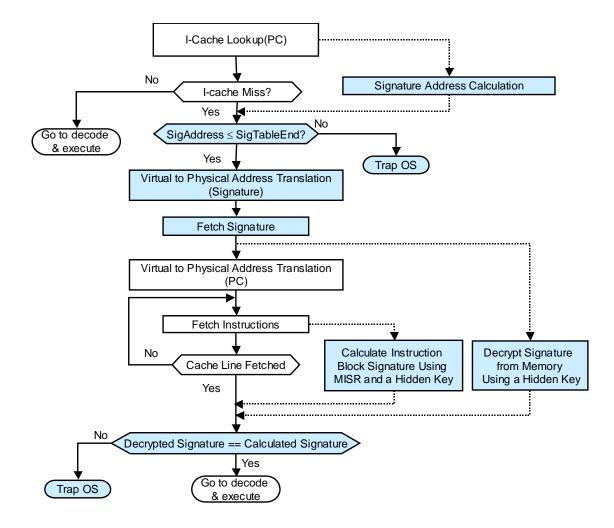

| 4.13   | SIGCTD: Signature verification control flow                                                                                   |

| 4.14   | SIGCTK: Signature verification control flow                                                                                   |

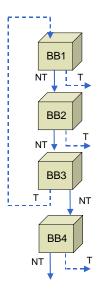

| 4.15   | Instruction streams                                                                                                           |

| 4.16   | SIGBEV: An example of the original and the protected code                                                                     |

| 4.17 | SIGBEV: Instruction Block Signature Verification Unit                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.18 | SIGBEV Procedures                                                                                                                                       |

| 4.19 | SIGBTK: Instruction Block Signature Verification Unit                                                                                                   |

| 4.20 | SIGBTK Procedures                                                                                                                                       |

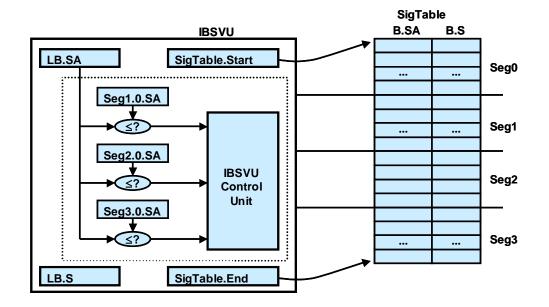

| 4.21 | SigTable access using segment approach                                                                                                                  |

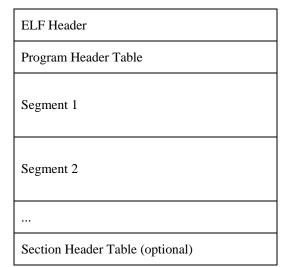

| 5.1  | Linking and execution view of an ELF file76                                                                                                             |

| 5.2  | The main simulator loop body in the sim-outorder simulator                                                                                              |

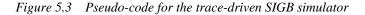

| 5.3  | Pseudo-code for the trace-driven SIGB simulator                                                                                                         |

| 5.4  | Pseudo-code for the function verify_signature()                                                                                                         |

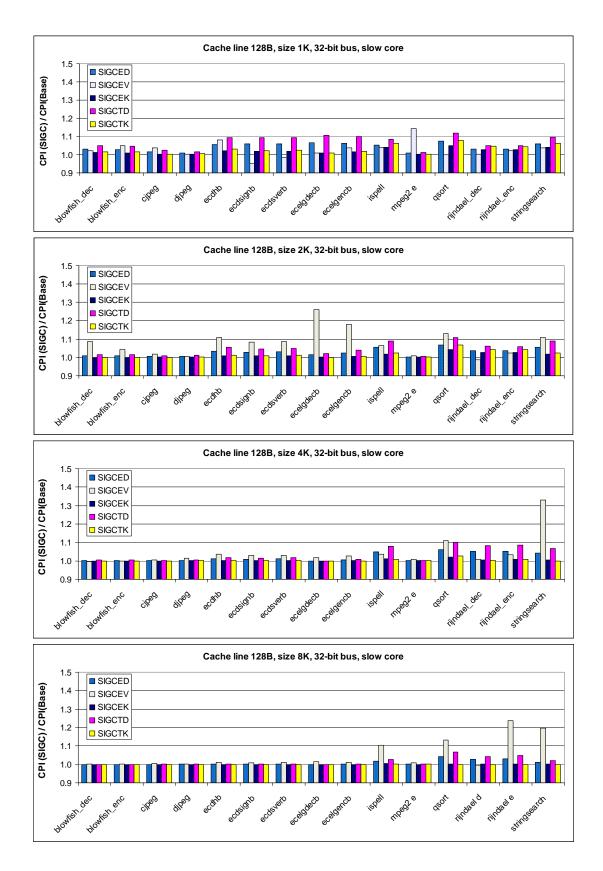

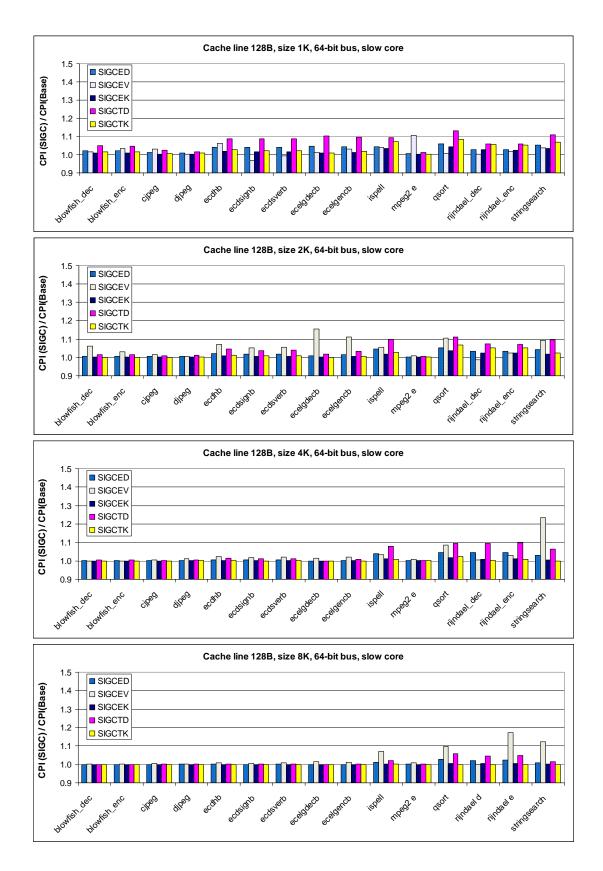

| 6.1  | SIGC: embedded processor configuration, I-cache line 128B, 32-bit bus, slow core110                                                                     |

| 6.2  | SIGC: embedded processor configuration, I-cache line 128B, 64-bit bus, slow core111                                                                     |

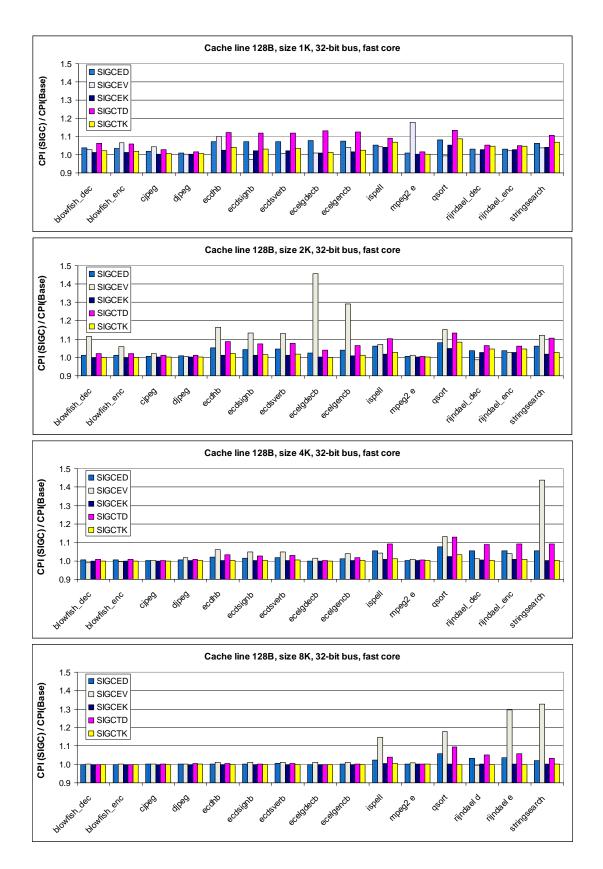

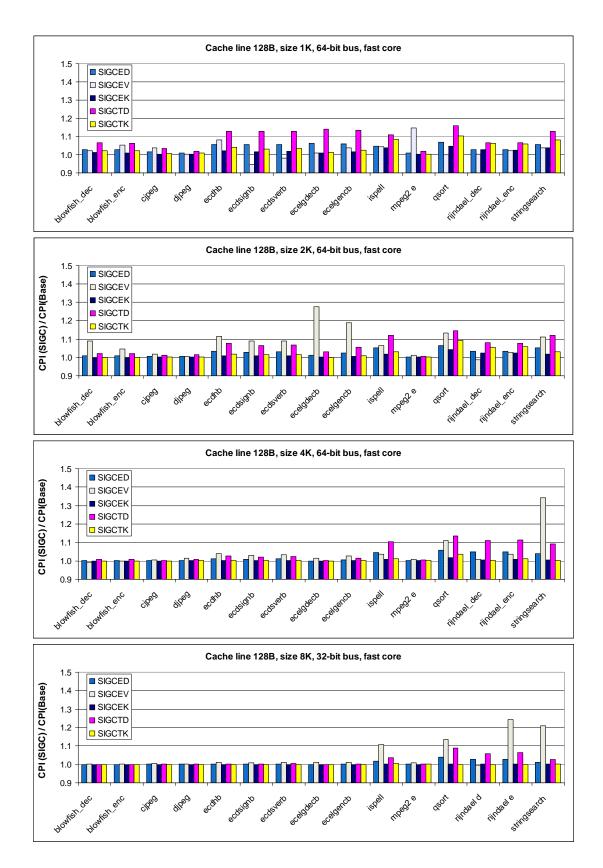

| 6.3  | SIGC: embedded processor configuration, I-cache line 128B, 32-bit bus, fast core112                                                                     |

| 6.4  | SIGC: embedded processor configuration, I-cache line 128B, 64-bit bus, fast core113                                                                     |

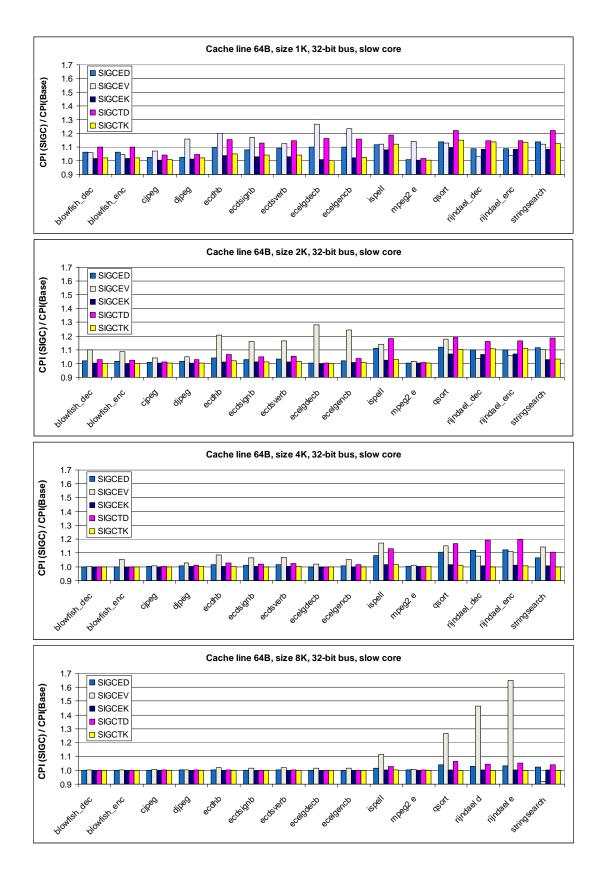

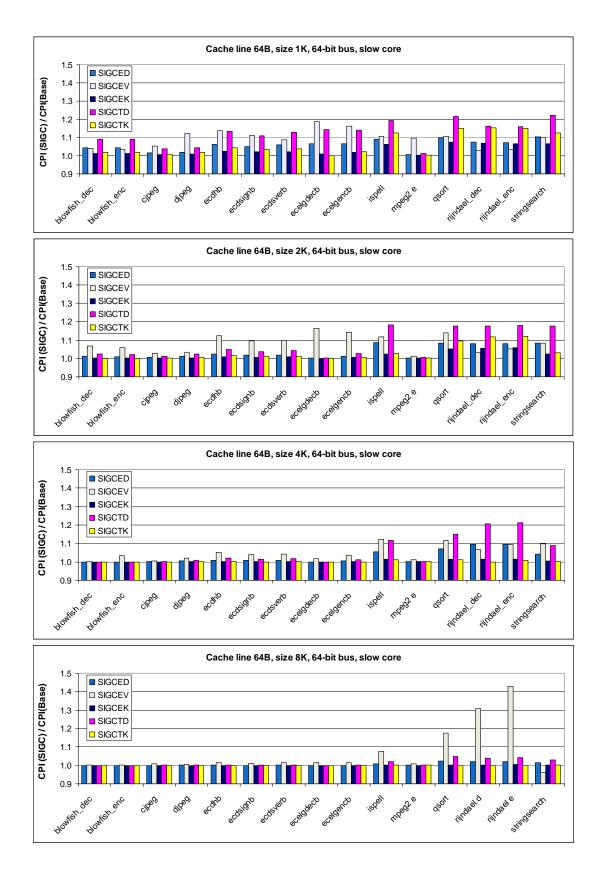

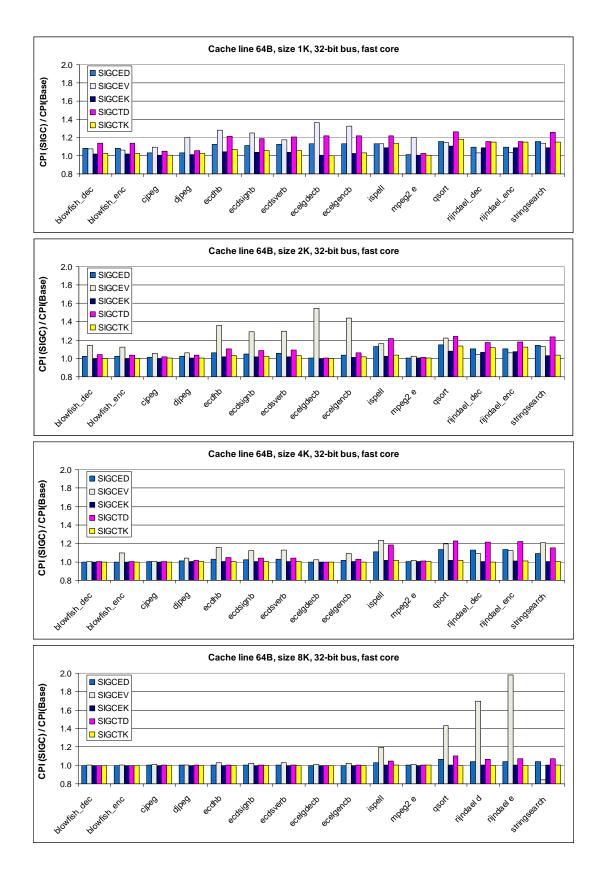

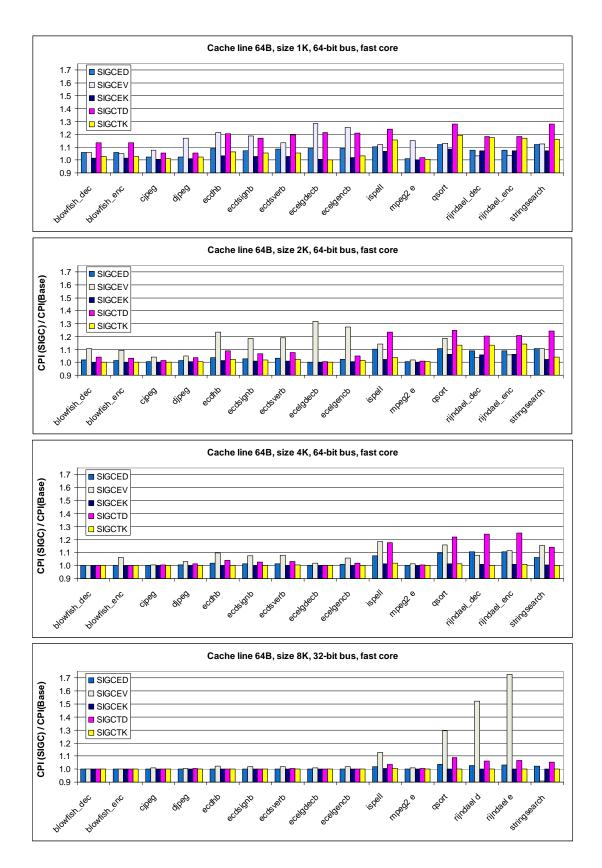

| 6.5  | SIGC: embedded processor configuration, I-cache line 64B, 32-bit bus, slow core114                                                                      |

| 6.6  | SIGC: embedded processor configuration, I-cache line 64B, 64-bit bus, slow core115                                                                      |

| 6.7  | SIGC: embedded processor configuration, I-cache line 64B, 32-bit bus, fast core116                                                                      |

| 6.8  | SIGC: embedded processor configuration, I-cache line 64B, 64-bit bus, fast core117                                                                      |

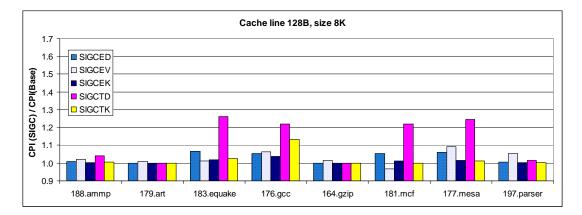

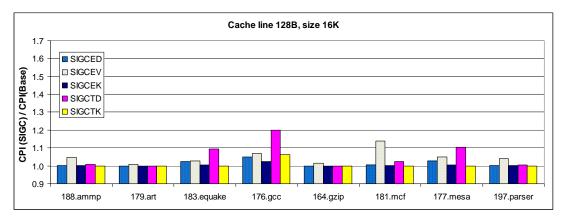

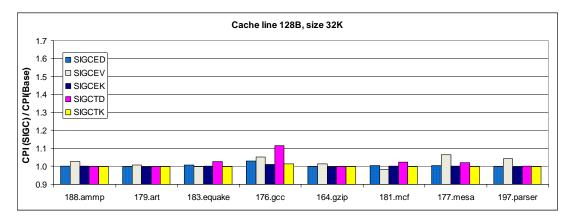

| 6.9  | SIGC: high-end processor configuration, I-cache line 128B                                                                                               |

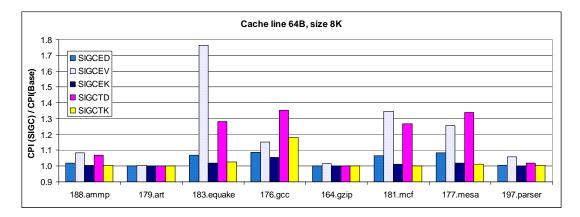

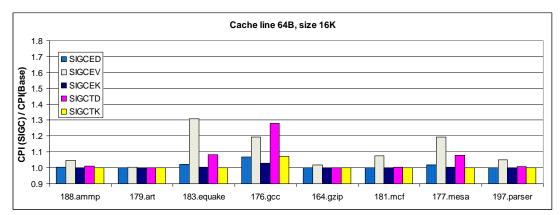

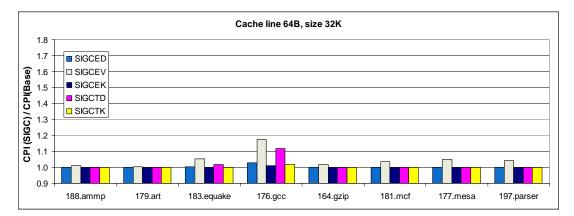

| 6.10 | SIGC: high-end processor configuration n, I-cache line 64B119                                                                                           |

| 6.11 | SIGBTK: Number of S-cache misses as a function of S-cache size I-cache size: 32K128                                                                     |

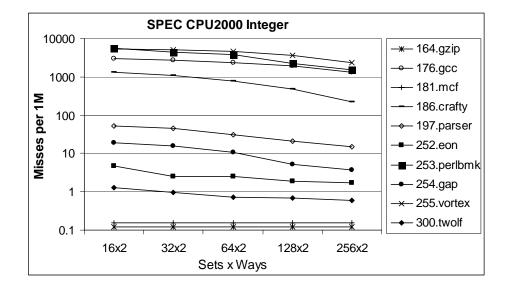

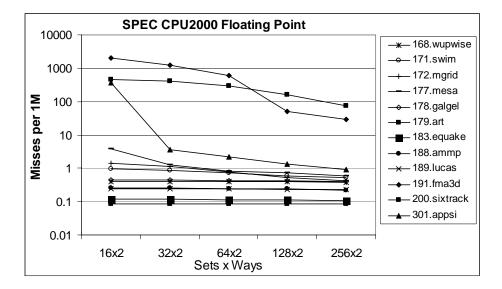

| 6.12 | SIGBTK: Number of S-cache misses as a function of S-cache associativity I-cache size: 32K129                                                            |

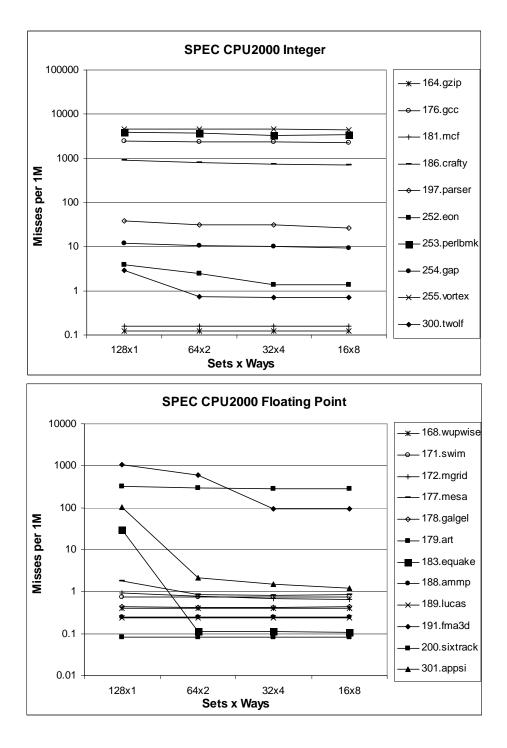

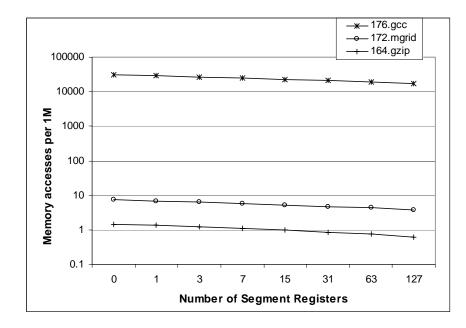

| 6.13 | SIGBTK: Number of memory accesses per 1M instructions due to S-cache misses with the segmented binary search, (128-set, 2-way) S-cache, and 32K I-cache |

# LIST OF TABLES

| Table | Pa                                                                                | ige |

|-------|-----------------------------------------------------------------------------------|-----|

| 3.1   | Static software-based techniques                                                  | 14  |

| 3.2   | Techniques that instrument code to verify run-time bounds                         | 18  |

| 3.3   | Attack-specific techniques                                                        | 19  |

| 3.4   | "Safe dialects" of C                                                              | 19  |

| 3.5   | Obfuscation techniques                                                            | 19  |

| 3.6   | Program monitoring techniques                                                     | 20  |

| 3.7   | Techniques with hardware support                                                  | 32  |

| 4.1   | Pros and cons of different techniques                                             | 49  |

| 5.1   | Some common ELF file sections                                                     | 77  |

| 5.2   | Descriptions of .c files used by SimpleScalar simulators                          | 81  |

| 5.3   | Simulator parameters for the embedded processor configuration                     | 87  |

| 5.4   | Simulator parameters for the high-end processor configuration                     | 88  |

| 5.5   | Description of benchmarks from embedded domain                                    | 90  |

| 5.6   | Benchmark code size and executed instructions for embedded systems                | 91  |

| 5.7   | Description of SPEC CPU2000 benchmarks and the size of precompiled Alpha binaries | 92  |

| 5.8   | The size of SPEC CPU2000 benchmarks when compiled with the ARM gcc compiler       | 93  |

| 6.1   | Base: I-cache misses per 1000 instructions in embedded processor configurations   | 96  |

| 6.2   | Base: CPI in embedded processor configurations, slow core, memory bus 32 bits     | 97  |

| 6.3   | Base: CPI in embedded processor configurations, slow core, memory bus 64 bits     | 98  |

| 6.4   | Base: CPI in embedded processor configurations, fast core, memory bus 32 bits     | 99  |

| 6.5   | Base: CPI in embedded processor configurations, fast core, memory bus 64 bits1    | 00  |

| 6.6  | Base: I-cache misses per 1M executed instructions in high-end processor configurations101      |

|------|------------------------------------------------------------------------------------------------|

| 6.7  | Base: CPI in high-end processor configurations101                                              |

| 6.8  | SIGCEV: I-cache misses per 1000 executed instructions in embedded processor configurations 107 |

| 6.9  | SIGCEV: I-cache misses per 1M executed instructions in high-end processor configurations108    |

| 6.10 | S-cache misses per 1000 executed instructions in high-end processor configurations108          |

| 6.11 | S-cache misses per 1000 executed instructions in embedded processor configurations109          |

| 6.12 | Percentage of file size increase for SPEC CPU2000 benchmarks                                   |

| 6.13 | Percentage of file size increase for benchmarks from the embedded domain122                    |

| 6.14 | Percentage of file size increase for SPEC CPU2000 benchmarks                                   |

| 6.15 | SIGBTK: Number of I-cache misses and signature verifications per 1M instructions126            |

| 6.16 | SIGBTK: Number of S-cache misses per 1M instructions                                           |

| 6.17 | SIGBEV: Number of I-cache misses and signature verifications per 1M instructions131            |

| 6.18 | Number of basic blocks and percentage of file size increase                                    |

## **CHAPTER 1**

### **INTRODUCTION**

"The art of war teaches us to rely not on the likelihood of the enemy's not coming, but on our own readiness to receive him; not on the chance of his not attacking, but rather on the fact that we have made our position unassailable."

Sun Tzu, "The Art of War"

With the exponential growth of the number of interconnected computing platforms, computer security becomes a critical issue. Today's society now more than ever relies upon computers and networks. Networked computing platforms make up the fabric of society's infrastructure; in fact, ubiquitous accessibility and interconnectivity are the driving forces in our modern economy, education, entertainment, medicine, transportation, and the military. Unfortunately, by connecting a computer system to the Internet or a local network, we expose its vulnerabilities to potential attackers. Failing to resist attacks can incur significant direct costs as well as costs in lost revenues and opportunities. The utmost importance of system security is further underscored by the increased complexity of high-end systems as well as the expected proliferation of diverse Internet-enabled, low-end embedded systems -- ranging from home appliances, cars, and sensor networks to personal health monitoring devices.

#### 1.1 Background and Motivation

A very large group of malicious attacks on applications running on general-purpose processors consists of different techniques that impair the software integrity, by injecting and then executing the malicious code instead of regularly installed programs. The most widely known type of such attacks is socalled stack smashing, where an attacker overflows a buffer stored on the stack with a malicious code sequence and replaces a valid return address with the malicious code address [1]. In addition, various other examples of attacks exist, such as heap overflow [2], format string attacks [3], and attacks exploiting integer errors [4] or dangling pointers [5]. The number of reported software vulnerabilities has grown from 171 in 1995 to 4,129 in 2002, according to the United States Computer Emergency Readiness Team Coordination Center (US-CERT/CC) [6].

Applications targeting embedded systems may suffer from the same vulnerabilities as applications running on general-purpose platforms. For example, one recent Cyber Security Bulletin from US-CERT reports multiple buffer overflow vulnerabilities in a Bluetooth connectivity program for Personal Digital Assistants (PDAs) [7]. Another US-CERT Cyber Security Bulletin indicates an emerging trend of mobile phone viruses [8]. As the communication and computation capabilities of smart phones, PDAs, and other embedded systems continue to grow, so will the number of malicious attacks trying to exploit code vulnerabilities.

### 1.2 Existing Techniques for Defense Against Code Injection Attacks

The multitude of code injection attacks prompted development of a large number of predominantly software-based counter-measures. Static software techniques rely on formal analysis and/or programmers' annotations to detect security flaws in the code, and then leave it to the programmers to correct these flaws. However, the use of these techniques has yet to become a common programming practice. Moreover, they fail to discover all vulnerabilities, suffer from false alarms, or put an additional burden on programmers. On the other hand, dynamic software techniques augment the original code or operating system to detect malicious attacks and to terminate attacked programs, or to reduce the attacker's chances of success. Though effective, these techniques can result in significant performance overhead and usually require program recompilation, so they are not readily applicable to legacy software.

Current trends in both hardware and software make us believe that dedicated processor resources should be used to ensure software integrity, consequently improving computer system security [9]. Software techniques by themselves are unlikely to counter all attacks, since more complex applications have potentially a larger number of defects, computing systems are becoming more diverse, and time-to-market constraints severely limit testing time. On the other hand, a further increase in the number of

transistors on a single chip will enable integrated hardware support for functions that so far have been restricted to the software domain. A form of hardware protection from buffer overflow has already found its way into mainstream general-purpose processors, AMD's Athlon-64 and Intel's Itanium [10]. Several recent research efforts propose hardware-supported techniques to prevent unauthorized changes of program control flow. Most of these techniques focus only on stack smashing or have significant performance overhead, or do not thoroughly explore the implications of implementation choices. We believe that there is a need for a new hardware security layer to prevent the whole class of code injection attacks.

#### 1.3 Architectures For Instruction Block Signature Verification

This dissertation proposes and evaluates new architectural extensions to ensure trusted program execution in high-performance and embedded computing platforms at minimal cost, power overhead, and performance loss. We propose several new techniques that share a common mechanism: Instruction blocks are signed using secret hardware keys during the secure program installation process, and signatures are stored with the code. During program execution, signatures are recalculated from instructions and compared to the stored signatures. If the two values do not match, the program cannot be trusted and should be terminated. The proposed techniques differ in type of protected instruction blocks, signature placement in the address space, signature placement in the physical memory, and signature handling after the verification.

Hardware-supported techniques have the potential to provide trusted program execution with lower overhead in performance and overall power consumption than techniques relying solely on software. Instead of vulnerability-specific solutions, the proposed architectures offer protection from a whole class of vulnerabilities that allow execution of a malicious code. Moreover, since with our mechanism each program requires a secure installation process, viruses cannot penetrate the system without explicit permission by the user. The proposed mechanism does not require significant processor changes and can be implemented even as a separate co-processor; it is cost-effective and requires no changes in legacy source code; several considered techniques do not require compiler support, while others require minimal compiler support. In addition, encrypted instruction block signatures protect the code from software tampering, and enable fault detection in error-prone environments such as Space.

#### 1.4 Main Contributions

The main contribution of this dissertation is a proposal of a novel hardware-supported mechanism for defense against code injection attacks. The proposed mechanism is based on run-time verification of instruction block signatures. We give taxonomy, detailed design, and performance evaluation for eight implementations of this mechanism.

Another contribution is an extensive survey of related work. The survey encompasses a wide range of software and hardware solutions proposed to counter malicious code injection attacks. Finally, the work on this dissertation resulted in a number of extensions for SimpleScalar simulator and a custom-made trace-driven simulator.

#### 1.5 Dissertation Outline

The rest of this dissertation is organized as follows. Chapter 2 gives an overview of security vulnerabilities that may be exploited by code injection attacks.

Chapter 3 gives a survey of software-based static and dynamic defense techniques, and hardwaresupported techniques. Several related fault-tolerant techniques and anti-tampering techniques are also mentioned. The proposed mechanism for run-time instruction block verification is explained in Chapter 4. This chapter also includes taxonomy of proposed architectural extensions, detailed descriptions of each technique, and a discussion of implementation challenges and limitations.

Chapter 5 describes experimental methodology used in this dissertation. It gives a short description of execution-driven simulator SimpleScalar and the modifications we made. It also describes a custom-made trace-driven simulator. The ELF format and various benchmarks used for evaluation are also described in this chapter, as well as metrics used for evaluation and simulator parameters fixed for all experiments.

Chapter 6 presents evaluation results and discusses them for a wide set of benchmarks. Finally, Chapter 7 states conclusions and indicates future research possibilities.

### **CHAPTER 2**

### SOFTWARE VULNERABILITIES AND CODE INJECTION ATTACKS

"We made too many wrong mistakes." Yogi Berra

A successful code injection attack must achieve two goals: it must inject the malicious code sequence, and it must change the value of a code pointer to point to the address of the injected code. The most common software vulnerabilities that can be exploited by code injection attacks are input buffers without boundary checks, both on the stack and on the heap; functions from *printf* family accepting input arguments as format strings; and errors related to dynamic memory allocation, such as freeing an already freed pointer. Attacks exploiting these vulnerabilities are rather complex and require deep understanding of underlying architecture, operating system, and the application under attack. In this chapter we give a short description of each vulnerability and the corresponding attack, and provide a detailed walk-through example for format string vulnerability.

# 2.1 Stack-Based Buffer Overflow Attacks

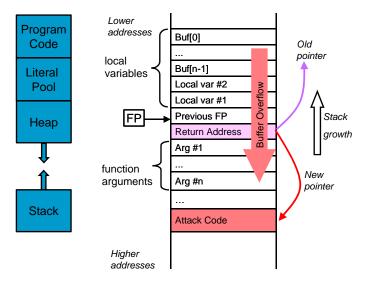

The mechanism of stack-based buffer overflow attacks, so-called "stack smashing," is probably the most widely known code injection mechanism [1, 11, 12]. Figure 2.1 illustrates one such attack: a function accepts untrustworthy values into a local buffer, which is stored on the stack. In most architectures, the direction of the stack growth is opposite to the direction of memory address growth, so if we overflow a buffer on the stack over its limits, we can overwrite any location on the stack in the address space after the beginning of the buffer. One such location holds the return address of the vulnerable function. Hence, if that function does not verify whether the length of the input exceeds the buffer size, an attacker might overflow the buffer to insert the malicious code and overwrite the return address with the address of the malicious code.

Stack smashing is probably the most exploited code injection attack, since an attacker knows that a return address is somewhere near the local function variables, and only needs to probe to find its exact location.

Figure 2.1 An illustration of a buffer overflow attack on the stack

## 2.2 Heap-Based Buffer Overflow Attacks

Buffer overflow vulnerabilities are not limited to buffers on the stack. Heap-based buffer overflow attacks are another attack category that exploits buffer overflows [2]. Let us assume that a buffer is stored on the heap in relative proximity to a code pointer, e.g., a function pointer. If that buffer accepts input without length verification, it may overwrite the function pointer with the address of attacker's choice, where the same or other buffer overflow attack stored the malicious code.

#### 2.3 Format String Attacks

Format string attacks exploit the ability of functions from the *printf* family to actually accept an input argument as a format string, for example by writing *printf(string)* instead of *printf("%s", string)* [3, 13]. The *printf* function interprets its first argument as a format string, and scans the format string looking for special format characters such as %d, %x, %s, etc. These characters specify the type of arguments to be retrieved from the stack and the corresponding output format. If an attacker can pass format strings to the *printf* function, he or she can exploit the *printf* mechanism to read the content of any memory location. This is a so-called *read attack*, which may be used to gain knowledge to mount the actual *write attacks*, such as stack smashing.

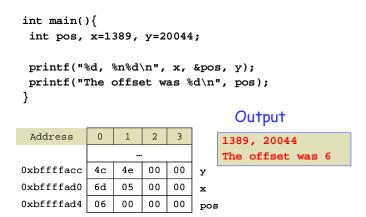

Allowing user-defined format strings also enables write attacks, based on the %n format character. If %n is encountered in the format string, the number of characters output before %n is stored at the address passed as the next argument. Figure 2.2 shows one such example: in the first *printf* call, the number of characters output before %n is 6: 4 digits of x, a comma, and a space. The value 6 is stored in the variable *pos*, as shown in the memory layout. The use %n actually results in storing the number of characters that should have been output, not the actual count of characters that were output. For example, the *snprintf* function writes no more than *size* characters to the string *str*, where both *str* and *size* are arguments of *snprintf*. Let us assume that the size of a string buffer *buf* is 20. Then the function call *snprintf* (buf, *sizeof*(buf), "%.100d%n", x, &pos) will store 100 in the variable *pos*. An intelligent use of %nenables the attacker to write any value to almost any address in the program space.

Figure 2.2 An illustration of the use of the %n format character

#### 2.4 Integer Error Attacks

Various integer errors that can compromise the system safety include unsigned integer overflow and underflow, precision error, and integer comparison [4]. A code injection attack cannot be based only on integer errors, but these errors can enable another type of attacks.

For example, overflow of an unsigned integer actually causes storing by modulo: a one-byte unsigned *char* variable can hold values 0-255, so the value 256 will be stored as 0, 257 as 1, etc. Let us assume that such a variable is used for buffer allocation and that it is overflowed. For instance, we want a buffer of 257 bytes, but the variable that controls dynamic buffer allocation is an *unsigned char*. Instead of 257 bytes, the size of the buffer is 1 byte. A "safe" function that stores data in the buffer may even verify whether the output exceeds the allowed values. However, the allowed value is 257 bytes, and the allocated size is only 1 byte. Here is an opportunity for a heap-based buffer overflow as explained before.

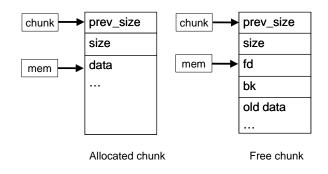

#### 2.5 Double free() attacks

To understand the principle of double *free()* vulnerabilities, we must first understand how dynamic memory allocation and deallocation work. Dynamic memory management information is usually kept together with the actual allocated memory chunk. Figure 2.3 shows the fields in allocated and free memory chunks, when using the GNU C library [14]. An allocated chunk has *prev\_size*, *size*, and *data* fields. The *prev\_size* field defines the size of the previous chunk if it is free (i.e., not allocated), or it belongs to data field of the previous chunk. The *size* field defines the size of the current chunk and also includes some status bits. The actual data is stored in the *data* field, and the pointer to data *mem* is what is returned by *malloc()*. When a memory chunk is freed, it is linked to a doubly linked list of all free chunks of the similar size, so it also has fields *fd* (pointer to a chunk forward in the list) and *bk* (pointer to a chunk backward in the list). If one of its physical neighbors is free, these two chunks are merged into one larger chunk. The linked list of free chunks is ordered by size, so that a chunk with the same size as some chunk in the list is inserted before that chunk, and all relevant forward and backward fields are set accordingly. The list is re-linked when a chunk is allocated by using a macro *unlink()*.

When a chunk C1 is freed twice, its bk and fd fields both point to itself, if there was no merging to a larger chunk between two calls to free() [5, 15]. When a program now needs to allocate a chunk of the same size as C1, the C1 will be unlinked from the list of free chunks and user data will be written in the field *data*. However, since C1 points to itself, it will not be really unlinked, so first eight bytes of *data* are actually *bk* and *fd*. Hence, an attacker might overwrite the *fd* and *bk* with addresses of his/her choice.

Next time when a chunk of C1 size is requested, unlink() will cause the content of bk field to be written at the address stored in fd plus offset of 12 bytes. One option is to overwrite a return address with the address of injected code in the data field. Therefore, exploiting the double *free()* vulnerability the attacker may satisfy both conditions for code injection attacks – inject the code and change a code pointer.

Figure 2.3 Allocated and free memory chunk organization, GNU C library malloc()

#### 2.6 A Format String Attack Example

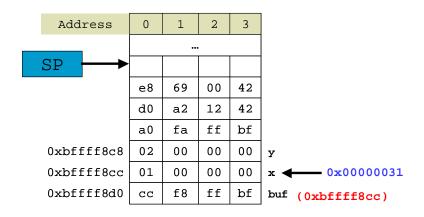

Figure 2.4 illustrates the effect of format string attack on a variable named x, which is set to 1 and not changed by any of the program instructions. The code in Figure 2.4 is slightly modified code from [3]. This attacks exploits the use of *snprintf()* with no specified format string. If the input argument argv[1] does not contain format characters, it is treated as a string, and its *sizeof(buf)* characters are simply copied to the string buffer *buf*. However, any format character will cause a value to be popped from the stack and stored in the *buf*. If we know the address of the variable x, we can change the value of x by using an input string that includes both the address of x and the *%n* format character. One way to do it is to store the address of x at the beginning of the buffer *buf*, and to include enough format string characters so that the argument for *%n* is read precisely from the *buf* beginning.

```

#include <stdio.h>

int main(int argc, char **argv){

char unsigned buf[96];

int x, y;

if(argc != 2) exit(1);

x=1; y=2;

snprintf(buf, sizeof buf, argv[1]);

buf[sizeof(buf) - 1] = 0;

printf("buffer (%d): %s\n", strlen(buf), buf);

printf("x is %d/%#x (@ %p)\n", x, x, &x);

printf("y is %d/%#x (@ %p)\n", y, y, &y);

printf("buffer[3:0]: %2x%2x%2x\n",

buf[3], buf[2], buf[1], buf[0]);

return 0;

}

```

Figure 2.4 An example of a vulnerable program

Let us assume that the x is stored at the address 0xbffff8cc (Figure 2.5). "Above" x on the stack are stored y and some other three values, and the *buf* starts below x. The input string xccxf8xffxbf.s08x.s08x.s08x.s08x.s08x.s08xsm will cause the following to happen. First, <math>0xbffff8cc will be stored in *buf[0:3]*. Then, five integer values will be popped from the stack and stored to *buf*, starting from the location below the stack pointer SP (this is the stack pointer when *snprintf()* starts to execute). Finally, the number of stored characters as specified by the format string will be stored to the address popped from the stack, i.e., the address of x stored at the beginning of the *buf*. Since the format string specifies writing of 49 characters before n (4+9\*5), the value of x will be changed to 49, as seen in the program output. Note that we used perl for input, since the address of x in hexadecimal form could not be specified when program was executed interactively under RedHat 7.0 Linux.

# Input

```

perl -e 'system

"./fmtme","\xcc\xf8\xff\xbf.%08x.%08x.%08x.%08x.%08x%n"'

```

# Output

```

buffer (49): Ìøÿ¿.420069e8.4212a2d0.bffffaa0.00000002.00000001

x is 49/0x31 (@ 0xbffff8cc)

y is 2/0x2 (@ 0xbffff8c8)

buffer[3:0]: bffff8cc

```

#### snprintf(buf,96,

```

"\xcc\xf8\xff\xbf.%08x.%08x.%08x.%08x.%08x%n");

```

Figure 2.5 Malicious input and the corresponding output for the above program, and the stack content (SP –stack pointer)

#### **CHAPTER 3**

# EXISTING TECHNIQUES FOR DETECTION AND PREVENTION OF CODE INJECTION ATTACKS

"Don't always follow the crowd, because nobody goes there anymore; it's too crowded." Yogi Berra

Techniques for countering code injection attacks can be classified in two broad categories: those that are completely software-based and those that require some hardware support. The software techniques can be further classified into static techniques and dynamic techniques. Static software-based techniques try to find possible security vulnerabilities in the code, so they can be corrected before the release version of the code. Dynamic software-based techniques augment the code so that in run-time an attack can be detected, prevented, or made very difficult, depending on a particular technique. Younan et al. survey a large number of software-based techniques [15], and Cowan et al. give a qualitative assessment of several buffer-overflow defenses [16, 17]. More recent hardware-aided techniques are less often studied. The goal of this chapter is to give an up-to-date survey of existing techniques for prevention and detection of code injection attacks.

#### 3.1 Static Software-Based Techniques

Static code analysis can find a significant number of security flaws and suggest where changes in the code should be made. However, the problem of static analysis is generally undecidable [18], so it is virtually impossible to discover all vulnerabilities in any given program by automated static analysis alone. Completely automated tools for detection of security-related flaws must choose between precise but not scalable analysis and lightweight analysis that may produce a lot of false positives and false negatives. The need for precise automated analysis can be alleviated if programmers manually add specially formulated comments about program constraints, but such techniques put an additional burden on programmers. Moreover, one can argue that adding program constraints may be as error-prone as programming. Table 3.1 lists static software-base techniques aimed to discover potential security defects, including the possibility of code injection.

While the simple Unix utility *grep* can be used to find some of the known security vulnerabilities in the code [19], it is not able to make distinction between safe and unsafe use of potentially vulnerable functions, nor it can assign rank to security warnings. For example, if we want to find format string vulnerabilities, the *grep* search for *printf()* function will give all *printf()* instances, and the majority of instances will be safe.

Several tools are developed to be essentially a smart *grep*. Viega et al. developed a token-based scanning tool called It's The Software, Stupid! Security Scanner (ITS4) [20-22]. ITS4 breaks a source file into tokens and then compares tokens against a vulnerability database. The analysis results can be further refined by checking the parameters of string functions and race conditions. The report severity is reduced for function calls with constant string parameters. On the other hand, a heuristic for race condition check increases report severity if it discovers a related race condition. Willander developed a similar open-source tool called Flawfinder [23]. Flawfinder checks for Unicode constant strings, which may further reduce the number of false alarms. Another similar tool is RATS (Rough Auditing Tool for Security) [24]. DeKok developed a tool called PScan (a limited problem scanner for C source files) [25]. PScan looks only for format string vulnerabilities and it gives a warning if a format string is not a constant value.

| Technique                                      | Description                                                                               |

|------------------------------------------------|-------------------------------------------------------------------------------------------|

| ITS4 [20-22], Flawfinder [23],<br>RATS [24]    | Marks potential vulnerabilities by comparing parsed code to a vulnerability database      |

| PScan [25]                                     | Scans code for format string vulnerabilities                                              |

| BOON [26, 27]                                  | Automatically detects potential string buffer overflow vulnerabilities                    |

| Buffer Overrun Tool [28]                       | Automatically detects buffer overflow vulnerabilities by using linear programming         |

| ARCHER [29]                                    | Automatically detects memory access errors                                                |

| Splint [30-32]                                 | Finds potential vulnerabilities if annotated by programmers                               |

| Propagation of tainted qualifiers [33]         | Detects format string vulnerabilities by using a special qualifier for untrustworthy data |

| CSSV [34]                                      | Detects all string manipulation errors in the code annotated by contracts                 |

| Compiler extensions using metacompilation [35] | Detects security errors by using programmer-written metacompiler extensions               |

| Eau Claire [36]                                | Detects security errors by using error specifications and an automatic theorem prover     |

| UNO [37]                                       | Detects several types of errors, plus user-defined properties                             |

Table 3.1

Static software-based techniques

Wagner et al. propose a tool for automated detection of code that might cause overflow of string buffers and introduce a tool prototype called Buffer Overrun detectiON (BOON) [26, 27]. The problem of string buffer overflow is formulated as an integer constraint problem: a string buffer is modeled as a pair of integers, one for the current buffer length and another for the allocated size, so the tool needs to verify whether the maximum length is not greater than the allocated size. The BOON's analysis is flowinsensitive and context-insensitive. Flow-insensitive means that the order of statements is ignored, and context-insensitive means that calls to a same function from different places are not treated in different way. The authors admit they sacrificed precision in order to have a scalable tool. BOON produces a relatively high number of false positives, e.g., 40 out of 44 generated warnings for *sendmail* program are false positives. Ganapathy et al. propose a similar approach to BOON, but with more precise pointer analysis and context-sensitivity [28]. A code understanding tool is first used to generate abstract syntax trees (AST) for program expressions and points-to information, and this data is used to generate linear constraints. Constraints that cannot be solved by linear programming are then removed from the set of all constraints (variables that get an infinite value and uninitialized constraint variables). The rest of constraints are solved using two solvers based on linear programming. Finally, heuristics are used to decide whether a particular buffer can be overflowed. This approach still lacks flow-sensitivity. The authors also note that modeling constraints in terms of pointers to buffers instead of buffers can lead to false negatives.

Xie et al. proposed another tool for automatic detection of memory access errors, named ARCHER (ARray CHeckER) [29]. ARCHER uses interprocedural, flow-sensitive and context-sensitive data-flow analysis: C source code is first parsed into AST trees and transformed to a canonical representation with reduced number of syntactic constructs. The canonical representation is then used to generate a control-flow graph (CFG) for each function and an approximate program call graph. This call graph is traversed bottom-up: for each function call, the corresponding CFG is traversed using randomized depth-first search and the ARCHER solver module is called to evaluate conditional expressions and verify whether memory accesses are unsafe. The tool gives warnings for unsafe memory accesses. Although ARCHER can discover more errors and give less false positives when compared to BOON, it still cannot reliably discover all memory access errors. It does not handle C string operations and does not track function pointers.

The need for precise automated analysis can be alleviated if programmers add specially formulated comments about constraints. Larochelle and Evans propose one such tool called Splint [30-32]. Splint is an extension of LCLint, an annotation-assisted lightweight static checking tool, developed by Evans et al. [38]. Function preconditions and postconditions can be stated using *requires* and *ensures* clauses. Within these clauses programmers may specify minimum and maximum buffer indices that can be read or written to: *maxSet, minSet, maxRead*, and *minRead*.

Shankar et al. propose a tool for detection of format string vulnerabilities [33], built on the top of *cqual*, an extensible type qualifying framework for language C [39]. The authors propose an additional

C qualifier, *tainted*, for data that cannot be trusted. The tool then analyzes how tainted data propagates through the program and gives a warning if tainted data is used as a format string.

In a recent study, Dor et al. propose a tool for detection of all string manipulation errors with very few false positives, CCSV (C String Static Verifier) [34]. While the previous work by the same authors discussed a similar algorithm with certain limitations [40], CCSV is able to find all such errors. It can handle all C constructs, including multi-level pointers, multidimensional structures, and pointer arithmetic. However, this approach requires that the potentially vulnerable functions are annotated with so-called contracts, including pre-conditions, post-conditions, and potential side effects. CCSV reports an error when a specified post-condition is not guaranteed to hold. The authors also propose algorithms for automated strengthening of post- and pre-conditions, reducing the burden placed on the programmer, but at the cost of increased imprecision.

Instead of annotating the code, a programmer can write compiler extensions that describe potential security errors. Ashcraft and Engler propose to use the metacompilation approach to look for security errors in the code [35]. With metacompilation a programmer can easily add a high-level checking rule to the compiler. The authors use belief inference approach to detect incomplete rule specifications. A range checker extension is used to demonstrate the metacompiler approach. The range checker finds errors in the Linux kernel code where the integer data from untrustworthy sources is used without first being checked.

Chess proposes another code checker, named Eau Claire [36]. Similar to the metacompilation approach, Eau Claire requires specifications of security vulnerabilities it is supposed to find. For each function, the function code and security specifications are translated to a series of verification conditions, which are then used as an input to an automatic theorem prover. A disproved theorem means that the corresponding function violates its security specifications.

Holzmann proposes a code checker named UNO [37]. The author extends an open-source C parser to generate control-flow graphs and check the code for the use of uninitialized variables, nilpointer dereferencing, and out-of-bound array indexing. UNO can also check for user-defined properties, where property definitions consist of actions and queries.

The authors of the static code analysis techniques rarely give quantitative comparisons of their techniques with other approaches. Wilander compared five static tools, ITS4, Flawfinder, RATS, BOON,

and Splint [41]. His test cases are based on 20 vulnerable functions from the ITS4 database and consist of 21 safe and 23 unsafe function calls with possibilities of buffer overflow and string format errors. Not surprisingly, "smart *grep*" techniques generated over 50% false positives and very few false negatives. Zitser et al. compared ARCHER, Boon, Splint, UNO and a commercial tool Polyspace C Verifier [42]. Test cases are based on known buffer overflow vulnerabilities and the corresponding code patches extracted from real applications, since the compared techniques were not able to process the complete code of *sendmail* and similar vulnerable programs. Splint and Polyspace were able to find a significant number of errors, but all tools gave a very high number of false warnings.

#### 3.2 Dynamic Software-Based Techniques

Precise static analysis and high coverage testing techniques can reduce the number of security vulnerabilities, but they can rarely solve all potential problems before the code is released. Dynamic software techniques aim to prevent or detect attacks in run-time. We can distinguish several groups of these techniques. The largest group encompasses techniques that automatically add run-time checks for security vulnerabilities to code (Table 3.2); some of these techniques are designed only for testing purposes, or target only one type of attack (Table 3.3). Several "safe dialects" of language C prevent code injection attacks by restricting the use of unsafe constructs, static analysis, run-time checks, and changes in memory management (Table 3.4). Various obfuscating techniques make vulnerability exploits more difficult (Table 3.5). Another group consists of various monitoring techniques (Table 3.6). Finally, some portions of the memory address space can be made non-executable with operating system support, thus preventing the execution of injected code stored at those addresses. Most of dynamic software techniques require program recompilation, so they are not readily applicable to legacy software. These techniques essentially increase the number of executed instructions, so they incur a significant performance overhead.

| Technique                                                                                | Description                                                                                   |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| bcc [43]                                                                                 | Extended pointers are used to checks bounds on pointer dereferences and array accesses        |

| RTCC [44]                                                                                | Similar approach as bcc                                                                       |

| Safe-C [45]                                                                              | Safe pointers enable detection of both spatial and temporal memory access errors              |

| Guarding [46]                                                                            | Run-time checking is decoupled from the original computation                                  |

| Backward-compatible bounds checking [47]                                                 | Unchanged pointer representation                                                              |

| Type-assisted run-time checks [48]                                                       | Run-time checks are based on type information stored in<br>"mirror" memory                    |

| Type-assisted dynamic buffer overflow detection [49], TIED+LibsafePlus [50]              | Target only buffer overflows                                                                  |

| Fail-Safe ANSI-C Compiler [51]                                                           | A memory-safe implementation of full ANSI-C                                                   |

| CRED [52]                                                                                | Detect buffer overflows of user-supplied string data                                          |

| Optimized bounds checking using metadata [53]                                            | Information about pointers is kept separated from the pointers                                |

| Boundless memory blocks [54]                                                             | Allows program to continue after an out-of-bound write, by storing it in a hash table         |

| Appropriate location bits [55]                                                           | "Unsafe" pointers may point only to locations designated as<br>appropriate in "mirror" memory |

| Purify [56], STOBO [57], detection of<br>input-related security faults [58],<br>SFI [59] | Testing tools                                                                                 |

### Table 3.2 Techniques that instrument code to verify run-time bounds

| StackGuard [60], StackShield [61],<br>RAD [62, 63], SSP [64] | Defense against stack smashing                          |

|--------------------------------------------------------------|---------------------------------------------------------|

| Libsafe, Libverify [65]                                      | Defense against stack smashing implemented in libraries |

| HEALERS [66, 67]                                             | Detects heap-based buffer overflows                     |

| Modified dlmalloc() [68]                                     | Protects dynamic allocation information                 |

| FormatGuard [13]                                             | Detects format string attacks                           |

Table 3.4"Safe dialects" of C

| Vault [69, 70]     | Enables resource management protocols in source code;<br>supports region-based memory management                 |

|--------------------|------------------------------------------------------------------------------------------------------------------|

| Cyclone [71, 72]   | "Unsafe" C features replaced by 'safe" extensions; supports garbage-collection or region-based memory management |

| CCured [73]        | Additional pointer types: safe, sequence, dynamic; garbage-collection                                            |

| Control-C [74, 75] | Restricts dynamic memory allocation and pointer arithmetic;<br>region-based memory management                    |

Table 3.5Obfuscation techniques

| ASLR [76, 77], TRR [78]                    | Randomizes base addresses of memory regions                                                  |

|--------------------------------------------|----------------------------------------------------------------------------------------------|

| Randomization of system call mappings [79] | System call mappings are randomized in linking time or before loading using binary rewriting |

| Code relocation [80]                       | Randomizes the order of variables and routines,<br>and uses random stack frame padding       |

| Code randomization [81]                    | Scrambles each byte of code                                                                  |

| PointGuard [17]                            | Encrypts code pointer values                                                                 |

| Monitoring systems calls behavior [82],<br>[83], [84], [85], [86] | An attack is detected when the monitored system call sequence<br>deviates from the expected one                      |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Monitoring performance register values [87]                       | An attack is detected when the monitored program deviates from<br>its performance signature                          |

| Janus [88]                                                        | Untrusted applications are executed within a process-tracing framework, which allows or denies system call execution |

| Reference monitor [89]                                            | Critical system calls are instrumented with access control tests                                                     |

| Program shepherding [90]                                          | Security policies are enforced by monitoring control flow transfers                                                  |

Table 3.6 Program monitoring techniques

Bcc, a source-to-source translator for inserting boundary checks was proposed as early as 1983, by Kendall [43]. The source code is transformed so that a checking function is called on each pointer dereference and array access. These function calls are to a separate run-time package. Checking functions verify whether an array access is within the array bounds, a null pointer is dereferenced or pointer access is not properly aligned; pointer arithmetic operations are checked for overflows. Pointers are converted to pointer structures: one such structure contains lower and upper bounds of the object that pointer is pointing to. Bcc also adds function wrappers to vulnerable functions. The reported slowdown is about 30 times.

The run-time checking compiler (RTCC) implements bcc as a part of the compiler front-end, in order to reduce its execution overhead [44]. It also gets rid of some bcc checks as too restrictive or unlikely errors, e.g., pointer arithmetic overflow. Since the size of a pointer structure is three times larger than the size of a "normal" pointer, a "fat" pointer must be reduced to its normal size before being passed to a system call. RTCC solves this problem by encapsulating all system calls so that the boundary information is added or removed as needed. Encapsulation wrapper also verifies that character string arguments are terminated with a null character within bounds. C libraries are recompiled with RTCC, so there is no need for encapsulation of library calls. RTCC-compiled code runs about 10 times slower then original code. A similar project is called Bounded Pointers [91].

Austin et al. propose a source-to-source translator technique called Safe-C that detects not only the spatial memory errors such as accesses outside an object's bounds, but also the temporal errors, such as

accesses outside an object's lifetime [45]. To achieve this level of detection, Safe-C extends pointer representation even more than bcc/RTCC: a safe pointer structure consists of pointer value, base address, size, storage class, and capability. Storage class can be Heap, Global, or Local; it is used to detect errors in pointer deallocation. Capability is used to detect temporal errors. When a safe pointer is allocated, it is assigned a unique capability value, which is stored into an associative table and deleted from the table after pointer deallocation. Global objects and invalid pointers have special capability values. Calls to *malloc()* and *free()* are performed through function wrappers, which set/destroy capability values. Some checks can be avoided either by compile-time or run-time optimization. Even with optimization, Safe-C can incur a significant performance overhead (up to 6 times for considered benchmarks), so it is still not suitable for release software.

With the guarding technique, Patil and Fischer try to reduce the performance overhead of bound checking by decoupling run-time checking from original computation [46]. This approach creates objects called guards with similar properties as safe pointers in Safe-C [45]. Source-to-source translation adds guard arguments to functions with pointer arguments. The authors argue that programs with run-time checks are mostly used to find errors, and not to perform actual computations. Hence, they propose to reduce the code by deleting computations not relevant to guarding and to run such program before or after the original program. If a program is running on a multiprocessor system, checking is performed by a shadow process executing on an idle processor, thus further reducing the overhead. In this case the main process is slowed down up to 10%, due to interprocess communication.

Jones and Kelly propose a run-time bounds checking technique that is backward compatible, i.e., instrumented programs can be linked with uninstrumented libraries [47]. This is achieved by not changing the representation of pointers. Information needed for bounds checking is not kept as a pointer extension, but in a separate objects table. Object list is stored as a splay tree, which is a binary tree where frequently used nodes migrate towards the top. The authors report 5-6 times slowdown for most considered programs.

Loginov et al. propose a checking technique based on type information [48]. The type of each object can be unallocated, uninitialized, integral, real, or pointer; each element of structures and arrays has its own type tag. Type information is stored in a "mirror" of memory used by the program, so that each

byte of used memory has a corresponding 4 bits in the "mirror," describing object's type and size. The goal of this technique is to be used in debugging, since the reported slowdown can be more than 100 times.

Lhee and Chapin propose a technique that detects only buffer overflows, so it has lower performance overhead than previously described techniques [49]. Automatic and static buffers are described by an additional data structure generated by a compiler extension, and information about dynamically allocated buffers is kept in a table. Range checking is performed by functions in a shared library. This approach cannot detect the overflow of buffers allocated with *alloca()* and variable-length automatic arrays. A similar recent solution that works with binary files is proposed by Avijit et al. [50]. The authors propose a buffer overflow defense based on the use of two tools, TIED (Type Information Extractor and Depositor) and LibsafePlus. TIED extracts buffer information from a binary file compiled with –g option and writes in a new ELF section; this information is used by wrapper functions provided in LibsafePlus. Maximal reported execution slowdown is 2.4.

Oiwa et al. propose the Fail-Safe ANSI-C compiler, which fully supports ANSI C [51]. This approach is also based on extended pointer representation. A "fat" pointer is described by the base address of a memory region, offset in that region, and a cast flag. If a pointer has its cast flag set, it may refer to a value of different type than the pointer's static type. In the proposed implementation both pointers and integers occupy two machine words, one word for base and cast flag bit and another for offset. A value of an integer is stored in the offset field. This approach enables casting from a pointer to an integer and back to a pointer. The reported slowdown is up to 8 times.

Ruwase and Lam propose the C Range Error Detector (CRED), which detect buffer overflows with lower overhead than previous techniques [52]. CRED is implemented on the top of the technique presented by Jones and Kelly [47], with several improvements. It allows program manipulations of out-of-bounds addresses that do not result in buffer overflows, by creating an out-of-bound object (OOB) for every out-of-bound address value in a special OOB hash table. The performance overhead is reduced by verifying only user-supplied string data. The resulting approach detects all buffer overflows in tests described by Wilander and Kamkar [92], with maximum overhead of 130%.

Xu et al. propose a more efficient technique for detection of both temporal and spatial memory errors [53]. This approach does not handle customized memory management functions, cast of integers to

pointers, and cast of pointers to structures to pointers of structures of unrelated type. Pointer-related information (metadata) is kept separated from the pointer, unlike various fat pointer techniques. Metadata is similar to information kept in Safe-C [45]. Average performance slowdown with various optimizations is 2.21 times, with maximum slowdown 3.37 times. Optimizations include splitting metadata into header and info structures, eliminating unnecessary operations on the stack capability store, and converting metadata structures to individual variables.

Most defense techniques cause programs to abort execution when a buffer overflow is detected. Rinard et al. propose an approach called boundless memory blocks, which prevents harmful effects of buffer overflows, but allows programs to continue execution [54]. The values of out-of-bounds writes are stored in a hash table, so they can be read by out-of-bounds reads. In order to limit the amount of memory occupied by the out-of-bound writes, the hash table is implemented as a fixed size LRU cache. The checking scheme is based on techniques proposed by Jones and Kelly [47] and Ruwase and Lam [52]. Reported slowdown ranges from negligible for Apache HHTP server processing requests to 8.9 times for composing mail in Pine.

Yong and Horwitz propose a technique that keeps track of all locations that may be pointed to by an unsafe pointer in a memory "mirror" [55]. Each memory byte has one bit mirror tag indicating whether it belongs to appropriate or inappropriate locations. Unsafe pointers and locations they can legitimately point to are determined by static analysis. The location tag is set to appropriate when that location is allocated, and reset after deallocation. Write operations via unsafe pointers and *free()* are instrumented to verify the appropriate tag. Maximum reported slowdown is 8.02.

High overhead of most bounds-checking techniques limits their use in release code versions, but they can be successfully used for testing. Several techniques are designed particularly for testing purposes. Widely used commercial testing tool Purify may detect security vulnerabilities related to memory access errors, such as heap-based buffer overflows [56]. Haugh and Bishop propose a testing tool called STOBO (Systematic Testing of Buffer Overflows) which detects potential buffer overflows during tests with regular data [57]. STOBO generates one type of warnings when both the source and destination are statically allocated, and another type when the destination is dynamically allocated; it reports an error when source is dynamically allocated, and destination statically allocated. Larson and Austin propose a tool for detection of input-related security faults, which also does not require "unsafe" test data [58]. All external input variables and derived variables are shadowed with a state variable: e.g., an integer is shadowed by a variable that stores the lower and upper variable bounds, and a string shadow variable encompasses maximum possible size of the string and null character information. Bounds are adjusted by control decisions (e.g., loops) and arithmetic operations. The tool generates an error report if any of values within the bounds causes can jeopardize security. Ghosh et al. propose to apply software fault injection (SFI) to discover potential security flaws [59].

Some dynamic techniques focus on only one type of attack targets: return addresses on the stack [60-65], format strings [13], or dynamically allocated memory [66-68]. Cowan et al. propose a compiler extension named StackGuard which detects or prevents changes of the return address on the stack [60]. With StackGuard detection, the function prologue places a dummy value, the so-called canary, between the return address and the rest of the stack. The canary is verified in the function epilogue before return execution. A buffer overflow attack that overwrites the return address must also overwrite the canary, so an attack is detected if the value of the canary has changed. The canary value may be randomized to prevent attack strings to overwrite it with the original value; however, even randomization does not prevent a write buffer overflow attack following a read attack. The overhead of canary mechanism is 125% for the worst-case function call, so it is very low for complete applications. StackGuard prevention of return address change is based on the debugging tool MemGuard, which protects values by marking the corresponding virtual pages as read-only and then emulating writes to non-protected values on those pages. Even with an optimization that uses Pentium debug registers to protect only last four return addresses, this approach has a significant slowdown.

StackShield also protects from stack smashing [61]. It applies two methods, Global Ret Stack and the Ret Range Check. In Global Ret Stack, return addresses are copied to a dedicated array in function prologue and restored from that array in function epilogue. The number of protected nested function calls is limited by array size. With Ret Range Check, a return address is copied to a global variable at the beginning of data segment. Newer versions of StackShield can also detect overwriting of function pointers. StackShield modifies assembly files, although it may be part of compiler chain. Chiueh and Hsu propose the Return Address Defender compiler patch (RAD) [62]. The RAD technique is similar to the StackShield: return addresses are copied to the Return Address Repository (RAR) in the data segment. To protect the RAR from being overwritten by attackers, the authors propose two RAD implementations, MineZone RAD and Read-Only RAD. With MineZone RAD, the RAR area is in the middle of a global array, with the array beginning and end set as read-only areas by *mprotect*() system call. A buffer spilling into RAR will cause a trap, but MineZone will not prevent attacks writing directly into the RAR. With Read-Only RAD, the whole RAR is read-only except when return addresses are written into it. Read-Only RAD completely protects the RAR, but at the price of increased overhead for set/remove of read-only protection. MineZone RAD increases the execution time of two considered benchmarks 1.02 and 1.3 times, and Read-Only RAD 18 and 43 times. RAD handles the *setimp()/longimp()* issue in the following way: if the address on the top of the RAR does not match the return addresses are popped from the RAR until the correct address is found or the RAR bottom is reached. Prasad and Chiueh propose a way to implement RAD as a binary rewriting technique [63].

Etoh and Yoda propose a stack-smashing defense compiler extension called the Stack Smashing Protector (SSP) [64]. SSP places a pseudo-random guard value on the stack to protect a return address and the corresponding frame pointer, similar to the canary in StackGuard. In addition, SSP reorders local variables so that buffers are placed after pointers. It also protects pointers in function arguments by copying them to an area preceding local buffer variables. To reduce overhead, SSP instruments only functions that have string buffers as arguments or local variables. For three considered applications, SSP overhead ranges from 0 to 4%, while StackGuard overhead for same applications is 0-8%. SSP cannot prevent certain types of buffer overflows: for example, a buffer may overflow into a pointer variable if both are part of the same structure, since the order of structure elements cannot be changed.

One limitation of StackGuard and similar techniques is that they require source or assembly code. Baratloo et al. propose a transparent run-time defense against smashing attacks that works with precompiled binaries [65]. The transparent defense is based on two dynamically loadable libraries, libsafe and libverify. Libsafe implements "safe" versions of functions which can cause buffer overflows, such as strcpy(). The size of buffers in those functions is limited by the size of the corresponding stack frame, so they can never overflow beyond the frame pointer. Libverify protects all return address as the StackGuard does, but canary code is completely contained within the library. Both libsafe and libverify rely on preload feature of ELF libraries to load with processes that need protection. For each function in a protected process, the *\_\_init()* function of libverify copies function code to heap, and replaces first instruction in original function and last instruction in the copy with jumps to wrapper entry/exit routines. The entry wrapper writes a canary value on the canary stacks and jumps to function copy, and the exit wrapper verifies the canary. The canary value is the return address itself, as in StackShield. The canary stack is protected by read-only regions like MineZone RAD. Libverify has slightly larger performance overhead than StackShield.

Wilander tested StackGuard, StackShield, ProPolice (an old name for SSP), Libsafe, and Libverify with 20 buffer overflow benchmarks [92]. Although all these techniques effectively protected return addresses, they were not able to detect/prevent other buffer overflow attacks, such as buffer overflow on the heap. The best technique, ProPolice, missed 9 of 20 attacks.

Fetzer and Xiao propose transparent defense against heap smashing attacks by using a dynamically loadable C function wrapper called HEALERS [66]. HEALERS wrapper intercepts C functions that could be used to write to the heap and performs boundary checking of function arguments. Wrapper for *malloc()* records position and size of allocated memory in an internal table, and wrapper for *free()* deletes the corresponding table entry. The overhead of HEALERS is up to 10% for considered applications. The authors later extended the HEALERS toolkit to automatically discover problems in C libraries using automated fault injection experiments and to support flexible wrapper generation [67].

Heap-based buffer overflows may target memory management information, which is stored at the beginning of each memory chunk. Robertson et al. propose to protect this information by storing a canary value when a chunk is allocated, and verifying it when the chink is freed [68]. The canary is the checksum of the chunk header seeded with a global random value, initialized during process startup. The proposed approach is implemented as a library patch for glibc library. Memory allocation functions in glibc are implemented using *dlmalloc*, so the authors needed to modify only this routine. For the worst-case microbenchmark, the execution slowdown is 28%. Performance impact for real applications is negligible.