# AN IMPLEMENTATION OF CHACHA20 STREAM CYPHER IN ALL-PROGRAMMABLE SoCs

by

# IGOR SEMENOV

# A THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in The Department of Electrical and Computer Engineering to The School of Graduate Studies of The University of Alabama in Huntsville

## HUNTSVILLE, ALABAMA

2020

In presenting this thesis in partial fulfillment of the requirements for a master's degree from The University of Alabama in Huntsville, I agree that the Library of this University shall make it freely available for inspection. I further agree that permission for extensive copying for scholarly purposes may be granted by my advisor or, in his/her absence, by the Chair of the Department or the Dean of the School of Graduate Studies. It is also understood that due recognition shall be given to me and to The University of Alabama in Huntsville in any scholarly use which may be made of any material in this thesis.

Igor Semenov

(date)

### THESIS APPROVAL FORM

Submitted by Igor Semenov in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate of the work described in this thesis. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering.

|                           |        | Committee Chair  |

|---------------------------|--------|------------------|

| Dr. Aleksandar Milenković | (Date) |                  |

| Dr. David Coe             | (Date) |                  |

| Dr. Jeffrey Kulick        | (Date) |                  |

| Dr. Ravi Gorur            | (Date) | Department Chair |

| Dr. Shankar Mahalingam    | (Date) | College Dean     |

| Dr. David Berkowitz       | (Date) | Graduate Dean    |

#### ABSTRACT

### School of Graduate Studies The University of Alabama in Huntsville

| Degree  | Masters of   | Science       | College/Dept.   | Engineering/Electrical and |

|---------|--------------|---------------|-----------------|----------------------------|

|         | in Engineer  | ring          |                 | Computer Engineering       |

| Name of | f Candidate  | Igor Semen    | lov             |                            |

| Title   | An implem    | entation of ( | ChaCha20 stream | m cypher                   |

|         | in all-progr | rammable So   | oCs             |                            |

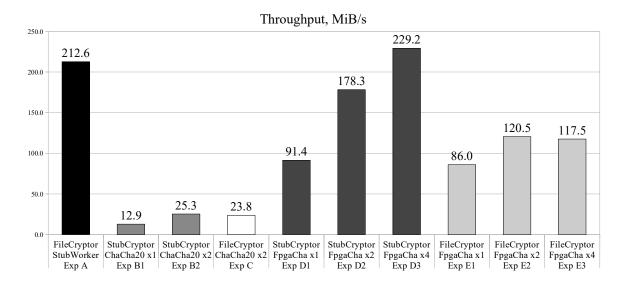

An increased reliance on services offered online is an inherent aspect of the Information Age. Such services often handle sensitive customers' data and therefore must ensure its confidentiality, for example, by using cryptographic algorithms. Some algorithms, such as AES, have long been used for this purpose, but they impose additional cost and/or performance overheads. However, new lightweight stream cyphers, such as ChaCha20, are emerging as a faster alternative to conventional algorithms without sacrificing the security. Development of hardware cryptographic accelerators has been widely used to reduce performance overheads of cryptographic algorithms. In the past, this approach was extremely expensive, but nowadays, widely available all programmable SoCs make it more affordable. In this thesis, we present an IP-core for ChaCha20 acceleration in a low-cost all-programmable SoC, Cyclone V. We describe the design of our core, consisting of a ChaCha20 accelerator and a custom DMA. We also present a software framework that employs multiple CPU cores or hardware accelerators for file encryption. We explore different configurations of this framework in order to find the optimal one. Our experiments show that two accelerators clocked at 50 MHz working concurrently provide the throughput of 120.5 MiB/s, a five-fold throughput improvement over the baseline software file encryption executed on two ARM Cortex-A9 processor cores running at 800 MHz.

Abstract Approval: Committee Chair

Dr. Aleksandar Milenković

Department Chair

Dr. Ravi Gorur

Graduate Dean

Dr. David Berkowitz

#### ACKNOWLEDGMENTS

First, I would like to thank the Department Electrical and Computer engineering for awarding me the position of a teaching assistant, which helped me to greatly improve my teaching skills and fund my education and research at UAH.

Second, I would like to express my deepest gratitude Dr. Aleksandar Milenković for serving as my advisor and providing constant support throughout this work. He has been a great inspirator and mentor for me during the last 2 years.

Additionally, I am also very grateful to Dr. Jeffrey Kulick and Dr. David Coe for serving as my committee members. Their challenging questions during the defense procedure and follow-up feedback helped me to improve this work.

I would like to sincerely thank my lab mates Mr. Ranjan Hebbar, Mr. Prawar Poudel, Dr. Mounika Ponugoti and Mr. Amirahmad Ramezani. They have been my true friends who I could always reach if I needed help with academic or life issues.

Finally, I am expressing my gratitude to my parents for their love and moral support. Special thanks goes to my wife, who treated my time-consuming work on this thesis with understanding.

# Contents

| $\mathbf{Li}$ | st of | Figures                   | х        |

|---------------|-------|---------------------------|----------|

| Li            | st of | Tables                    | xi       |

| Li            | st of | Symbols                   | xii      |

| 1             | Intr  | oduction                  | 1        |

|               | 1.1   | Technology trends         | 2        |

|               | 1.2   | Contributions             | 3        |

|               | 1.3   | Thesis outline            | 4        |

| C             | hapto | er                        |          |

| <b>2</b>      | Bac   | kground                   | <b>5</b> |

|               | 2.1   | Block vs. stream ciphers  | 5        |

|               | 2.2   | ChaCha20                  | 8        |

|               | 2.3   | Intel Cyclone V           | 13       |

|               | 2.4   | Terasic DE10-Nano Kit     | 15       |

|               | 2.5   | Avalon interfaces         | 18       |

|               |       | 2.5.1 Avalon-MM interface | 19       |

|               |       | 2.5.2 Avalon-ST interface | 20       |

|               |       | 2.5.3 Avalon interrupt    | 21       |

|          | 2.6                  | Userspace I/O device drivers                                                                                | 22 |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------|----|

|          | 2.7                  | User space mappable DMA Buffer                                                                              | 24 |

| 3        | Rel                  | ated work                                                                                                   | 26 |

| 4        | $\operatorname{Des}$ | ign considerations                                                                                          | 30 |

|          | 4.1                  | Pipelining                                                                                                  | 30 |

|          | 4.2                  | XOR stage                                                                                                   | 33 |

|          | 4.3                  | Summation stage                                                                                             | 34 |

|          | 4.4                  | Summary                                                                                                     | 35 |

| <b>5</b> | Des                  | sign description                                                                                            | 36 |

|          | 5.1                  | FpgaCha IP-core                                                                                             | 36 |

|          |                      | 5.1.1 ChaCha20 accelerator                                                                                  | 38 |

|          |                      | 5.1.2 S2M adapter $\ldots$ | 41 |

|          | 5.2                  | Software organization                                                                                       | 43 |

|          |                      | 5.2.1 Task                                                                                                  | 45 |

|          |                      | 5.2.2 Queue                                                                                                 | 45 |

|          |                      | 5.2.3 Worker                                                                                                | 46 |

|          |                      | 5.2.4 Cryptor                                                                                               | 48 |

|          |                      | 5.2.5 Queue of finished tasks                                                                               | 49 |

|          |                      | 5.2.6 Overall framework description                                                                         | 50 |

| 6        | Exp                  | periments and results                                                                                       | 53 |

|          | 6.1                  | Correctness of software and hardware                                                                        | 53 |

| R | efere | nces    |                                                            | 69 |

|---|-------|---------|------------------------------------------------------------|----|

| A | ppen  | dix A:  | Enabling FPGA-to-SDRAM bridge using U-Boot                 | 67 |

|   | 7.3   | Future  | e work                                                     | 64 |

|   | 7.2   | Result  | 55                                                         | 63 |

|   | 7.1   | What    | has been done                                              | 62 |

| 7 | Cor   | nclusio | n                                                          | 62 |

|   |       | 6.2.5   | Hardware-based file encryption throughput (Experiments Ex) | 60 |

|   |       | 6.2.4   | Hardware ChaCha20 throughput (Experiments $\mathrm{Dx})$   | 59 |

|   |       | 6.2.3   | Software-based file encryption throughput (Experiment C)   | 58 |

|   |       | 6.2.2   | Software ChaCha20 throughput (Experiments Bx)              | 57 |

|   |       | 6.2.1   | File I/O throughput (Experiment A)                         | 56 |

|   | 6.2   | Throu   | ghput evaluation                                           | 55 |

|   |       | 6.1.2   | File encryption test of the other modes                    | 54 |

|   |       | 6.1.1   | Functional testing of the reference mode                   | 53 |

# LIST OF FIGURES

### FIGURE

## PAGE

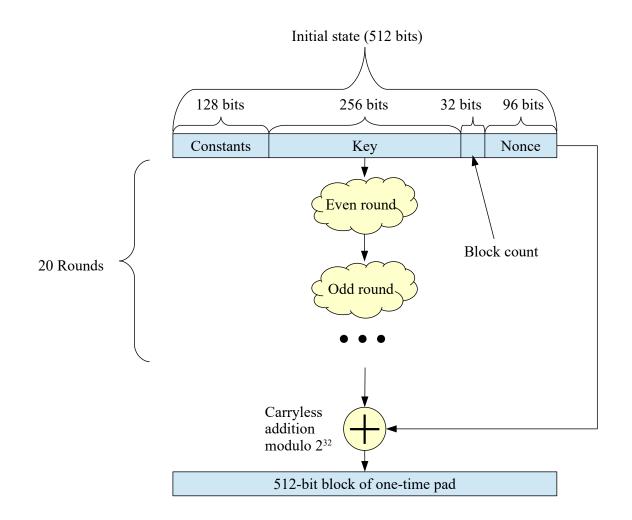

| 2.1 | Graphical illustration of ChaCha20 algorithm                                                 | 9  |

|-----|----------------------------------------------------------------------------------------------|----|

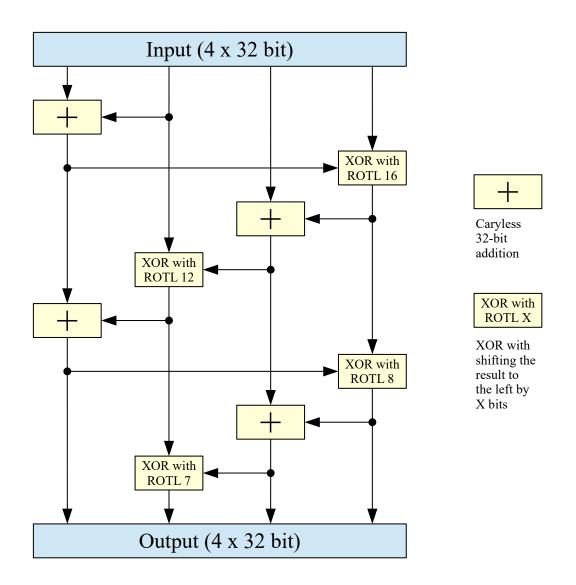

| 2.2 | Graphical illustration of ChaCha20 round                                                     | 11 |

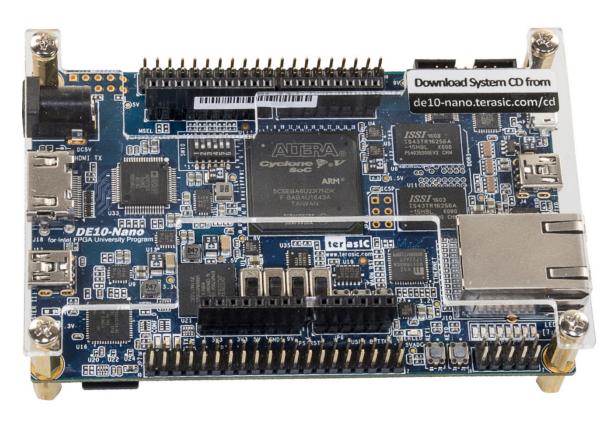

| 2.3 | Photo of DE10-nano board                                                                     | 16 |

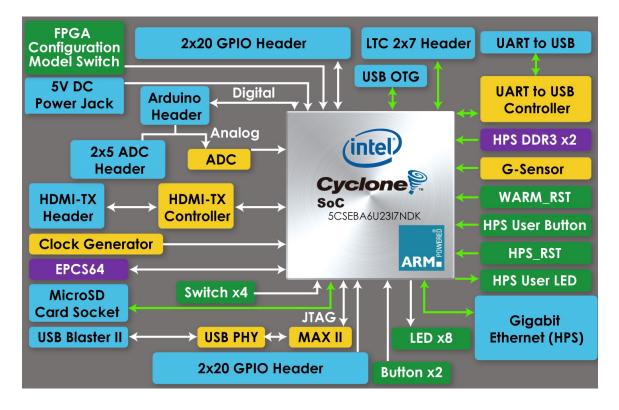

| 2.4 | Block diagram of DE10-nano board                                                             | 17 |

| 4.1 | A pipelined design vs a non-pipelined design with a feedback loop $\ . \ .$                  | 31 |

| 5.1 | Hardware components of FpgaCha                                                               | 37 |

| 5.2 | The data path of ChaCha20 accelerator                                                        | 40 |

| 5.3 | Structure of our software framework                                                          | 44 |

| 5.4 | Structure of FpgaChaWorker                                                                   | 47 |

| 5.5 | Example of the framework with 2 workers and a 6-slot queue                                   | 51 |

| 6.1 | Overall system throughput for different combinations of data producers<br>and data consumers | 57 |

# LIST OF TABLES

| TAE | PAG                                                                                     | ΞE |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.1 | Fields of ChaCha20 initial state                                                        | 10 |

| 2.2 | ChaCha20 even round input words                                                         | 12 |

| 2.3 | ChaCha20 odd round input words                                                          | 12 |

| 2.4 | Signals of Avalon-MM interface                                                          | 20 |

| 2.5 | Signals of Avalon-ST interface                                                          | 21 |

| 3.1 | Summary of the performance characteristics for various hardware cyphers                 | 28 |

| 3.2 | Summary of the resource consumption for various hardware cyphers implemented in FPGA    | 29 |

| 5.1 | Register map of ChaCha20 accelerator                                                    | 39 |

| 5.2 | FPGA resource utilization of ChaCha20 accelerator                                       | 41 |

| 5.3 | Register map of S2M adapter                                                             | 42 |

| 5.4 | FPGA resource utilization of S2M adapter                                                | 43 |

| 6.1 | Test vector for reference mode functional testing                                       | 54 |

| 6.2 | The result of the reference ChaCha20 implementation operating on the test vector        | 54 |

| 6.3 | SHA-2 hashes of files decrypted using different modes                                   | 55 |

| 6.4 | Experiments for throughput evaluation of software and hardware ChaCha20 implementations | 56 |

| A.1 | Register map of some registers of HPS                                                   | 68 |

### LIST OF SYMBOLS

### SYMBOL DEFINITION

- AEAD Authenticated encryption with associated data

- AES Advanced encryption standard

- ASIC Application-specific integrated circuit

- CSR Control and status register

- DRAM Dynamic random-access memory

- FPGA Field-programmable gate array

- HPS Hard processor system

- IP-core Intellectual property core

- IRQ Interrupt request

- LUT Lookup table

- OS Operating system

- OTP One-time pad

- RAM Random-access memory

- SoC System on a chip

- UIO User-space input/output

#### Chapter 1

#### INTRODUCTION

Data confidentiality has become especially important in the Information Age. Nowadays many services are provided online: governments, financial institutions, and e-commerce companies interact with their customers remotely. Such interaction is extremely convenient for all parties. However, service providers are required to store and transfer sensitive customer's data, which makes them a target for hacker attacks. Sometimes customer's data becomes exposed even without malicious actions, leading to data leaks. To prevent detrimental consequences of unauthorized data access, sensitive information can be encrypted using strong cryptographic algorithms. Such algorithms are usually computationally difficult, which, together with ever growing amounts of data, leads to the need of increasing the efficiency of data encryption. That is why new lightweight cryptographic algorithms are being developed. An example of such an algorithm is ChaCha20, which can outperform its conventional competitors. Additionally, the performance of the encryption process can be improved by using hardware accelerators, designed specifically to facilitate a certain cryptographic algorithm. Even though fabrication of such accelerators is extremely expensive, some technologies, such as field-programmable gate arrays, make it much more affordable.

The goal of this work is to explore any performance improvements of implementing a hardware accelerated ChaCha20 algorithm on a system-on-a-chip (SoC) platform that contains an FPGA and a CPU. We focus on file encryption in the Linux environment as the final application of our solution.

#### 1.1 Technology trends

This thesis focuses on hardware implementation of ChaCha20 cypher in the context of all-programmable SoCs. Our motivation for pursuing this topic arises from the following technological trends.

The first trend we recognize is extensive application of hardware accelerators for different tasks, including data encryption. Since strong cryptographic algorithms are usually computationally intensive, replacing their software implementations with hardware modules dramatically improves their performance. This is especially important for embedded systems where resources are limited due to size, cost, or power consumption requirements. Many companies whose products target embedded market use hardware accelerators. For example, STMicroelectronics embeds an AES cryptoprocessor in some families of their STM32 microcontrollers [1]. Texas Instruments also uses AES hardware accelerators in some of their MSP430 microcontrollers [2].

Development of new stream cyphers is another technology trend. Many cryptographic applications these days rely on block cyphers. Recently, stream cyphers started gaining more attention because they are capable of providing higher security level with the same performance. An example of such a cypher is ChaCha20 [3]. According to Langley [4] ChaCha20 shows better performance than Advanced Encryption Standard (AES) algorithm [5], a de facto industry standard for encryption.

Heterogeneous computing is one more technological trend. Heterogeneous systems may combine different types of computational units, suitable for different tasks. For example, some computers these days contain a CPU to solve general purpose tasks and a GPGPU that helps to accelerate parallelizable tasks. Another instance is all-programmable system-on-a-chip products. These devices contain a hard processor system and field-programmable gate array fabric on the same silicon die. They are capable of solving the same problems as GPGPU-based platforms, but have a more fine-grained structure that gives the developer more freedom for building a custom architecture.

#### **1.2** Contributions

This thesis presents the design and evaluation of a ChaCha20 cypher in heterogeneous all-programmable SoCs. Specifically, the thesis makes the following contributions:

- Presents a design and an implementation of an IP-core for efficient ChaCha20 computation in FPGA. To the best of our knowledge, this is the first freely available ChaCha20 accelerator for FPGA, easily connectible to an HPS.

- Describes a software framework based on the Linux environment that allows instantiation of our IP-core and its evaluation and comparison to software cyphers

running on multiple CPU cores in order to evaluate and compare performance of different configurations.

- Evaluates the performance of different configurations of our hardware accelerator, demonstrating its superiority over the software solution. The throughput of our hardware solution is 120.5 MiB/s, which is 5 times higher than the maximum throughput of a software solution running on two CPU cores.

- Identifies DRAM bandwidth as the main bottleneck, limiting the performance of our IP-core.

#### 1.3 Thesis outline

The remaining sections of this thesis are organized as follows. Chapter 2 gives background information that is essential for understanding the other sections of this thesis. Chapter 3 overviews existing work that is related to the topic. Chapter 4 explains design choices we made in order to build an efficient hardware accelerator. Chapter 5 describes the design of our IP-core for accelerating ChaCha20. It also describes our software framework for file encryption with hardware acceleration or without it. Chapter 6 lists experiments we carried out, presents their results and gives some analysis of those results. Finally, Chapter 7 summarizes the work, draws conclusions, and discusses future work. Additionally, Appendix A describes the procedure of enabling the SDRAM-to-FPGA bridge, which was essential for the practical part of this thesis.

#### Chapter 2

### BACKGROUND

This chapter contains information that is useful for better understanding of the other chapters of this thesis. First, we explain what stream cyphers are and how they are different from block cyphers. Then, we describe the stream cypher of our interest, ChaCha20. We also give some information about the platform we used for our experiments, as well as some technologies we used to implement ChaCha20 in hardware and interface our implementation to software.

#### 2.1 Block vs. stream ciphers

According to Christof Paar [6], encryption algorithms can be divided into two groups: symmetric and asymmetric. In the former, the same secret key is used to encrypt and decrypt the data, whereas for the latter, encryption and decryption keys are different.

Symmetric cryptography algorithms are subdivided into two subgroups: block ciphers and stream ciphers. In both cases a certain transformation is applied to a plaintext (the original message that needs to be encrypted), yielding a cyphertext (the encrypted message). This transformation is assumed to be irreversible in practice without knowing the secret key. The way such a transformation is applied to the plaintext is different for block and stream ciphers.

In block ciphers the plaintext is split into blocks, size of which is algorithmspecific. Then, each block of the plaintext is transformed into a block of the ciphertext by applying some encryption function as follows:

$$CB = E(Key, PB) \tag{2.1}$$

where CB is a block of the ciphertext; PB is a block of the plaintext; Key is the secret key; and E is the encryption function.

In real block ciphers each bit of CB depends of each bit of PB. Moreover, changing a single bit of PB alters CB in an unpredictable way. This property differentiates block ciphers from stream ciphers.

In stream cyphers the encryption function is applied independently to each bit of the plaintext. In other words, the encryption process is described as follows:

$$C_i = E(Key, P_i, i) \tag{2.2}$$

where  $C_i$  is the *i*-th bit of the ciphertext;  $P_i$  is the *i*-th bit of the plaintext; and E is the encryption function.

The result of E depends on the index, i, of the bit being encrypted. If E was a function of  $P_i$  only, the ciphertext would be either a bitwise inverted or non-modified plaintext. This, obviously, would give no protection at all.

Usually, the E function is implemented as a bitwise XOR operation between P and a pseudo-random number derived from Key. It is important to choose this number such that it is not shorter than P and make sure it is used only once. Moreover, it should be impossible to get Key from the pseudo-random number. Without these two properties a stream cypher cannot be secure.

As opposed to block ciphers, changing  $P_i$  in a stream cipher affects only  $C_i$ , but not  $P_j$  when  $j \neq i$ . This may give a malicious party a much better chance to attack a specific part of the plaintext by altering the cyphertext. That is why if the attacker can potentially modify the cyphertext, stream cyphers must be used together with authentication algorithms.

According to [6], currently, block ciphers are used more frequently than stream ciphers despite the fact that stream ciphers can provide similar or better performance. That is why, stream cyphers have a great potential for improving performance of cryptographic applications.

There are encryption algorithms that were designed as block ciphers, but can be turned into stream ciphers. AES [5], a de facto industry standard for symmetric encryption, is an example of such an algorithm. When used in the electronic codebook mode (ECB), it works as a block cypher. In the counter mode, AES works as a stream cypher.

The next section describes a relatively new stream cypher, ChaCha20. Even though it is less flexible than AES, because it can only be used in the stream mode, it is more efficient and secure, and its computation involves only relatively low-complexity operations. These properties make it promising for cryptographic applications, including file encryption.

#### 2.2 ChaCha20

ChaCha20 is a stream encryption algorithm proposed in 2008 by Daniel J. Bernstein. The algorithm is based on Salsa20: another encryption algorithm proposed by Bernstein earlier. According to the author, Salsa20 can be used instead of AES in applications where the confidence in the cypher's security can be sacrificed in favor of speed [7]. ChaCha20 has even better characteristics: it provides higher confidence, while being consistently faster than AES on machines without hardware accelerators [4]. These properties allowed ChaCha20 to earn recognition in the cryptographic community [3]. Moreover, the algorithm was standardized in two documents RFC7539 [8] (now obsolete) and RFC8439 [9]. The novelty of ChaCha20 and its superb characteristics make it a good candidate for hardware implementation for this research.

ChaCha20 is a classic stream cypher: it produces a stream of pseudo-random bytes (one-time pad or OTP) that is XORed with the plaintext to produce the cyphertext. Figure 2.1 demonstrates how a 512-bit chunk of such a stream is generated according to RFC8439. First, the initial 512-bit state of ChaCha20 must be formed. This state consists of a few fields that are explained in Table 2.1. Second, the initial state is transformed by 20 round functions of two types: even and odd. Each round function converts its 512-bit input into a 512-bit output. Finally, the initial state is added to the result of the last round function. To do the summation stage, both

Figure 2.1: Graphical illustration of ChaCha20 algorithm

operands are viewed as arrays of 32-bit integer numbers with 16 elements. The summation modulo  $2^{32}$  is done element-wise between the arrays. The result of the summation is used to do encryption as follows:

$$C_i = P_i \oplus PAD_i \tag{2.3}$$

where  $C_i$  is the *i*-th bit of the ciphertext;  $P_i$  is the *i*-th bit of the plaintext; and  $PAD_i$  is the *i*-th bit of ChaCha20 result.

| Name        | Bit size | Byte size | Description                                                                                                                                                                                                                               |

|-------------|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constant    | 128 bits | 16 bytes  | A constant part of the state. It is always<br>initialized with the ASCII values of the<br>characters of the following string: 'expand<br>32-byte k'                                                                                       |

| Key         | 256 bits | 32 bytes  | The secret key.                                                                                                                                                                                                                           |

| Block count | 32 bits  | 4 bytes   | A counter that starts from 0 and is incre-<br>mented to generate the next chunks of OTP.<br>There are $2^{32}$ unique values of this field, so<br>the maximum length of the entire OTP with<br>the same secrete key and nonce is 256 GiB. |

| Nonce       | 96 bits  | 12 bytes  | A unique number that can be changed to<br>generate a new OTP with the same key.<br>Using each value of nonce no more than<br>once is crucial for providing a high level of<br>security.                                                   |

Table 2.1: Fields of ChaCha20 initial state

To generate the next 512-bits of OTP, the block count field of the initial state is incremented and the process repeats.

The final result of ChaCha20 is extremely sensitive to changes of the initial state: flipping even a single bit of the input leads to an unpredictable change of the result. Moreover, despite the round functions being reversible, it is impossible to convert the result of ChaCha20 back to the initial state, because of the summation stage. This two properties make ChaCha20 suitable for stream encryption.

The round functions consist of one layer of quarter rounds, each working on 1/4 of the round's input. Figure 2.2 shows the structure of the quarter round. The input of the quarter round consists of 4 32-bit words taken from the input of the round. Even and odd rounds supply the input to the quarter rounds differently. Tables 2.2

Figure 2.2: Graphical illustration of ChaCha20 round

and 2.3 show how the input words of the even and odd rounds are supplied to their quarter rounds.

High performance of ChaCha20 can be ascribed to the fact that it is based on a few primitive operations that execute in a minimum number of clock cycles on modern 32-bit and 64-bit processors:

• Carryless addition of two 32-bit numbers:  $a + b \mod 2^{32}$ .

| Quarter round number | Input words for the quarter round |

|----------------------|-----------------------------------|

| 1                    | 0, 5, 10, 15                      |

| 2                    | 1,  6,  11,  12                   |

| 3                    | 2, 7, 8, 13                       |

| 4                    | 3, 4, 9, 14                       |

Table 2.2: ChaCha20 even round input words

Table 2.3: ChaCha20 odd round input words

| Quarter round number | Input words for the quarter round |

|----------------------|-----------------------------------|

| 1                    | 0, 5, 10, 15                      |

| 2                    | 1,  6,  11,  12                   |

| 3                    | 2, 7, 8, 13                       |

| 4                    | 3,  4,  9,  14                    |

- Exclusive OR between two 32-bit numbers:  $a \oplus b$ .

- Rotation of a 32-bit number by a fixed number of positions:  $ROTL^{n}(a)$ .

Even though having only such simple operations in an encryption algorithm may seem insecure, Bernstein points out that his operators can simulate any circuit and therefore provide the same security level as a set of more complex operations [7].

Having only such simple operations makes ChaCha20 attractive for implementation in hardware. We used Intel Cyclone V FPGA device for this purpose. The next section describes the characteristics of this device.

#### 2.3 Intel Cyclone V

Intel Cyclone V is a family of affordable field-programmable gate array (FPGA) devices. Some sub-families of Cyclone V are called System-on-a-Chip (SoC) because they combine an FPGA and an ARM-based hard processor system (HPS) on a single die. The following sub-families are available, targeting various applications with different requirements for cost and performance [10]:

- Cyclone V E lowest power, low cost, general logic and DSP applications

- Cyclone V GX additionally contain 3.125 GiB/s transceivers

- Cyclone V GT contain 6.144 GiB/s transceivers instead

- Cyclone V SE same as E but with HPS

- Cyclone V SX same as GX but with HPS

- Cyclone V ST same as GT but with HPS

The chips are manufactured using the 28 nm TSMC Low-Power technology and require only 1.1 V core voltage. The FPGA part of Cyclone V allows the engineer to build custom hardware accelerators out of basic blocks called ALMs (Adaptive Logic Modules). Each ALM contains an 8-input adaptive look-up table (LUT), 4 flip-flops, and two full adders. In addition to ALMs, Cyclone V provides digital signal processing (DSP) blocks, which include a 64-bit accumulator, a hard pre-adder supporting 18 and 27-bit modes, and cascaded output adders for systolic finite-impulse-response filters. Cyclone V also contains embedded memory blocks, each providing 10 Kibit of space in a fast dual-port static RAM (SRAM) [10]. Although the ability to reconfigure FPGA fabric introduces some overhead compared to application-specific integrated circuits (ASICs), it is ideal for prototyping and building accelerators for products with low production quantity.

The HPS part of the chip consists of an ARM-based processor, a shared multiport DRAM controller, and a few peripheral devices. These devices include a SD/MMC card controller, an Ethernet MAC, a USB OTG, a NAND Flash controller, and a DMA controller. The HPS provides additional performance boost in case the developer needs a CPU and various external interfaces in the system. Even though FPGA technology allows building an entire CPU out of ALMs and the other building blocks, it is not the most efficient solution due to the overhead inherent in FPGAs. Having the HPS eliminates this overhead. Additionally, designing a custom high-performance CPU is not a trivial task. Instead, a third-party IP-core may be purchased, but such a solution may be costly. Cyclone V gives the developer a powerful processor for a low price.

The HPS part of Cyclone V can be interfaced with the FPGA fabric through one of the following bridges:

• FPGA-to-HPS bridge. This bridge allows hardware modules implemented in FPGA to access peripherals on the HPS side. It is also possible to have coherent access to DRAM. This means that the CPU's cache will be aware of DRAM content changes and will invalidate corresponding cache lines. The bridge supports burst transactions, so that multiple contiguous reads or writes can be done in a sequence. The maximum data width supported by this bridge is 128-bit. Having all these features, the bridge is suitable for high-throughput data transfers initiated from the FPGA side.

- HPS-to-FPGA bridge. This bridge allows ARM core and HPS-side DMAs to access data on the FPGA side. The bridge supports burst transactions and has maximum data width of 128-bit. Thus, it is suitable for high-throughput data transfers initiated from the HPS side.

- Lightweight HPS-to-FPGA bridge. This bridge also allows the ARM core to access the data on the FPGA side, but it is primarily used for non-intensive traffic. A good example of such traffic is reading and modification of control and status register of custom hardware peripherals. Having a dedicated interface for such communication offloads the high-speed HPS-to-FPGA bridge and improve overall performance.

- FPGA-to-SDRAM bridge. This bridge allows FPGA peripherals to non-coherently access DRAM. That is, the CPU's cache will not be aware of changes in DRAM. The interface supports burst transactions and its maximum data width for unidirectional (read or write only) access is 256 bit. Thus, this interface is suitable for high-throughput data transfers initiated from the FPGA side.

#### 2.4 Terasic DE10-Nano Kit

Terasic DE10-Nano Kit is a Cyclone-V-based FPGA development board suitable for application in embedded systems due to its compact size and low cost. The photo

Figure 2.3: Photo of DE10-nano board

of the board is shown in Figure 2.3. Figure 2.4 depicts the resources that the board has. The most important of them are the following:

- Cyclone V SE 5CSEBA6U23I7NDK FPGA chip, consisting of two parts:

- FPGA with 32,070 ALMs [12]. The number of ALMs is equivalent to 85,000

logic elements. The FPGA part is relatively big and has even more logic

than is needed for this work.

- 800MHz dual-core ARM Cortex-A9 CPU. The processor is capable of running a fully-fledged Linux-based operating system.

Figure 2.4: Block diagram of DE10-nano board [11]

- 1GB of DDR3 memory with a 32-bit data bus. This memory can be used as RAM for Linix-based OS. It can also work as a storage for data produced by custom FPGA modules.

- 1 Gigabit Ethernet PHY. The network connection this PHY provides is useful for interacting with Linux running on the board remotely using SSH protocol.

- Micro SD card socket. SD card can be used to store Linux kernel and root file system. It is also possible to store there FPGA configuration as an .rbf file and load it to the FPGA fabric before booting Linux.

- UART to USB converter, connected to a UART on the HPS side. Even though having a network interface covers most needs for the user interaction with Linux,

the network is only initialized after Linux has booted. Thus, it is useful to have access to UART for observing boot process or changing boot configuration in U-boot, a Linux loader. In this work U-boot was helpful to activate FPGA-to-SDRAM bridge (see Appendix A).

• Three 50 MHz clock generators. These clock sources can be used to clock custom FPGA logic. If needed, the frequency of 50 MHz can be multiplied using on-chip phase locked loop (PLL) modules.

### 2.5 Avalon interfaces

Avalon is a group of interfaces available for use in Intel FPGAs. These interfaces unify interaction between hardware modules. The group includes the following interfaces that accommodate various needs [13]:

- Avalon-MM (Avalon Memory Mapped Interface) an interface for reading/writing data from/to devices that are or look like memory.

- Avalon-ST (Avalon Streaming Interface) an interface for handling unidirectional streams of data.

- Avalon Interrupt Interface an interface for notifying hardware components about events that they need to react on.

- Avalon Conduit Interface an interface that encapsulates a custom set of signal that are not encompassed by any other Avalon interfaces.

The following subsections describe Avalon interfaces that are essential for this work: Avalon-MM, Avalon-ST and Avalon Interrupt.

#### 2.5.1 Avalon-MM interface

Avalon-MM interface connects memory-like peripheral devices to a CPU or a DMA. Memory-like means that such a device must support reads or/and writes at a certain range of addresses. However, it does not mean the the device must have internal memory. The memory-like device is called the Slave (S) and the controlling device is called the Master (M).

Data transfers through Avalon-MM happen as follows. On the first clock cycle M asserts either read or write signal to indicate that it wants to read or write data to S. If it is a read transaction, on the same clock cycle M sets the address it wants to read from. If it is a write transaction, M also sets the data it wants to write on the writedata bus. On the next clock cycle, M observes the waitrequest signal, controlled by S. If this signal is asserted, M keeps all the signals it controls for one or more cycles until waitrequest is deasserted. Once this happens, M can read the readdata in the case of a read transaction. For a write transaction, having waitrequest deasserted means that the transaction was successful.

Table 2.4 lists most important signals that are used in the Avalon-MM interface. Additional information about the interface's features and signals can be found in [13].

In our system we used the Avalon-MM interface to give the CPU access to control and status registers of our peripheral devices. Through these registers the CPU can configure peripheral devices and observe their current state. More details

| Name        | Direction         | Description                                                                                                                                                                                                  |  |

|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| address     | M→S               | Master uses this signal to let the slave know which<br>address it is going to read or write.                                                                                                                 |  |

| read        | M→S               | Master uses this signal to signalize that it is going<br>to read data from the slave.                                                                                                                        |  |

| write       | M→S               | Master uses this signal to signalize that it is going<br>to write data to the slave.                                                                                                                         |  |

| readdata    | $S \rightarrow M$ | Slave outputs the data for reading by the Master through this bus.                                                                                                                                           |  |

| writedata   | M→S               | Master outputs the data for writing to the Slave through this bus.                                                                                                                                           |  |

| waitrequest | S→M               | Slave uses this signal to indicate that it cannot<br>process the current read or write request from the<br>Master. The Master must repeat its request on the<br>next clock cycle if this signal is asserted. |  |

Table 2.4:

Signals of Avalon-MM interface

about control and status registers of our peripherals can be found in Sections 5.1.1 and 5.1.2.

#### 2.5.2 Avalon-ST interface

Avalon-ST interface is used to connect a data provider to a data consumer. The data provider is called source (SRC) and the data consumer is called sink (SNK). Usually a single data item is transmitted per clock cycle. Its size is static, but can vary for different sources and sinks. SRC has the option not to send the data on a specific clock cycle. It deasserts the valid signal to notify SNK about this. If a valid data item is transmitted, the valid signal must be asserted. SNK has the option not to accept the data on any clock cycle. It deasserts the ready signal on the next clock

| Name  | Direction                               | Description                                                                     |

|-------|-----------------------------------------|---------------------------------------------------------------------------------|

| valid | $SRC \rightarrow SNK$                   | SRC uses this signal to indicate that its trying to transfer valid data to SNK. |

| data  | $\mathrm{SRC} \rightarrow \mathrm{SNK}$ | SRC uses this bus to transfer data to SNK.                                      |

| ready | SNK→SRC                                 | If SNK is unable to accept data from SRC, it asserts this signal to stall SRC.  |

Table 2.5:

Signals of Avalon-ST interface

cycle to notify SRC about this. SRC must repeat data transfer until SNK asserts the **ready** signal.

Table 2.5 lists most important signals that are used in the Avalon-ST interface. Additional information about the interface's features and signals can be found in [13].

In our system we used the Avalon-ST interface to output data from ChaCha20 accelerator (see Section 5.1.1). This interface allows us to supply data to the next stage, a custom DMA, only if the data is ready to be transmitted: the accelerator produces valid data only once every 20 clock cycles. Moreover, if the consumer cannot handle the data (for example when DRAM controller is busy and DMA cannot access it) the **ready** signal can stall the accelerator. More information about functioning of our DMA ChaCha20 accelerator can be found in Sections 5.1.1 and 5.1.2.

#### 2.5.3 Avalon interrupt

Avalon interrupt interface connects an interrupt sender to an interrupt receiver. Such a connection is useful when a slave device needs to notify a master device about some event as soon as possible. Usually this notification is handled by the master device in a timely manner, because master pauses its previous routine and processes the signal.

We used the Avalon interrupt interface in our system to connect our IP-core to the CPU. This allows the CPU to schedule a new computation as soon as the previous one is finished and its result is transferred to DRAM. Using an interrupt in this scenario minimizes the idle time of the IP-core. Section 5.1.2 contains more detailed information about interrupts in our system.

### 2.6 Userspace I/O device drivers

In Linux-based operating systems (OS) applications are executed in a virtual address space and with limited privileges. This restricted environment is called user space. By keeping applications in the user space, the OS protects itself and other applications from unauthorized access. This approach results in inability of regular applications to directly interact with memory-mapped hardware devices: they are controlled by reading and writing at dedicated addresses of CPU's physical address space, which is unavailable to user space programs.

Contrary to user-space applications, Linux kernel runs with higher privileges and thus can directly control devices (can function as a device driver). However, it is not always feasible to modify the kernel to add support of a custom device. That is why Linux-based OSs can be extended by adding kernel modules. Such modules can be loaded dynamically (when the kernel already runs). Even though the perspective of developing a device driver as a kernel module looks attractive, this task is hard: a bug in the module can crash entire OS. Generic Userspace Input/Output (UIO) driver [14] with interrupt handling support (a.k.a. uio\_pdrv\_genirq driver) is a good alternative to custom kernel modules. This module is a part of the Linux kernel code base and can be enabled by configuring the kernel before its compilation.

This device driver covers most needs for custom memory-mapped hardware devices. Through this driver user space programs can access device's control status registers (CSR) as well as handle interrupts. As a result, the major part of the device interaction logic can be moved to the user space, making the debugging task much easier as program errors do not crash entire system. The UIO driver even makes possible controlling devices directly from a program written in a higher level language such as Python.

Whenever the uio\_pdrv\_genirq module is loaded, it creates a device file /dev/uioX, where X is the device number. This file serves for both CSR access and interrupt handling. To access device registers the users space program opens this file using open() function and makes mmap() system call. The mmap() function returns a pointer to a virtual memory region that is mapped to the physical addressees of device CSRs. By modifying and reading that region, the program can control the device and observe its status.

To react on interrupt requests (IRQs), the user space program does a blocking read from the /dev/uioX file by calling to the read() function. This operation suspends the calling thread until the device triggers an interrupt. An interrupt event unlocks the suspended thread, so it can process the interrupt request. Usually, when reacting on an IRQ, device drivers write to certain CSR to deassert the interrupt line an be able to leave the interrupt service routine. However, the generic UIO driver is not aware of the functionality of CSRs of a specific device. Thus, to clear the interrupt, it disables the channel of the interrupt controller that belongs to the processed interrupt. This means that the users space program, which is aware of control and status register functionality, has to modify one of the registers to clear the pending interrupt. Finally, to be able to accept new interrupts the users space program does a file write operation on the /dev/uioX file. This operation activates the interrupt channel that was previously disabled.

There is an alternative to the generic UIO driver: user space programs can access physical address space by calling mmap() on the /dev/mem device file. This method provides access to any physical addresses including those that are mapped to CSRs of a custom device. The main advantage of this method is its availability for virtually any precompiled kernel (/dev/mem is enabled by default). To enable UIO support one often needs to configure and build their own kernel. However, the /dev/mem has a serious drawback: it does not support handling interrupts. That is why we used the generic UIO driver in our work instead of /dev/mem.

#### 2.7 User space mappable DMA Buffer

Direct Memory Access (DMA) is an important feature in a system that is expected to have a hight throughput. DMA can unload the CPU from moving memory content and reduce overhead of this process. DMA modules usually expect to have access to a physically contiguous region of memory. Operating system needs to be aware of this buffer so that it does not use it to store some other data. One may think of using regular malloc() call to allocate space for a DMA buffer. This, however, will not work: malloc() allocates a virtually contiguous region, but does not guarantee its physical contiguity. /dev/mem will not work either: although it can give a user space program access to physical memory in a contiguous manner, it cannot prevent the OS from using the buffer for other purposes.

This problem is usually solved by using kmalloc() function, which can provide physical contiguity. However, it is only available in the kernel space, which requires developing a kernel module.

An alternative solution is the udmabuf Linux device driver developed by Kawazome Ichiro [15]. This kernel module can reserve a contiguous chunk of memory of required size. The user space code can easily map this buffer to its virtual address space and find out its physical address to properly configure DMA using a UIO driver. Since udmabuf provides a buffer that satisfies all the requirements for DMA, we used it in our work.

# Chapter 3

# **RELATED WORK**

Developing custom cryptographic accelerators in hardware is a popular topic in scientific and engineering literature. Some articles feature an FPGA-based chip or a hybrid SoC as the target platform. Other use ASIC (application-specific integrated circuit) or do not mention any platform at all, discussing only a general architecture of the proposed design. Many publications feature AES as the accelerated algorithm. A few projects are devoted to acceleration of ChaCha20.

Cowart *et al.* present and discuss the results of their experiments where they measure the performance of hardware AES accelerators implemented in an all-programmable SoC [16]. Their target platform is Zedboard, a Zynq-7000-based development board. The authors discuss two AES IP-cores placed in the FPGA fabric: a non-pipelined core for the ECB and CBC AES modes, and a fully pipelined core for the CTR (counter) AES mode. They compared the performance of these cores to that of the OpenSSL library compiled for the ARM architecture. As a result, they did not manage to see a significant speedup for the non-pipelined core, but demonstrated that the pipelined one is almost 7 times faster than OpenSSL. The maximum performance observed for the non-pipelined core was 25 MiB/s and 350 MiB/s for the pipelined one.

Baskaran and Rajalakshmi present an AES accelerator fabricated using a 0.18-µm CMOS technology [17]. Their design supports the ECB (electronic codebook), OFB (output feedback), and CBC (cipher block chaining) modes of operation of AES and runs at the frequency of 330 MHz. The accelerator can be configured using a memory-mapped interface of a LEON 32-bit (SPARC V8) processor. The maximum throughput they manage to get in such setting is 480 MiB/s.

Silex Insight implemented ChaCha20-Poly1305 Crypto Engine as an IP-core [18]. The core supports the Authenticated Encryption with Associated Data (AEAD) mode. In such a mode only a part of the input message is encrypted. The other part is transmitted as is. However, both parts are authenticated [19]. The core is claimed to have multi Gibit/s speeds. However, the company's official website does not give any information about the core's exact throughput [20], so it is difficult to evaluate it.

Kanda and Ryoo propose an accelerator supporting ChaCha20-Poly1305-based AEAD [21]. Their target platform is Virtex 7, a high-end family of FPGAs from Xilinx. Their design can run at the clock frequency of 161.02 MHz, giving the resulting throughput of 515 MiB/s for ChaCha20 encryption without message authentication. The resource utilization of their design is 1692 LUTs and 566 registers. No information is provided about the way this core can be connected to a CPU.

Another work describes a compact co-processor that facilitates ChaCha computation as well as the computation of BLAKE and Skein — ChaCha-based hashing algorithms [22]. Instead of directly implementing ChaCha rounds, the authors propose

| Source                                                                                      | Algorithm                                                                                                   | Platform                                       | Frequency                              | Performance                                                                  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------|

| Cowart <i>et al.</i> [16]<br>Cowart <i>et al.</i> [16]<br>Baskaran and Rajalak-<br>shmi[17] | $\begin{array}{c} \mathrm{AES} \ \mathrm{CBC} \\ \mathrm{AES} \ \mathrm{CTR}^1 \\ \mathrm{AES} \end{array}$ | Zynq-7000<br>Zynq-7000<br>0.18-µm CMOS         | 100 MHz<br>100 MHz<br>330 MHz          | 25 MiB/s<br>350 MiB/s<br>480 MiB/s                                           |

| Kanda and Ryoo[21]<br>At <i>et al.</i> [22]<br>Strömbergson[23]<br>This thesis              | ChaCha20<br>ChaCha20<br>ChaCha20<br>ChaCha20                                                                | Virtex 7<br>Virtex 6<br>Cyclone V<br>Cyclone V | 161 MHz<br>266 MHz<br>60 MHz<br>50 MHz | 550  MiB/s<br>362  MiB/s<br>$159 \text{ MiB/s}^2$<br>$120.5 \text{ MiB/s}^3$ |

Table 3.1: Summary of the performance characteristics for various hardware cyphers

an architecture that can efficiently pipeline the primitive arithmetic operations that the algorithm involves. They argue that such an approach can significantly reduce resource utilization, but keep a high throughput. As a result, their architecture provides the throughput of 266 MiB/s at the clock frequency of 362 MHz for ChaCha20 algorithm while consuming only 49 slices and 2 block RAMs on Virtex-6 FPGA.

One more ChaCha20 implementation is available in a GitHub repository [23]. This project contains a standalone ChaCha20 module. According to its author the module has a non-pipelined design. The latency of producing one OTP is 23 clock cycles. When compiled for Cyclone V, this design is capable of working at 60 MHz and consumes 1939 ALMs (basic logic blocks of Cyclone V). This results in 159.22 MiB/s of theoretical throughput. Unlike our solution, this design does not have any processor interfaces, so it cannot be connected to HPS systems without additional modification.

$<sup>^{1}\</sup>mathrm{a}$  fully pipelined design is used

<sup>&</sup>lt;sup>2</sup>theoretical throughput

<sup>&</sup>lt;sup>3</sup>the result of using two IP-cores for file encryption

$<sup>^{4}</sup>$ custom DMA is not included

| Source             | Algorithm | Platform  | Registers | Logic                  |

|--------------------|-----------|-----------|-----------|------------------------|

| Kanda and Ryoo[21] | ChaCha20  | Virtex 7  | 566       | 1692 LUTs              |

| At $et al.[22]$    | ChaCha20  | Virtex 6  |           | 49 slices              |

| Strömbergson[23]   | ChaCha20  | Cyclone V | 1940      | $1939 \ \mathrm{ALMs}$ |

| Silex Insight [18] | ChaCha20- | Zynq-UP-  |           | $3769 \ \mathrm{LUTs}$ |

|                    | Poly1305  | MPSoC     |           |                        |

| This thesis        | ChaCha20  | Cyclone V | 1040      | $1440 \text{ ALMs}^4$  |

Table 3.2:

Summary of the resource consumption for various hardware cyphers

implemented in FPGA

\$\$\$

This thesis is different from the above-mentioned works in several aspects. First, we offer a ready-to-use open-source solution for hardware ChaCha20 acceleration that can easily be integrated in existing processor systems. Second, we provide a software framework that allows interfacing multiple hardware modules and using them for file encryption in the Linux environment. Finally, we carry out experiments that demonstrate the performance of our core under realistic conditions and show how it compares to a multi-threaded software implementation. The experiments have been done for a real-world application, file encryption.

Table 3.1 summarizes the performance of all related implementations mentioned in this section, including the implementation described in this thesis. Table 3.2 gives the summary of the resource consumption of all FPGA-based projects mentioned above. Both tables exclude implementations that do not mention the parameters of interest.

# Chapter 4

### DESIGN CONSIDERATIONS

In order to see how beneficial hardware realization of ChaCha20 encryption algorithm in all-programmable SoC can be, we developed a ChaCha20 IP-core in SystemVerilog. In this chapter we describe design decisions made to build a costeffective and high-throughput IP core.

# 4.1 Pipelining

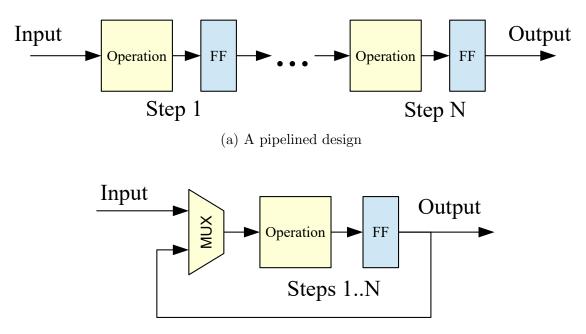

If an algorithm consists of a sequence of steps and this sequence does not depend on the input data, building a pipeline can greatly increase the throughput of a system. At the same time pipelining may require considerably more resources. If the data produced by a pipelined module cannot be utilized properly by the other modules, the pipeline will stall, leading to poor resource utilization. Alternatively, if all the steps of an algorithm are identical (the algorithm consists of a loop), a non-pipelined design with a feedback loop can be used. On one hand, such design will demonstrate N times lower performance, where N is the number of steps in the algorithm. On the other hand it will consume almost N time less resources. The pipelined and non-pipelined designs are shown in Figure 4.1. Blue rectangles depict

(b) A non-pipelined design with a feedback loop

Figure 4.1: A pipelined design vs a non-pipelined design with a feedback loop

registers and yellow rectangles depict combinational logic. The non-pipelined design contains a multiplexer that feeds the input data to the operation logic on the first step and connects the result of the operation to its input for the following steps. Once N steps are computed, the output becomes valid.

The decision between a pipelined design and a non-pipelined must be justified. ChaCha20 is a perfect candidate for pipelining as it consists of a static sequence of steps. A pipelined ChaCha20 module can produce 512 bits of OTP every clock cycle. Considering the clock rate of 50 MHz, it provides the data rate of:

$$64 \text{ bytes} \cdot 50 \text{ MHz} = 3.2 \text{ GiB/s} \tag{4.1}$$

At the same time, a non-pipelined implementation that computes one round per clock cycle produces 512 bits of OTP every 20 clock cycles. This results in the data rate of:

$$\frac{64 \text{ bytes} \cdot 50 \text{ MHz}}{20 \text{ cc}} = 160 \text{ MiB/s}$$

$$\tag{4.2}$$

Let us consider the DRAM of the DE1-SoC board as the storage for OTP. The board has two DDR3 memory chips that are connected to the memory controller by a 64-bit data bus. The clock rate of the memory is 400 MHz. Since DDR3 is a double data rate memory (two data transfers happen per clock cycle) the theoretical throughput of this DRAM is:

$$8 \text{ bytes} \cdot 400 \text{ MHz} \cdot 2 = 6.4 \text{ GiB/s}$$

$$(4.3)$$

Even though DRAM throughput is twice as high as the data rate of the pipelined ChaCha20, it does not mean that the pipelined version can be efficiently utilized. First, it is just a theoretical upper limit: the real speed may be a few times lower due to long memory timings [24]. Second, ChaCha20 module is not the only device accessing DRAM: the software part that does encryption needs to access OTP with the same rate.

Even if DRAM could handle the required data throughput, the FPGA-to-SDRAM bridge (see Section 2.3) would cause an additional limitation. Its maximum data width is 256 bit and its clock rate equals to the clock rate of the FPGA fabric. This means that if a pipelined ChaCha20 accelerator produced 512 bits of data every clock cycle, the bridge would require 2 clock cycles to send this data to the DRAM controller. Thus, the accelerator would stall every second clock cycle, waiting for the bridge.

One can argue that once a pipelined version is implemented, it can be successfully used in systems without sufficient throughput if the pipeline stalls properly. This can make the module more universal. However, pipelining is costly in terms of chip area. Let us assume that R is the number of logic gates required to build ChaCha20 round function and S is the number of flip-flops needed for a register, holding one ChaCha20 state. In this case, resource consumption of a pipelined module that computes 20 rounds will be 20R logic elements and 21S flip-flops. At the same time a non-pipelined implementation will take roughly R logic elements and 2S flip-flops. That is, for systems with a limited throughput, 95% of logic gates and 90% of flip-flops will be wasted.

Considering the problem with low DRAM bandwidth, an insufficient width of the FPGA-to-SDRAM bridge, and low resource utilization of the pipelined ChaCha20 version, we have chosen a non-pipelined approach.

# 4.2 XOR stage

The XOR stage of ChaCha20 is used to encrypt and decrypt data (see Section 2.2). This operation is unique comparing to the other 21 stages (20 rounds plus the summation stage) of the algorithm, so it requires additional resources that are not used for the rest of the algorithm. As a result, we could expect a low utilization ratio for the XOR gates involved:

$$\frac{1 \text{ clock cycle (XOR stage)}}{22 \text{ clock cycles (total number of stages)}} = 4.54\%$$

(4.4)

To prudently use FPGA resources, the XOR stage can be handled by software. Keeping this stage on the HPS side should not significantly affect the performance: in Section 6.2.3 we will show that file access together with XOR operation is far from the critical path. Moreover, having XOR stage in HPS avoids moving plaintext (for encryption) or cypertext (for decryption) to the FPGA side and reading back the result: only moving OTP from FPGA to HPS is necessary. As a result, our design choice can reduce HPS-to-FPGA bridge traffic by two times.

#### 4.3 Summation stage

The summation stage adds 32-bit words of the initial state to the result of 20 rounds (see Section 2.2). This operation is unique comparing to the other 21 stages (20 rounds plus the XOR stage) of the algorithm, so it requires additional resources that are not used for the rest of the algorithm. As a result, we could expect a low utilization ratio for the adders involved:

$$\frac{1 \text{ clock cycle (summation stage)}}{22 \text{ (total number of stages)}} = 4.54\%$$

(4.5)

To prudently use FPGA resources, the summation stage can be handled by software. Keeping this stage on the HPS side should not significantly affect the performance. The summation stage requires the same number of instructions as the XOR stage (16 add instructions versus 16 xor instructions per 512 bits of OPT), which is also handled by software (see Section 4.2). According to the data presented in Section 6.2.3, even if the number of instructions on the CPU side doubles, the CPU part will still be far from the critical path, so we expect no significant performance degradation caused by this design decision.

# 4.4 Summary

As the result of careful consideration the following design decisions have been made:

- A non-pipelined architecture has been chosen;

- Only the round function will be implemented in hardware;

- The summation and the XOR stages will be handled in software.

#### Chapter 5

# **DESIGN DESCRIPTION**

In order to see how beneficial hardware realization of ChaCha20 encryption algorithm in all-programmable SoC can be, we developed a ChaCha20 IP-core in SystemVerilog and designed a software framework to employ it for file encryption and compare it with our software implementation. This chapter describes the design of the IP core and the software framework for evaluating its effectiveness, using a file encryption/decryption as an exemplar workload.

# 5.1 FpgaCha IP-core

FpgaCha is a hardware IP-core for ChaCha20 algorithm acceleration that we implemented to do this research. FpgaCha is packaged as an Intel Platform Designer (an Intel's tool for system integration) subsystem, so it can easily be connected to different processor systems such as Nios II or an ARM-based HPS. Internal modules of FpgaCha are implemented in SystemVerilog. According to the Timing Analyzer, the  $F_{max}$  parameter of this core is 54.38 MHz for the Slow 1100 mV 100 C° model (a conservative model). We use a slightly lower frequency of 50 MHz to clock the core as it is easier to derive. The source code of the IP-core is available at [25].

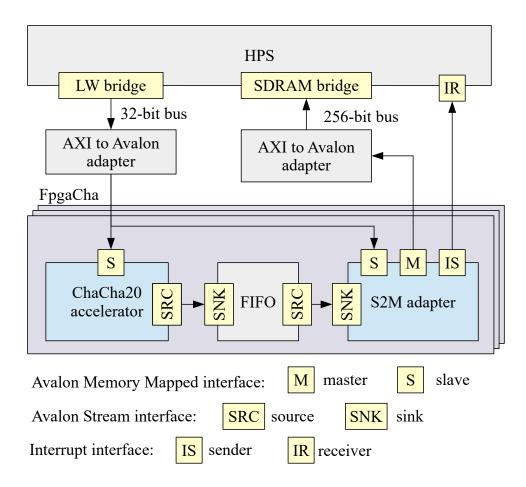

Figure 5.1: Hardware components of FpgaCha

Figure 5.1 shows all components of the core and how it is interfaced to to the HPS. Blue rectangles represent custom modules and gray rectangles represent modules already available in the Intel Platform Designer.

FpgaCha IP-core functions as follows. The HPS configures ChaCha20 accelerator and S2M (Avalon-ST to Avalon-MM) adapter through the lightweight HPS-to-FPGA bridge (LW bridge in Figure 5.1). AXI to Avalon adapter connects a simpler Avalon-MM slave interface to the AXI bus that is native to the bridge. ChaCha20 accelerator configuration includes setting encryption parameters (key, nonce, initial block count) and the number of OTP blocks that needs to be produced. S2M adapter configuration includes setting the target address of SDRAM and the number of 256-bit chunks to transfer (twice the number of OTP blocks set in ChaCha20 accelerator). Right after configuring, ChaCha20 accelerator starts producing OTP blocks. They go to the S2M adapter through a FIFO buffer with the capacity of 16 512-bit items. The buffer helps to avoid stalling ChaCha20 accelerator if S2M adapter cannot accept data for a short period of time. S2M adapter accepts data from the queue and moves it to SDRAM through the FPGA-to-SDRAM bridge. One more AXI to Avalon adapter is used here for connecting the Avalon-MM master interface to AXI bus of the bridge. Once all scheduled transfers are finished, the adapter sends an interrupt request to the HPS. Upon accepting the request, the HPS clears pending interrupt flag in S2M adapter and the cycle repeats if more OTP blocks are needed. Now HPS can access generated blocks in the DRAM.

The following two subsections describe the functionality of our custom modules: ChaCha20 accelerator and S2M adapter in more detail.

# 5.1.1 ChaCha20 accelerator

ChaCha20 accelerator is a custom SystemVerilog module that is capable of computing 20 rounds of ChaCha20 algorithm in 20 clock cycles. The module has a non-pipelined architecture and does not include the summation stage.

From the programmer's point of view the module looks like a set of control registers. Their functionality is summarized in Table 5.1. To configure the module the programmer, first, needs to set up the initial ChaCha20 state (see Section 2.2). Second, the programmer should decide how many OTP blocks the module will generate

| Name             | Byte offset     | Description                                                                                                                                                                   |

|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT_STATE[0:15] | 0x0000 - 0x001F | A 16-word (32 bits per word) initial<br>state for ChaCha20 algorithm. This<br>register consists of multiple fields such<br>as key, nonce, and block count (see<br>Table 2.1). |

| PAD_COUNTER      | 0x0020          | The number of one-time pads (with-<br>out the summation stage) to generate.<br>The module start computation upon<br>modification of this register.                            |

Table 5.1: Register map of ChaCha20 accelerator

and set the PAD\_COUNTER register. The bigger this number is, the less significant the configuration overhead will be. On the other hand, bigger numbers require more memory to store OTP. Upon modification the PAD\_COUNTER register, the module starts producing OTP blocks and outputs them through Avalon-ST interface. When generating blocks the module automatically increments the block count field of the INIT\_STATE register.

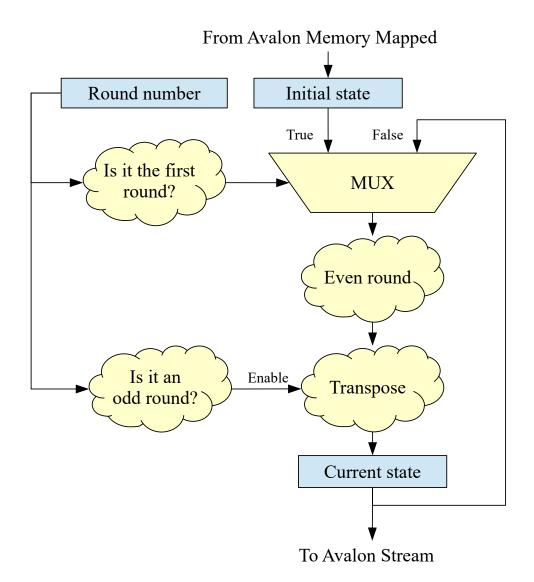

The data path of the module is shown in Figure 5.2. This diagram demonstrates how a single OTP (without the summation stage) is calculated by the module. Blue rectangles represent registers and yellow clouds depict combinational logic. Initially, the round number register (not accessible by the programmer) contains 0. The register is incremented by 1 every clock cycle until it reaches 19. The current state register is also updated every clock cycle and contains the last result of the round function. In the first round, the current state is computed based on the initial state (configured by the programmer). In the following rounds, the previous value of the current state

Figure 5.2: The data path of ChaCha20 accelerator. Its feedback loop allows computation of multiple ChaCha rounds iteratively

serves as the input for the round function. Once 20 rounds have been computed, the result is available through the Avalon-ST source interface. If Avalon-ST (see Section 2.5.2) sink deasserts the **ready** line, signalizing its inability to accept data, the module stalls, so that no data gets lost. If Avalon-ST sink accepts the data, the block

| Resource type     | Available [12] | Used  | Utilization ratio |

|-------------------|----------------|-------|-------------------|

| ALMs              | 32,070         | 1,440 | 4.5%              |

| Registers         | $128,\!300$    | 1,094 | 0.9%              |

| Block memory bits | 4,065,280      | 0     | 0.0%              |

| DSP blocks        | 87             | 0     | 0.0%              |

Table 5.2:

FPGA resource utilization of ChaCha20 accelerator

count field in the initial state register is incremented, the PAD\_COUNTER is decremented, and the process of computing 20 rounds is repeated until PAD\_COUNTER reaches 0.

The module is quite compact as it takes only 4.5% of the logic resources available in the FPGA chip. Its resource utilization is summarized in Table 5.2

#### 5.1.2 S2M adapter

S2M adapter is a custom SystemVerilog module that accepts 512-bit data items through the Avalon-ST sink interface, splits them into two 256-bit chunks and transfers these chunks through the 256-bit Avalon-MM master interface at a certain address configurable by the programmer. To reach better performance, the module does those transfers in bursts of two. In the IP-core the module is used to transfer data from ChaCha20 accelerator to DRAM. Basically, the adapter functions as a DMA, but has a smaller size as it contains only essential functionality. It also supports a 512-bit Avalon-ST interface, which is not supported by the DMAs available in Platform Designer.

From the programmer's point of view the module looks like a set of control registers. Their functionality is summarized in Table 5.3. To configure the module the

| Name    | Byte offset | Description                                                                                                           |

|---------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| LENGTH  | 0x0000      | The number of 256-bit chunks of data to<br>be transferred. Modification of this register<br>initiates a data transfer |

| ADDRESS | 0x0004      | Starting address in the DRAM for transfer-<br>ring data at                                                            |

| IRQ     | 0x0008      | Modification of this register clears a pend-<br>ing interrupt request                                                 |

Table 5.3: Register map of S2M adapter

programmer, first, needs to chose the destination address in DRAM and set it to the ADDRESS register. Second, the programmer has to decide how many 256-bit chunks of data should be transfered from ChaCha20 accelerator to DRAM, and set this number to the LENGTH register. Since each block of OTP is 512-bit long, this number must be 2 times bigger than the number used in the PAD\_COUNTER register (see Section 5.1.1) of ChaCha20 accelerator. Improperly chosen value of LENGTH will cause undefined behavior. Modification of LENGTH starts data transfer. Once LENGTH 256-bit chunks have been transferred, the module generates an interrupt, signalizing about the end of the transfer. The programmer is supposed to modify the IRQ register to clear the pending interrupt.

S2M adapter supports the waitrequest signal from the Avalon-MM slave interface. This signal can stall the module if the DRAM controller is busy. Moreover, if necessary, the module can stall the Avalon-ST source interface, by deasserting the ready signal. This feature prevents data loss when the DRAM controller experiences high load. Also, it allows connection of multiple FpgaCha modules to the same DRAM

| Resource type     | Available [12] | Used | Utilization ratio |

|-------------------|----------------|------|-------------------|

| ALMs              | 32,070         | 186  | 0.6%              |

| Registers         | $128,\!300$    | 354  | 0.3%              |

| Block memory bits | 4,065,280      | 0    | 0.0%              |

| DSP blocks        | 87             | 0    | 0.0%              |

Table 5.4:

FPGA resource utilization of S2M adapter

port: the arbitration logic introduced by Platform Designer uses waitrequest signal to stall the Avalon-MM masters that lose arbitration.

The module is quite compact as it takes only 0.6% of the logic resources available in the FPGA chip. Its resource utilization is summarized in Table 5.4

### 5.2 Software organization

In order to carry out experiments and compare the hardware solution to the software one, we have implemented a small software framework. The framework is written in C++ programming language. Its source code is freely available at [25].

We designed the framework to satisfy the following requirements:

- support for multi-threading;

- support for multiple hardware accelerators;

- simplicity of adding or removing hardware accelerators and varying the number of threads;

- capability of testing performance of data consumers and producers separately;

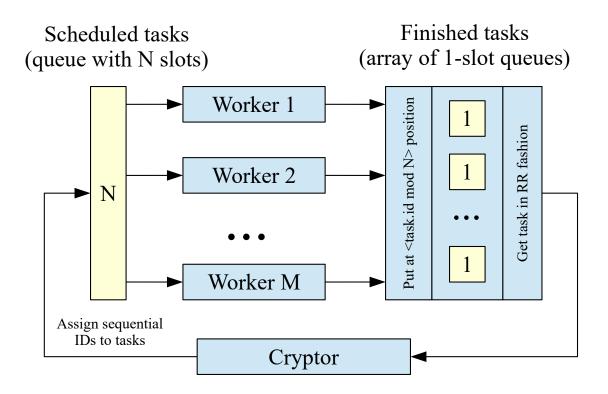

Figure 5.3: Structure of our software framework

• the system must be self-balancing: if data producer or data consumer is faster than its counterpart, it must stall.

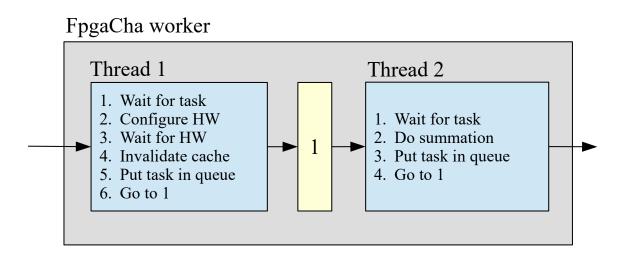

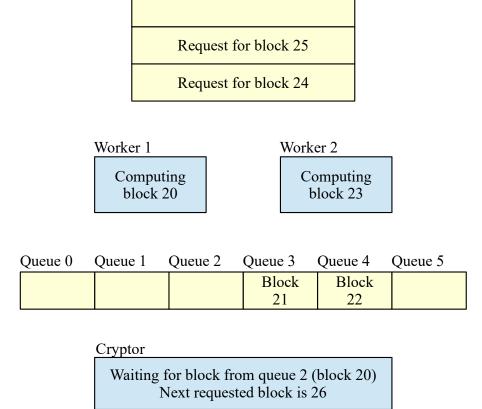

The structure of the framework is shown in Figure 5.3. It consists of the following components: tasks (objects that represent the need for OTP blocks or produced OTP blocks; the flow of tasks is depicted as arrows), queues (buffers temporary storing tasks; depicted as yellow rectangles), workers (threads that perform tasks by generating OTP blocks), and cryptors (threads that use solved tasks to do data encryption). The following subsections describe those components in detail and explain how they function as a whole.

5.2.1 Task

Task is a C++ struct that represents a job that needs to be done on some data. Arrows in Figure 5.3 represent the flow of tasks. The type of work that needs to be done is determined by the consumer of a task. In Figure 5.3 the tasks that enter workers represent the need of the cryptor for OTP. The tasks that exit the workers represent ready-to-use OTP blocks that can be used for data encryption.

Each task contains the following fields:

- id: the sequence number of a task. There are no two tasks with the same id in the system.

- buffer: a pointer to the buffer with the input data (if any) for the task. This buffer is used to store the result (if any) of the task as well.

- length: the number of words available in the buffer.

There is a constant number of tasks in the system. This property helps to prevent excessive memory consumption if the producer of tasks produces them faster than the consumer can handle.

# 5.2.2 Queue