### LOW OVERHEAD HARDWARE TECHNIQUES FOR SOFTWARE AND DATA INTEGRITY AND CONFIDENTIALITY IN EMBEDDED SYSTEMS

by

#### **AUSTIN ROGERS**

#### **A THESIS**

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

**HUNTSVILLE, ALABAMA**

2007

| In presenting this thesis in partial f | fulfillment of the requirements for a master's degree     |

|----------------------------------------|-----------------------------------------------------------|

| from The University of Alabama in      | n Huntsville, I agree that the Library of this University |

| shall make it freely available for in  | nspection. I further agree that permission for extensive  |

| copying for scholarly purposes may     | ay be granted by my advisor or, in his/her absence, by    |

| the Chair of the Department or the     | e Dean of the School of Graduate Studies. It is also      |

| understood that due recognition sha    | nall be given to me and to The University of Alabama in   |

| Huntsville in any scholarly use wh     | nich may be made of any material in this thesis.          |

|                                        |                                                           |

|                                        |                                                           |

| (student signature)                    | (date)                                                    |

|                                        |                                                           |

#### THESIS APPROVAL FORM

Submitted by Austin Rogers in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this thesis. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering.

| (Date) | Committee Chair  |

|--------|------------------|

| ,      |                  |

|        |                  |

|        |                  |

|        |                  |

|        | Department Chair |

|        | Department Chan  |

|        | College Dean     |

|        | Graduate Dean    |

## **ABSTRACT**

# The School of Graduate Studies The University of Alabama in Huntsville

| Degree Master of Scie               | nce in Engineering                  | College/Dept.       | Engineering/Electrical &           |

|-------------------------------------|-------------------------------------|---------------------|------------------------------------|

|                                     | -                                   | - 0 1               | Computer Engineering               |

| N 60 111                            | A C D                               |                     |                                    |

| Name of Candidate<br>Title Low Over | Austin Rogers head Hardware Techniq | ues for Software    | and Data Integrity and             |

|                                     | ality in Embedded Syst              |                     | and Data Integrity and             |

|                                     | willy in Line duals syst            |                     |                                    |

| Computer secu                       | rity is an ever-increasing          | g challenge. Bill   | ions of microprocessors have       |

| been sold, most of whi              | ch form parts of embedo             | ded computer syst   | ems. Computers are subject to      |

| both software and phys              | sical attacks, and rampa            | nt piracy causes a  | severe loss of revenue. These      |

| problems can be allevi              | ated by addressing the is           | ssues of integrity  | (preventing the execution of       |

| unauthorized instruction            | ons or the use of unautho           | orized data) and co | onfidentiality (preventing the     |

| unauthorized copying                | of instructions or data).           | This thesis propo   | ses architectural enhancements to  |

| ensure the integrity and            | d confidentiality of softw          | ware instructions a | and the data used by those         |

| instructions. The perfo             | ormance and energy ove              | rhead introduced    | by these architectures is analyzed |

| using a cycle-accurate              | simulator. The memory               | overhead and on     | -chip complexity of the proposed   |

| architectures are analy             | zed qualitatively. Our a            | nalyses show that   | these proposed architectures may   |

| be implemented with le              | ow performance and end              | ergy overhead, and  | d only moderate on-chip            |

| complexity and memor                | ry overhead.                        |                     |                                    |

| Abstract Approval:                  | Committee Chair                     |                     |                                    |

|                                     |                                     |                     |                                    |

|                                     | Department Chair                    |                     |                                    |

|                                     | Graduate Dean                       |                     |                                    |

#### **ACKNOWLEDGMENTS**

"To know wisdom and instruction; to perceive the words of understanding;

To receive the instruction of wisdom, justice, and judgment, and equity;

To give subtlety to the simple, to the young man knowledge and discretion."

Proverbs 1:2-4

As a researcher, I stand on the shoulders of many researchers before me. The research documented herein builds on the work of Aleksandar and Milena Milenković, Emil Jovanov, and Chris Otto. In particular, the simulation infrastructure they established provided a solid foundation and convenient starting point for the simulation software used in this current research.

In addition to the researchers whose work I have continued, I must also thank my friends, family, and coworkers for their support and understanding.

Finally, I dedicate this thesis to my parents, Brenda Lee Nixon Rogers and William Austin Heard Rogers (of blessed memory), without whose encouragement, love, and support this thesis would not have been possible.

## TABLE OF CONTENTS

|    |      |                |                                                                       | Page |

|----|------|----------------|-----------------------------------------------------------------------|------|

| LI | ST O | F FIGU         | TRES                                                                  | X    |

| LI | ST O | F TABI         | LES                                                                   | xiii |

| CF | HAPT | ER             |                                                                       |      |

| 1  | INT  | RODU           | CTION                                                                 | 1    |

|    | 1.1  | Secur          | e Processors: Motivation and Background                               | 1    |

|    | 1.2  | Propo<br>Confi | sed Architectures for Ensuring Software/Data Integrity and dentiality | 2    |

|    | 1.3  | Contr          | ibutions                                                              | 3    |

|    | 1.4  | Outlin         | ne                                                                    | 4    |

| 2  | CON  | MPUTE          | ER SECURTITY                                                          | 5    |

|    | 2.1  | Softw          | are Attacks                                                           | 5    |

|    |      | 2.1.1          | Buffer Overflow Attacks                                               | 6    |

|    |      | 2.1.2          | Format String Attacks                                                 | 6    |

|    |      | 2.1.3          | Integer Error Attacks                                                 | 6    |

|    |      | 2.1.4          | Dangling Pointer Attacks                                              | 7    |

|    |      | 2.1.5          | Arc-Injection Attacks                                                 | 7    |

|    | 2.2  | Physic         | cal Attacks                                                           | 8    |

|    |      | 2.2.1          | Spoofing Attacks                                                      | 8    |

|    |      | 2.2.2          | Splicing Attack                                                       | 9    |

|   |     | 2.2.3  | Replay Attacks                                                      | 10 |

|---|-----|--------|---------------------------------------------------------------------|----|

|   | 2.3 | Side-C | Channel Attacks                                                     | 11 |

|   |     | 2.3.1  | Timing Analysis                                                     | 11 |

|   |     | 2.3.2  | Differential Power Analysis                                         | 12 |

|   |     | 2.3.3  | Fault Exploitation                                                  | 12 |

|   |     | 2.3.4  | Architectural Exploitation                                          | 13 |

| 3 | REL | ATED   | WORK                                                                | 14 |

|   | 3.1 | Acade  | emic Proposals                                                      | 14 |

|   | 3.2 | Indust | rial Solutions                                                      | 18 |

| 4 |     |        | RE SUPPORTED TECHNIQUES FOR ENSURING SOFTWARE Y AND CONFIDENTIALITY | 20 |

|   | 4.1 | Frame  | ework Overview                                                      | 20 |

|   |     | 4.1.1  | Secure Installation                                                 | 21 |

|   |     | 4.1.2  | Secure Loading                                                      | 24 |

|   |     | 4.1.3  | Secure Execution                                                    | 25 |

|   |     | 4.1.4  | Other Considerations                                                | 26 |

|   | 4.2 | Basic  | Implementation                                                      | 27 |

|   |     | 4.2.1  | Implementation Details                                              | 27 |

|   |     | 4.2.2  | Performance Overhead                                                | 29 |

|   |     | 4.2.3  | Hardware Requirements                                               | 31 |

|   | 4.3 | Reduc  | eing Overhead                                                       | 33 |

|   |     | 4.3.1  | PMAC                                                           | 34 |

|---|-----|--------|----------------------------------------------------------------|----|

|   |     | 4.3.2  | Run-Before-Verification                                        | 36 |

|   |     | 4.3.3  | Reducing Memory Overhead                                       | 37 |

|   | 4.4 | Summ   | nary                                                           | 43 |

| 5 |     |        | RE SUPPORTED TECHNIQUES FOR ENSURING DATA YAND CONFIDENTIALITY | 44 |

|   | 5.1 | Data F | Framework Overview                                             | 44 |

|   |     | 5.1.1  | Secure Installation                                            | 46 |

|   |     | 5.1.2  | Secure Loading                                                 | 47 |

|   |     | 5.1.3  | Secure Execution                                               | 47 |

|   | 5.2 | Hardw  | vare Support for Runtime Verification                          | 54 |

|   | 5.3 | Perfor | mance Overhead                                                 | 56 |

|   |     | 5.3.1  | TLB Miss and Write-back                                        | 56 |

|   |     | 5.3.2  | Sequence Number Cache Miss and Write-back                      | 58 |

|   |     | 5.3.3  | Data Cache Miss                                                | 60 |

|   |     | 5.3.4  | Data Cache Write-back                                          | 63 |

|   | 5.4 | Summ   | nary                                                           | 64 |

| 5 | EXF | ERIME  | ENTAL ENVIRONMENT                                              | 65 |

|   | 6.1 | Exper  | imental Flow                                                   | 65 |

|   | 6.2 | Bench  | marks                                                          | 67 |

|   | 6.2 | Cimul  | ation Coftwara                                                 | 71 |

|    | 6.4  | Simulation Parameters                               | 72  |

|----|------|-----------------------------------------------------|-----|

| 7  | RES  | SULTS                                               | 74  |

|    | 7.1  | Complexity Overhead                                 | 74  |

|    | 7.2  | Memory Overhead                                     | 75  |

|    | 7.3  | Instruction Protection Architecture (SICM) Overhead | 75  |

|    |      | 7.3.1 Performance Overhead                          | 76  |

|    |      | 7.3.2 Energy Overhead                               | 84  |

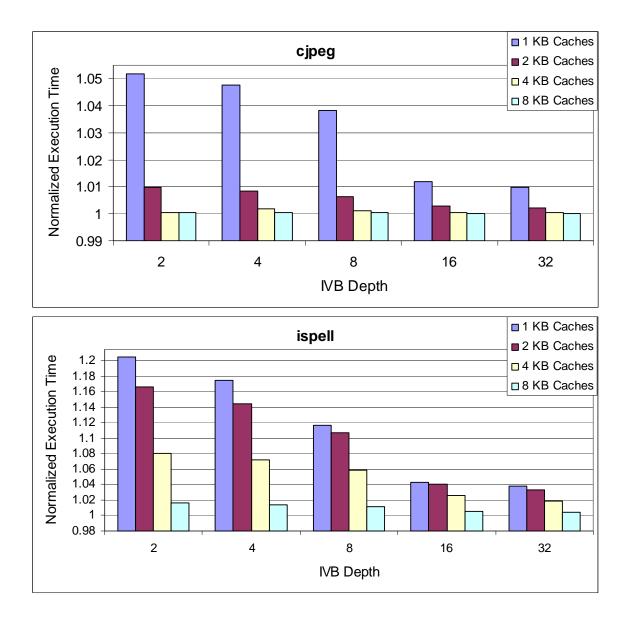

|    |      | 7.3.3 IVB Depth                                     | 90  |

|    | 7.4  | Data Protection Architecture (DICM) Overhead        | 92  |

| 8  | CON  | NCLUSIONS AND FUTURE WORK                           | 103 |

| RE | EFER | ENCES                                               | 105 |

## LIST OF FIGURES

| Figure | Page                                                                                     |

|--------|------------------------------------------------------------------------------------------|

| 2.1    | Spoofing Attack                                                                          |

| 2.2    | Splicing Attack                                                                          |

| 2.3    | Replay Attack                                                                            |

| 4.1    | Overview of Architecture for Trusted Instruction Execution                               |

| 4.2    | Signed Binary Instruction Block: (a) Signed plaintext, (b) ES, (c), EtS, (d) StE. 24     |

| 4.3    | I-Cache Miss Algorithm, CBC-MAC Implementation                                           |

| 4.4    | Verification Latency, CBC-MAC WtV Implementation                                         |

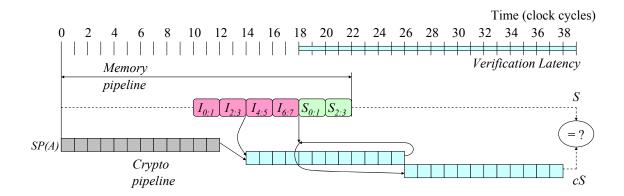

| 4.5    | Instruction Block Signature Verification Unit                                            |

| 4.6    | I-Cache Miss Algorithm, PMAC Implementation                                              |

| 4.7    | Verification Latency, PMAC WtV Implementation                                            |

| 4.8    | Instruction Verification Buffer                                                          |

| 4.9    | I-Cache Miss Algorithm, PMAC Implementation, Expanded Protected I-Block 39               |

| 4.10   | Memory Layout and Cache Miss Cases                                                       |

| 4.11   | Verification Latency, PMAC RbV Implementation, Expanded Protected I-Block, Cases 1 and 2 |

| 4.12   | Verification Latency, PMAC RbV Implementation, Expanded Protected I-Block, Case 3        |

| 4.13   | Verification Latency, PMAC RbV Implementation, Expanded Protected I-Block,               |

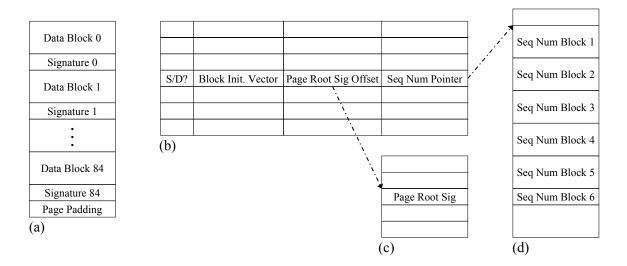

| 5.1  | Memory Structures for Protecting Dynamic Data: (a) Dynamic Data Page, (b) Page Table Modifications, (c) Page Root Signature Table, (d) Sequence Number Table | . 50 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.2  | Sequence Number Cache Miss Algorithm                                                                                                                         | . 59 |

| 5.3  | D-Cache Miss Algorithm                                                                                                                                       | . 62 |

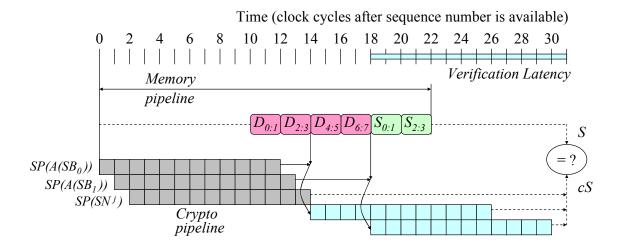

| 5.4  | Verification Latency, D-Cache Miss                                                                                                                           | . 62 |

| 5.5  | D-Cache Write-back Algorithm                                                                                                                                 | . 64 |

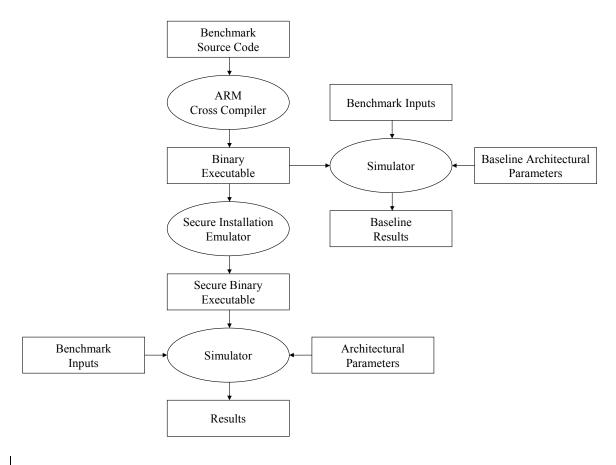

| 6.1  | Experimental Flow                                                                                                                                            | . 66 |

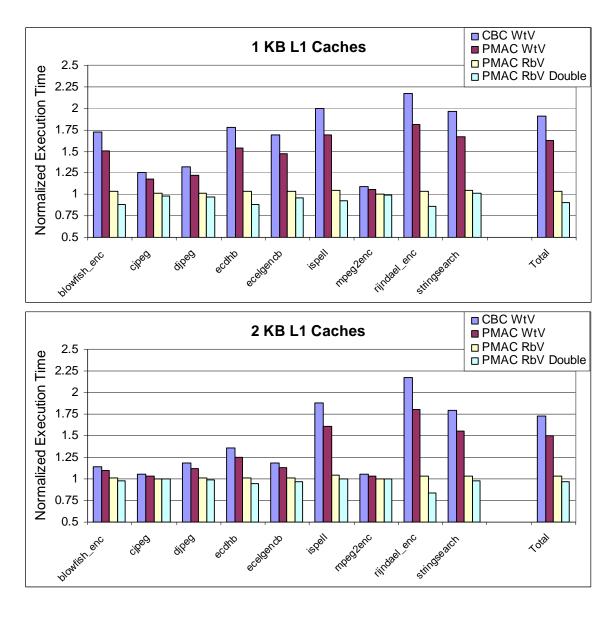

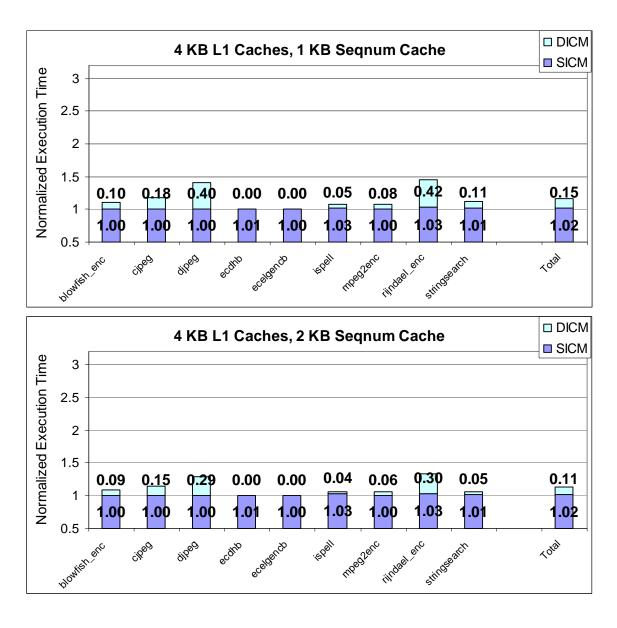

| 7.1  | Performance Overhead for Embedded Benchmarks, SICM, 1 KB and 2 KB L1 Cache Sizes                                                                             | . 77 |

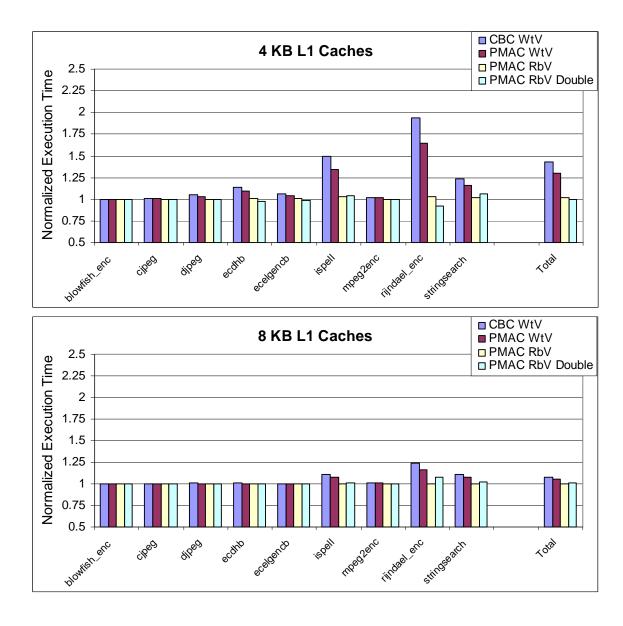

| 7.2  | Performance Overhead for Embedded Benchmarks, SICM, 4 KB and 8 KB L1 Cache Sizes                                                                             | . 78 |

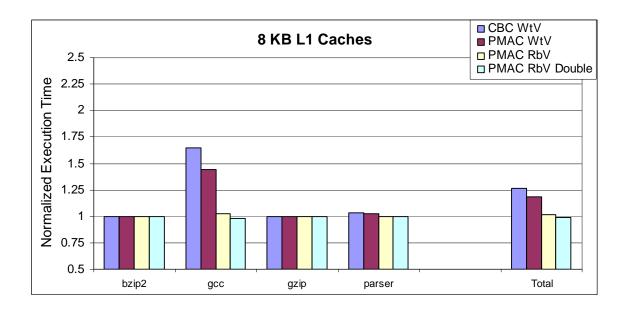

| 7.3  | Performance Overhead for SPEC Benchmarks, SICM, 8 KB Cache Sizes                                                                                             | . 80 |

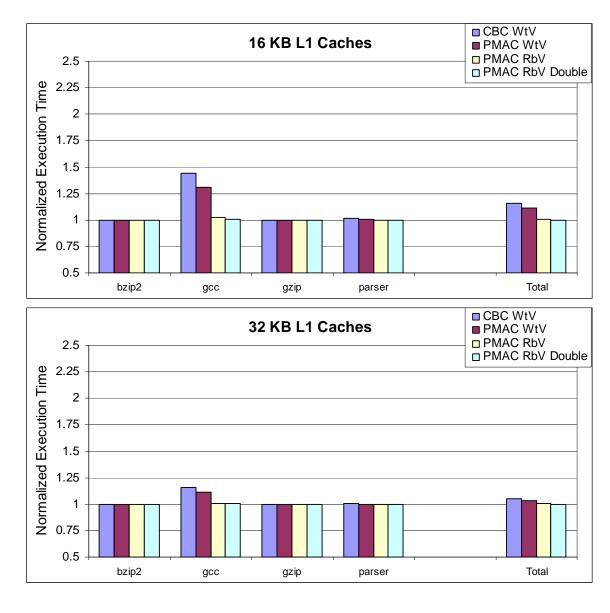

| 7.4  | Performance Overhead for SPEC Benchmarks, SICM, 16 KB and 32 KB Cach Sizes                                                                                   |      |

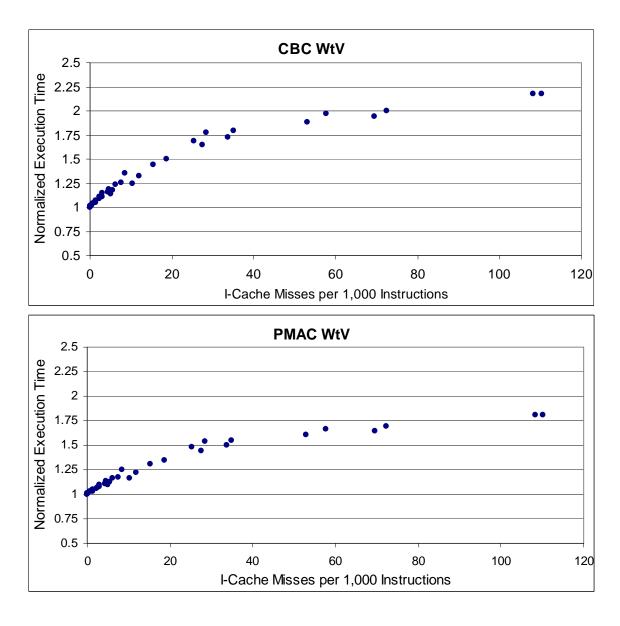

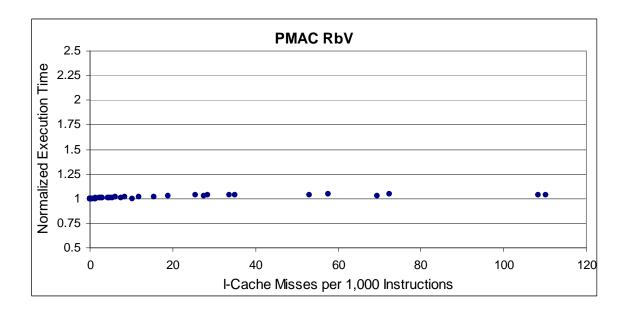

| 7.5  | Normalized Execution Time vs. I-Cache Miss Rate, SICM, CBC WtV and PM WtV Implementations                                                                    |      |

| 7.6  | Normalized Execution Time vs. I-Cache Miss Rate, SICM, PMAC RbV Implementation                                                                               | . 84 |

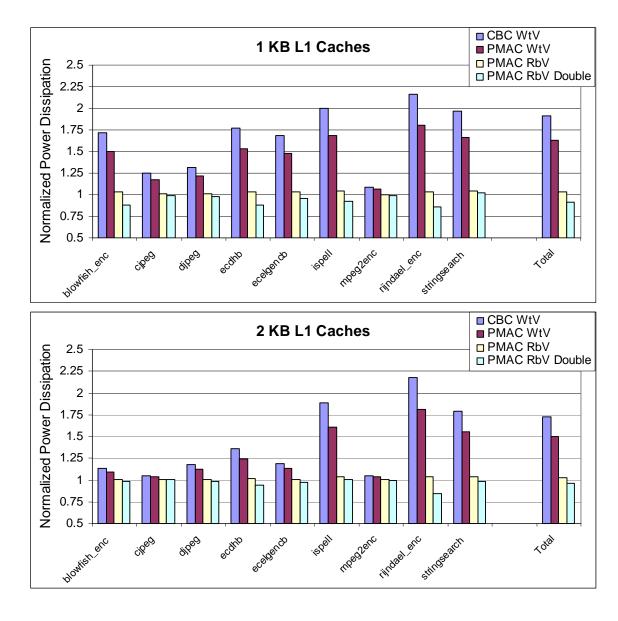

| 7.7  | Energy Overhead for Embedded Benchmarks, SICM, 1 KB and 2 KB L1 Cach Sizes                                                                                   |      |

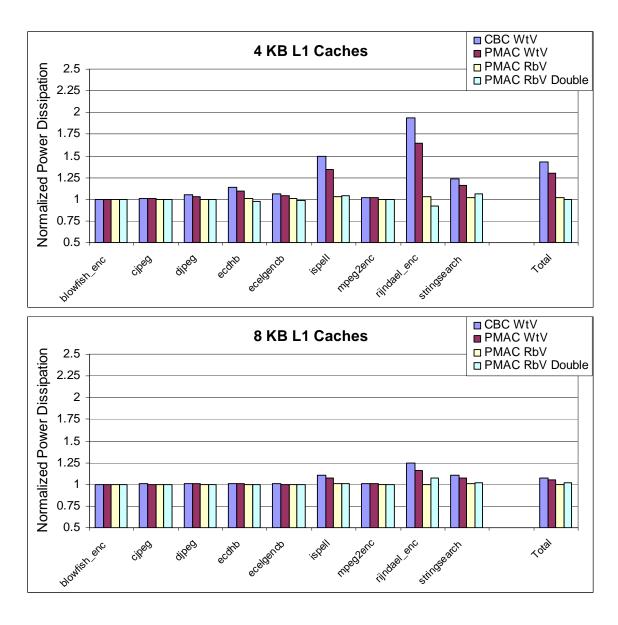

| 7.8  | Energy Overhead for Embedded Benchmarks, SICM, 4 KB and 8 KB L1 Cach Sizes                                                                                   |      |

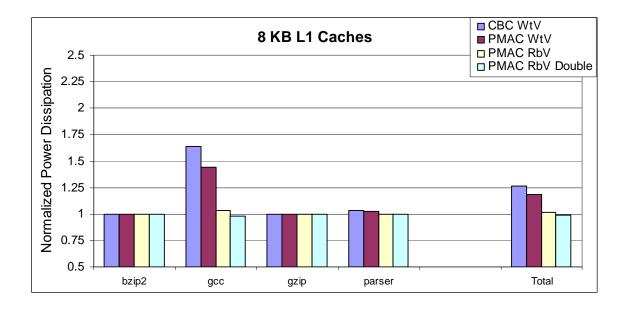

| 7.9  | Energy Overhead for SPEC Benchmarks, SICM, 8 KB L1 Cache Size                                                                                                | . 88 |

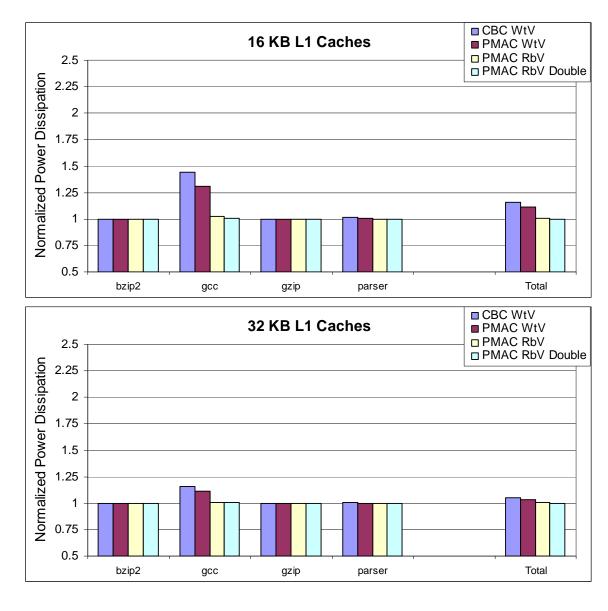

| 7.10 | Energy Overhead for SPEC Benchmarks, SICM, 16 KB and 32 KB Cache Size                                                                                        |      |

| 7.11 | IVB Depth Evaluation                                                        | . 91 |

|------|-----------------------------------------------------------------------------|------|

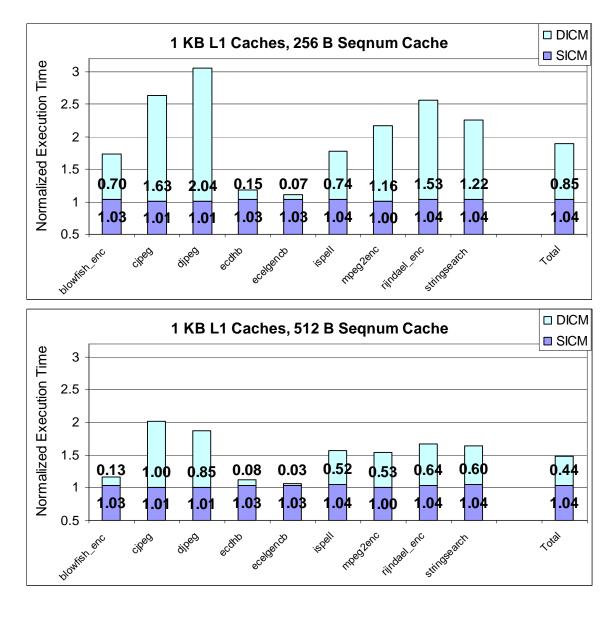

| 7.12 | Performance Overhead for Embedded Benchmarks, SICM/DICM, 1 KB L1 Cache Size | . 93 |

| 7.13 | Performance Overhead for Embedded Benchmarks, SICM/DICM, 2 KB L1 Cache Size | . 94 |

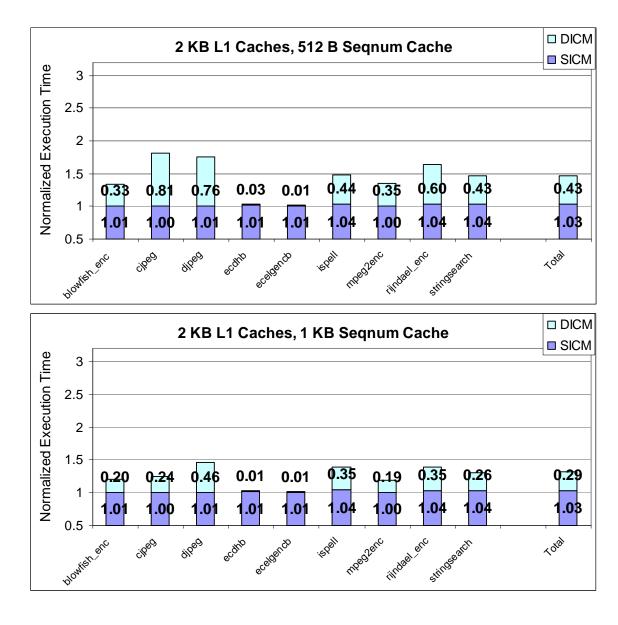

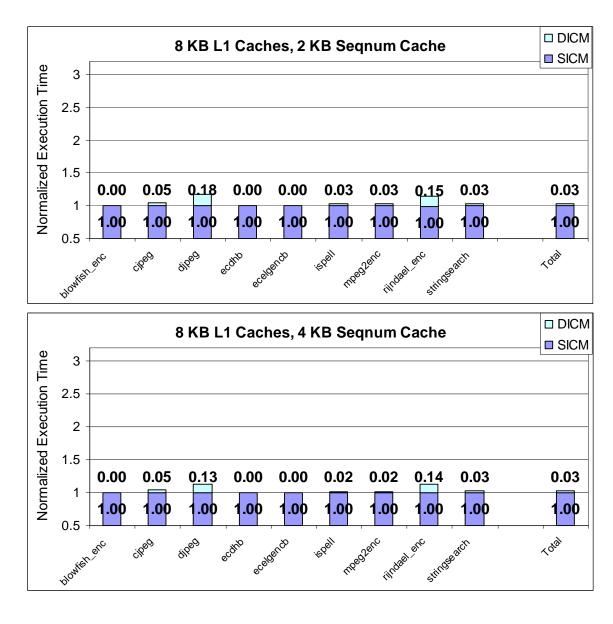

| 7.14 | Performance Overhead for Embedded Benchmarks, SICM/DICM, 4 KB L1 Cache Size | . 95 |

| 7.15 | Performance Overhead for Embedded Benchmarks, SICM/DICM, 8 KB L1 Cache Size | . 96 |

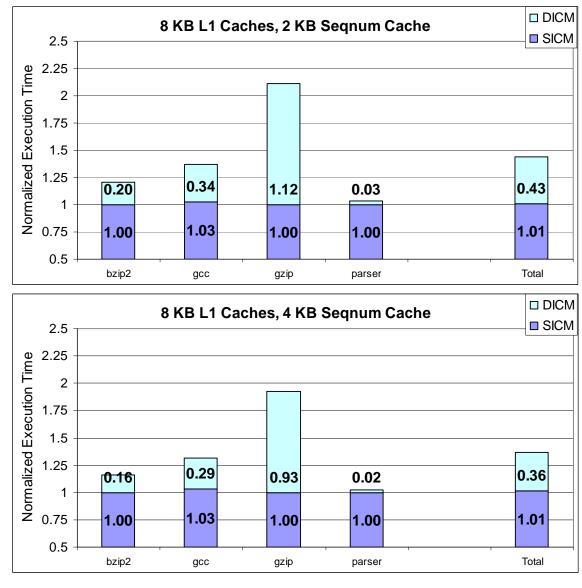

| 7.16 | Performance Overhead for SPEC Benchmarks, SICM/DICM, 8 KB L1 Cache Size     | . 98 |

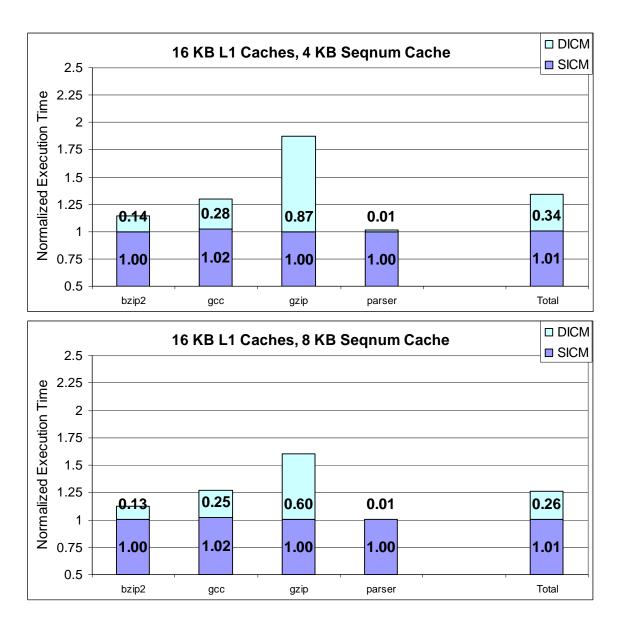

| 7.17 | Performance Overhead for SPEC Benchmarks, SICM/DICM, 16 KB L1 Cache Size    |      |

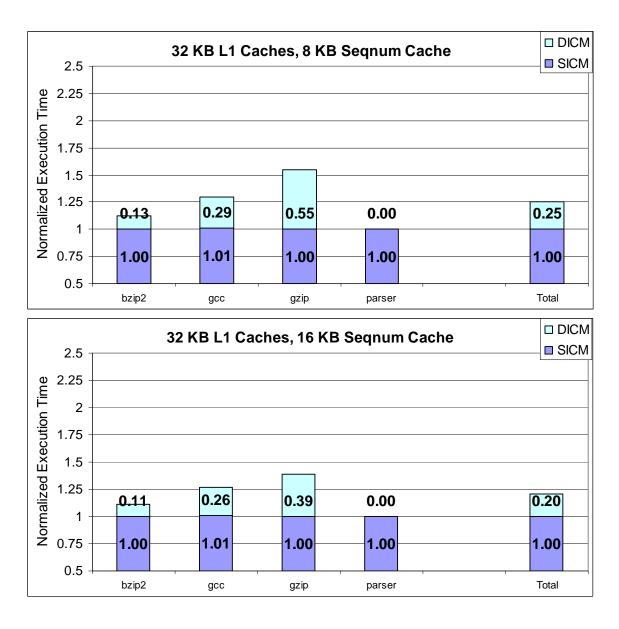

| 7.18 | Performance Overhead for SPEC Benchmarks, SICM/DICM, 32 KB L1 Cache Sizes   |      |

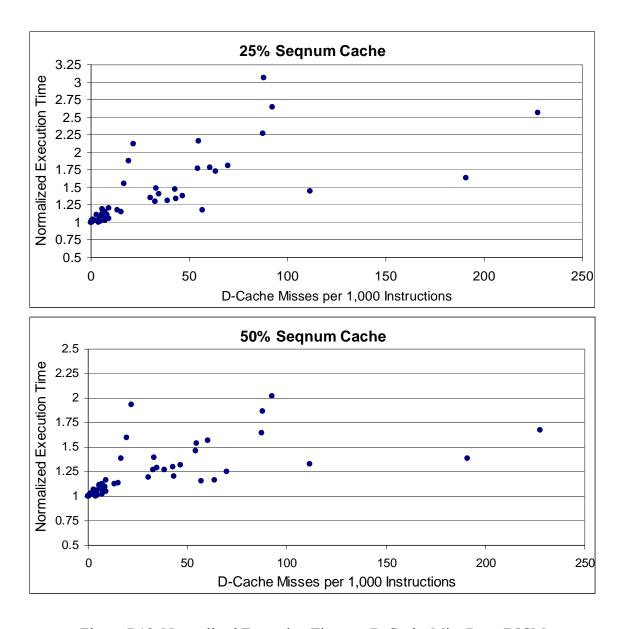

| 7.19 | Normalized Execution Time vs. D-Cache Miss Rate, DICM                       | 102  |

## LIST OF TABLES

| Table | P                                                                                  | age  |

|-------|------------------------------------------------------------------------------------|------|

| 6.1   | Description of Embedded Benchmarks                                                 | . 68 |

| 6.2   | Cache Miss Rates for Embedded Benchmarks                                           | . 68 |

| 6.3   | Description of SPEC Benchmarks                                                     | . 70 |

| 6.4   | SPEC Benchmark Segment Weights                                                     | . 70 |

| 6.5   | Cache Miss Rates for SPEC Benchmarks                                               | . 70 |

| 6.6   | Simulation Parameters                                                              | . 73 |

| 7.1   | Performance Overhead for Embedded Benchmarks, SICM, 1 KB and 2 KB L1 Cache Sizes   |      |

| 7.2   | Performance Overhead for Embedded Benchmarks, SICM, 4 KB and 8 KB L1 Cache Sizes   | . 79 |

| 7.3   | Performance Overhead for SPEC Benchmarks, SICM, 8 KB, 16 KB, and 32 KL Cache Sizes |      |

| 7.4   | Energy Overhead for Embedded Benchmarks, SICM, 1 KB and 2 KB L1 Cach Sizes         |      |

| 7.5   | Energy Overhead for Embedded Benchmarks, SICM, 4 KB and 8 KB L1 Cach Sizes         |      |

| 7.6   | Energy Overhead for SPEC Benchmarks, SICM, 8 KB, 16 KB, and 32 KB L1 Cache Sizes   | . 90 |

| 7.7 | Performance Overhead for Embedded Benchmarks, DICM | 97    |

|-----|----------------------------------------------------|-------|

|     |                                                    |       |

| 7.8 | Performance Overhead for SPEC Benchmarks, DICM     | . 101 |

#### **CHAPTER 1**

#### INTRODUCTION

Embedded computer systems are everywhere. They are indispensable to modern telephones, music players, network routers, and even weapons systems. Society relies on embedded systems to perform an increasing multitude of tasks. As the number of embedded applications increases, so do the incentives for attackers to compromise the security of these systems. Security breaches on these systems may have wide ranging impacts, from simple loss of revenue to loss of life. Maintaining security on embedded systems is therefore vital for the consumer, industry, and government.

#### 1.1 Secure Processors: Motivation and Background

Computer systems are often subject to attacks, and the number of vulnerabilities is high. According to the United States Computer Emergency Readiness Team [1], 5,198 software vulnerabilities were identified in the year 2005 alone, the number of actual attacks was much greater. Unauthorized copying of software is another major threat. The Business Software Alliance [2] estimates that, in the year 2006, 35% of all software installed on personal computers was pirated, leading to forty billion dollars in lost revenue. Furthermore, the number of fielded computer systems is astronomical. Most observers would recognize general purpose desktops, workstations, and servers as computer systems, but the number of these systems in the field is far outstripped by the

number of embedded systems. In 1999, an estimated total of 250 million 32-bit processors and one billion each of 16-bit, 8-bit, and 4-bit processors were sold, which contrasts sharply with the 100 million desktop, workstation, and server computer systems that were sold [3].

This thesis addresses computer security from the microprocessor's perspective. We focus on embedded systems, and address the areas of integrity, confidentiality, and availability. Integrity is violated whenever any unauthorized code is executed on a system or unauthorized data is used by the processor. Confidentiality is violated whenever some entity, human or computer, is able to view, copy, or reverse-engineer instructions or data. Availability is violated whenever a legitimate user is denied access to the system. The architectures we propose directly address the integrity and confidentiality of software instructions and data. The architectures indirectly address availability in that attacks on integrity often result in a loss of availability.

## 1.2 Proposed Architectures for Ensuring Software/Data Integrity and Confidentiality

We propose two architectures for secure processors. One addresses the integrity and confidentiality of the software itself (instructions). The other addresses the integrity and confidentiality of data used by the software. These two architectures may be implemented independently or combined as appropriate.

Software integrity and confidentiality is ensured using encryption and signature verification. The confidentiality of instructions is preserved by encrypting the data using a variant one-time pad (OTP) scheme, which provides a high level of security while allowing for quick decryption at runtime. Instruction integrity is preserved by signing the

when new instructions are fetched from memory, their signature is recalculated and compared to the signature from memory. If the signatures do not match, the instructions have been subjected to tampering and program execution is halted.

Encryption and signature verification are also used to ensure the integrity and confidentiality of the data used by the instructions. Encryption and signature generation incorporate a data versioning scheme to support dynamic data. Data versions, stored as sequence numbers, are themselves signed at the data page level to ensure their integrity. The integrity of the page-level signatures is ensured by using them to calculate a program-level signature.

#### 1.3 Contributions

The primary contribution of this work is the proposal of architectures for ensuring the integrity and confidentiality of both software instructions and data. This work includes several unique and/or innovative features, such as the following:

- We propose architectures for ensuring the integrity and confidentiality of both software instructions and data.

- We introduce several enhancements to reduce performance, power, and memory

overhead including: the parallel message authentication code (PMAC) cipher, the

instruction verification buffer, protecting multiple instruction blocks with one

signature, and caching sequence numbers.

- We establish a cycle-accurate simulation framework for quantitative evaluation of these architectures.

We use the cycle-accurate simulator to evaluate performance and power overhead.

#### 1.4 Outline

The remainder of this thesis is organized as follows. Chapter 2 presents an overview of several threats to computer security. Chapter 3 surveys existing proposals for hardware support meant to preserve software and/or data integrity and/or confidentiality. Chapter 4 details our proposed architecture for preserving software integrity and confidentiality, while Chapter 5 details our proposed architecture for preserving data integrity and confidentiality. Chapter 6 describes the experimental environment used to evaluate these architectures. Chapter 7 evaluates these architectures both qualitatively and with quantitative test results for various benchmarks. Chapter 8 concludes the thesis and suggests avenues for further research.

#### **CHAPTER 2**

#### **COMPUTER SECURITY**

This chapter briefly examines several types of attacks that embedded systems may experience. First we look at software-based attacks, where the attacker already has access to a system, either directly or over a network. Next we look at physical attacks, where the attacker has physical access to the system but not necessarily software access. Finally we examine side-channel attacks, in which the attacker attempts to gain knowledge about the system by indirect analysis.

#### 2.1 Software Attacks

Software attacks require the attacker to have some form of access to the target computer system. This could be direct access, with a lower permission level than the attacker desires. The access could also be across a network, which would require the attacker to sniff the system's open ports, looking for services with known vulnerabilities. The goal of software attacks is to modify a running program by injecting and executing code. The foreign instructions must be injected into memory, and then the return address of the currently executing function must be overwritten to force the processor to execute the injected instructions. These attacks are only briefly documented here; a more detailed treatment can be found in [4].

#### 2.1.1 Buffer Overflow Attacks

A common class of attacks is buffer overflow. These attacks take advantage of I/O instructions that simply store incoming data to a buffer, without bothering to check to see if the amount of incoming data will exceed the buffer size. After the buffer fills, memory locations beyond the buffer are overwritten. Most systems have stacks that grow counter to memory address growth. If the buffer is on the stack, then this attack can overwrite the data at any address on the stack beyond the buffer with malicious instructions. This overwrite includes the return address, allowing the attacker to divert the program to the newly injected instructions. If the buffer is on the heap near a function pointer, then the attacker's goal is to inject code and overwrite that function pointer.

#### 2.1.2 Format String Attacks

Format string attacks take advantage of *printf*-family instructions that take a format string as an input. These functions will accept any pointer and interpret the contents of memory at that address as a format string. By skillfully manipulating the inputs passed to the *printf* function, the attacker can read from any address in memory. The *%n* format character presents an additional vulnerability. This character causes a *printf* function to write the number of characters output by the function before it reached *%n* to a specified address. A skillful attacker could use this to write an arbitrary integer to any address.

#### 2.1.3 Integer Error Attacks

Errors arising from integer operations cannot be used as a direct attack. However, integer errors can facilitate other forms of attacks. For instance, an unsigned integer

overflow can result in a smaller number than expected. If this is used to allocate a buffer, then the buffer will also be smaller than expected. This exposes the system to a buffer overflow attack, even if subsequent input operations using that buffer check input length.

A more thorough treatment of integer error attacks may be found in [5].

#### 2.1.4 Dangling Pointer Attacks

Dangling pointers become an issue if the *free* function is called twice for the same pointer. The vulnerability arises from the way that the GNU C library handles memory allocation [6]. When a chunk of memory is freed, it is inserted into a doubly linked list of free chunks. If *free* is called twice, the pointers to the next and previous entries may wind up pointing back to the same chunk. An attacker may write malicious code to the chunk's data area and put a pointer to that code in place of the pointer to the previous list entry. If that chunk is allocated again, the memory manager will try to unlink the chunk from the list, and will write the attacker's pointer to an address calculated from the pointer to the next entry. If that address happens to contain a function's return address, then a successful attack has been accomplished.

#### 2.1.5 Arc-Injection Attacks

An arc injection or "return-into-libc" involves overwriting a return address such that control flow is disrupted. Oftentimes the address of a library function is used.

Library system calls can be used to spawn other processes on the system with the same permissions as the compromised program. If the operating system (OS) itself is compromised, then the attacker can run a malicious program that will have the ability to access any and every memory location.

#### 2.2 Physical Attacks

In contrast to software attacks, physical attacks involve tampering with the actual computer hardware. Probes are often inserted on the address and data bus, allowing the attacker to monitor all transactions and override data coming from memory with his/her own data. This is a tool often used in industrial and military espionage. This section describes three such attacks: spoofing, splicing, and replay.

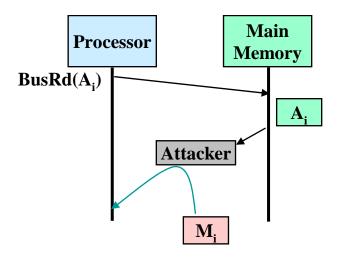

#### 2.2.1 Spoofing Attacks

A spoofing attack occurs when an attacker intercepts a request for a block of memory, and then manually supplies a block of his/her choice. This block may contain either data or instructions of a malicious nature. In an unsecured system, the processor na $\ddot{\text{v}}$  conducts a bus cycle, and is unaware that the data it received came from an attacker rather than from main memory. The spoofing process is illustrated in Figure 2.1. The processor initiates a bus read cycle for a block at memory location  $A_i$ . The attacker intercepts the request and supplies a potentially malicious block  $M_i$  instead of the correct block  $A_i$ .

Figure 2.1 Spoofing Attack

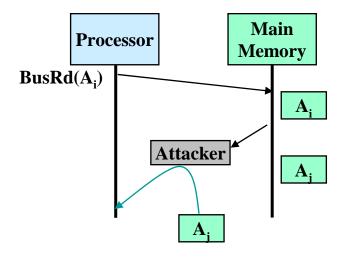

#### 2.2.2 Splicing Attack

Splicing attacks involve intercepting a request for a block of memory and then supplying the data from a different block. The supplied block is a valid block from somewhere in the address space, but it is not the actual block that the processor requested. This attack may be performed with either data or instruction blocks. Once again, the unsecured processor is unaware that it has received the incorrect memory block. The splicing attack methodology is illustrated in Figure 2.2. The processor initiates a bus read cycle for a block at memory location A<sub>i</sub>. The attacker intercepts the request and supplies a valid block from memory, but from address A<sub>j</sub> rather than the desired address.

Figure 2.2 Splicing Attack

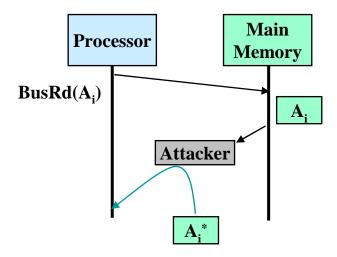

#### 2.2.3 Replay Attacks

In a replay attack, the attacker intercepts a request for a block of memory, and then supplies an older copy of that block. This is primarily a concern for data blocks rather than instructions. The supplied block was correct at some point in the past, but now it may be obsolete. The replay attack process is illustrated in Figure 2.3. The processor initiates a bus read cycle for the data block at address  $A_i$ . The attacker intercepts the request and returns an older version of that block, which may be different from the current version in memory.

Figure 2.3 Replay Attack

#### 2.3 Side-Channel Attacks

Side-channel attacks attempt to gather information about a system or program via indirect analysis. These attacks involve first collecting information about the system and then analyzing that information in an attempt to deduce the system's secrets [7]. The information gathering stage requires some form of access to the system. The attacker may have direct physical access to the system and its components, or have some level of privileges to run programs on the target system. In this section, we briefly describe a few examples of the myriad possible side-channel attacks, including timing analysis, differential power analysis, fault exploitation, and architectural exploitation.

#### 2.3.1 Timing Analysis

Timing attacks are, perhaps, the simplest type of side-channel attacks, taking advantage of the fact that different operations require different amounts of time to execute. Kochner [8] illustrates how this can be used to break cryptographic algorithms,

given a known algorithm and either known plaintext or known ciphertext. He uses timing analysis to determine the secret exponent in the Diffie-Hellman algorithm, factor RSA private keys, and determine the private key used by the Digital Signature Standard algorithm.

#### 2.3.2 Differential Power Analysis

A microprocessor's power consumption at any given moment can indicate what operations it is performing. A differential power analysis can be used to determine what instructions are executed and when. Kocher *et al.* [9] discuss how to break a known, data-driven encryption algorithm using such an attack. Instantaneous CPU power consumption is measured at intervals during a cryptographic operation, forming a trace. Multiple traces can be compiled and compared, revealing patterns produced by the execution of certain instructions. Since the encryption algorithm is both known and data-driven, the data being processed can be revealed solely from the power traces.

#### 2.3.3 Fault Exploitation

A fault exploitation attack takes advantage of hardware faults to discover secrets. These hardware faults may be transiently occurring within the processor, or induced externally. Boneh *et al.* [10] describe a simple fault exploitation attack, whereby the modulus used by an RSA algorithm may be calculated. A signature must be calculated from the same data two times. One signature is calculated without a hardware fault. The second is calculated in the presence of a hardware fault, either transient or induced. The modulus of the RSA system can then be factored by analyzing the difference between the

two signatures. Boneh *et al.* go on to break even more sophisticated cryptographic schemes using similar techniques.

#### 2.3.4 Architectural Exploitation

Due to the well-known effect of Moore's Law, microprocessor designers have been able to introduce more and more advanced features. Sometimes these advanced features may be exploited to reveal information about the processor. A prime example of an architectural exploitation attack is the Simple Branch Prediction Analysis attack devised by Aciicmez et al. [11]. This attack expands on the classical timing attack by taking advantage of the branch prediction unit and multi-threading capabilities of the Pentium 4 processor. A spy process is executed in parallel with a process performing a known cryptographic algorithm. The spy process executes branch instructions, flooding the processor's branch target buffer (BTB), while measuring the execution time required for those branch instructions. When the cryptographic process executes a branch instruction that results in the branch not being taken, no BTB eviction is needed. Thus, the next time the spy process executes a corresponding branch, it will execute quickly, thereby revealing that the cryptographic process had a branch not taken. Conversely, a taken branch in the cryptographic process results in a BTB eviction, which in turn causes a spy process branch to take longer to execute, revealing that the cryptographic process had a taken branch. The recorded trace of branches that were taken and not taken can then be used to deduce the cryptographic secret key. This attack relies on detailed information about the underlying hardware and software, but such information is often available and can be obtained using microbenchmarks [12].

#### **CHAPTER 3**

#### RELATED WORK

In this chapter, we briefly survey several architectural techniques that have been proposed to support the software and data integrity and confidentiality. Security may be approached from both the software and hardware perspectives. Software techniques may be classified as static (relying on the detection of security vulnerabilities in code at design time) and dynamic (adding code to enhance security at runtime). A survey of static and dynamic software techniques may be found in [4]. Hardware techniques rely primarily on hardware to ensure security, often with some degree of software support. This chapter focuses on hardware techniques, as our proposed security architectures are hardware-oriented. We first examine various proposals from academia, which are well documented. Then we examine industrial security solutions, which are not as well documented due to their proprietary nature.

## 3.1 Academic Proposals

Several techniques have been put forth to address common types of attacks. Xu *et al.* [13] and Ozdoganoglu *et al.* [14] propose using a secure hardware stack to defend against stack buffer overflow attacks. Tuck *et al.* [15] suggest using encrypted address

pointers. Suh *et al.* [16] and Crandall and Chong [17] propose that all data coming from untrusted channels be tagged, thus not allowed to be used as a jump target.

The execute-only memory (XOM) architecture proposed by Lie *et al.* [18] provides an architecture meeting the requirements of integrity and confidentiality. Main memory is assumed to be insecure, so all data entering and leaving the processor while it is running in secure mode is encrypted. This architecture was vulnerable to replay attacks in its original form, but that vulnerability was corrected in [19]. The drawbacks to this architecture are its complexity and performance overhead. XOM requires modifications to the processor core itself and to all caches, along with additional security hardware. This architecture also incurs a significant performance overhead, by its designers' estimation, of up to 50%.

The high overhead of XOM is reduced by the architectural improvements proposed by Yang *et al.* [20]. They only address confidentiality, as their improvements are designed to work with XOM, which already addresses integrity concerns. They propose to use a one-time pad (OTP) scheme for encryption and decryption, in which only the pad is encrypted and then exclusive or-ed with plaintext to produce ciphertext, or with ciphertext to produce plaintext. They augment data security by including a sequence number in the pad for data blocks, and require an additional on-chip cache for said sequence numbers. While their scheme greatly improves XOM's performance, it inherits its other weaknesses.

Gassend *et al.* [21] propose to verify untrusted memory using a tree of hashes. They only address integrity, suggesting that their architecture can be added to a system such as XOM, which will handle confidentiality concerns. The use of a hash tree

introduces significant bandwidth overhead, which is alleviated by integrating the hash mechanism with system's caches. However, their integrity-only overhead is still high, with a maximum of 20% for the most efficient architecture they propose.

Lu *et al.* [22] propose a similar architecture, using a message authentication code (MAC) tree. MACs are computed for each cache block, incorporating its virtual address and a secret application key. For higher level nodes, MACs are computed using those from the lower level and a random number generated from thermal noise in the processor. They propose to enhance performance by caching MAC data on the chip. This MAC tree architecture does show an improvement over the hash tree proposed by Gassend *et al.*, but it still introduces an average performance overhead of between 10% and 20%.

Suh *et al.* [23] propose an architecture that addresses confidentiality and overall integrity. Their architecture uses one-time pad (OTP) encryption to provide confidentiality with relatively low overhead. However, since their cryptographic functions take a timestamp as an input, they propose that the entire protected memory be re-encrypted on the unlikely event of a timestamp counter rollover. To reduce overhead from integrity checking, they propose to construct a log of memory accesses using incremental multiset hashes. They assume that a program produces meaningful, signed outputs either at the end of its execution or at discrete intervals during execution. Their architecture verifies the hashed memory access sequences only when those outputs are produced. Since verification occurs infrequently, it introduces negligible overhead. The major drawback is that tampering is not immediately evident, leaving the system potentially vulnerable between verifications.

Another architecture proposed by Suh and his colleagues [24] is the AEGIS secure processor. They describe physical unclonable functions (PUFs) to generate the secrets needed by their architecture. Memory is divided into four regions based on whether it is static or dynamic (read-only or read-write) and whether it is only verified or is both verified and confidential. They allow programs to change security modes at runtime, starting with a standard unsecured mode, then going back and forth between a mode supporting only integrity verification and a mode supporting both integrity and confidentiality. They also allow the secure modes to be temporarily suspended for library calls. This flexibility comes at a price; their architecture assumes extensive operating system and compiler support.

The work of Milenković *et al.* [4, 25, 26] provides the foundation for the research documented in this thesis. They introduced many of the elements that will be used in this current work and described below. Their proposed architecture addresses only the integrity of instructions, and involves signing instruction blocks during a secure installation procedure. These signatures are calculated using instruction words, block starting addresses, and a secret processor key, and are stored together in a table in memory. At runtime, these signatures are recomputed and checked against signatures fetched from memory. The cryptographic function used in the architecture is a simple polynomial function implemented with multiple input shift registers. The architecture is updated in [27] and [28], adding AES encryption to increase cryptographic strength and embedding signatures with instruction blocks rather than storing them in a table. This architecture remains vulnerable to splicing attacks, since signatures in all programs use the same key.

Drinić and Kirovski [29] propose a similar architecture to that of Milenković et al., but with greater cryptographic strength. They use a cipher block chaining (CBC-) MAC cipher, and include the signatures in the cache line. They propose to reduce performance overhead by reordering basic blocks, so that instructions that may not be safely executed in a speculative manner are not issued until signature verification is complete. The drawback to this approach is that it requires significant compiler support, and may consistently hide the verification overhead. Furthermore, their architecture does not address confidentiality, and is vulnerable to replay and splicing attacks.

#### 3.2 Industrial Solutions

Microprocessor vendors Intel and Advanced Micro Devices (AMD) have each introduced features to prevent buffer overflow attacks. Intel calls their feature the Execute Disable Bit [30], which prohibits the processor from executing instructions that originate from certain areas of memory. AMD's No Execute (NX) Bit [31] is very similar to Intel's Execute Disable Bit. The NX bit is stored in the page table, and is checked on translation look-aside buffer (TLB) misses. Both Intel and AMD allow software to disable this functionality.

International Business Machines (IBM) has developed the SecureBlue architecture [32]. Like the academically-proposed techniques described above, it relies on cryptography to ensure integrity and confidentiality of both software and data. SecureBlue is intended to be incorporated into existing microprocessor designs.

ARM markets the TrustZone security architecture [33], designed to augment ARM microprocessors. It relies on both hardware and software support. The hardware component uses cryptography to address integrity and confidentiality, allowing the

processor to run in either a secure or non-secure mode. The software support includes the TrustZone Monitor, which augments the operating system and provides an application programming interface (API) for secure programs.

Maxim (formerly Dallas Semiconductor) manufactures the DS5250 secure microprocessor [34]. The DS5250 is designed to serve as a co-processor for embedded systems with traditional, non-secure microprocessors. Maxim proposes that the co-processor perform security-sensitive functions while the primary processor performs less sensitive operations. The DS5250 contains a non-volatile on-chip memory that is erased if physical tampering is detected. This memory is used to store the processor's secret key, and can also be used to securely store other sensitive data. The DS5250 can also access external memory, using cryptography to ensure integrity and confidentiality of such accesses.

#### **CHAPTER 4**

# HARDWARE SUPPORTED TECHNIQUES FOR ENSURING SOFTWARE INTEGRITY AND CONFIDENTIALITY

In this chapter we present the proposed hardware architecture supporting software integrity and confidentiality. We begin with a general overview of the proposed architecture followed by a more detailed discussion of the required hardware. Further design choices are then explored that reduce performance, energy, and memory overhead.

#### 4.1 Framework Overview

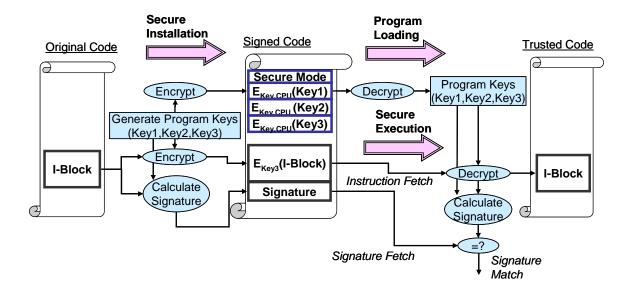

The framework for software integrity and confidentiality encompasses three stages [25]. The first stage is a secure installation procedure, in which binary executables are signed and optionally encrypted for a particular processor. The second stage is secure loading, in which the computer system prepares to run the secure program. The final stage is secure execution, where the program is run, such that its integrity and/or confidentiality is maintained.

The proposed architecture allows three levels of protection: unprotected, software integrity only mode (SIOM), and software integrity and confidentiality mode (SICM). In the SIOM mode only software integrity is guaranteed; all instructions are stored in binary plaintext that could be read by an adversary. The SICM mode ensures both software

integrity and confidentiality by further encrypting the instructions. Figure 4.1 shows an overview of the three stages of the proposed architecture when running in SICM mode.

Figure 4.1 Overview of Architecture for Trusted Instruction Execution

#### 4.1.1 Secure Installation

The process by which an unprotected program is installed on the system to take advantage of hardware support for software integrity and/or confidentiality is called secure installation. The secure installation procedure presented here is similar to that proposed by Kirovski *et al.* [35]. The CPU must perform secure installations in an atomic manner, and must not reveal any secret information during or after the installation.

Key generation is the first step in secure installation. SIOM mode requires two unique program keys, while SICM mode requires three. These keys, designated Key1, Key2, and Key3, are randomly generated by the CPU. They are then encrypted on-chip using the processor's internal secret key, Key.CPU. The encrypted keys are brought off-chip and stored in the header of the secure executable. Note that these keys should only leave the CPU in encrypted form; the plain-text keys must stay on the CPU.

The next step in the secure installation process is signature calculation.

Signatures must be calculated for each instruction block (I-block). Protected I-block size must be determined at this point. A natural protected I-block size is the line size of the lowest level instruction cache (I-cache) line. Smaller protected I-block sizes will yield a higher memory overhead, so a multiple of the I-cache line size may be chosen. This paper focuses on cases where the protected I-block size is either equal to or twice the size of the I-cache line size.

A protected I-block's signature is a cryptographic function of three factors: the block's starting virtual address (alternatively, its offset from the beginning of the program's code section), two of the program keys generated earlier, and the instruction words within the I-block. The use of unique program keys prevents the execution of any unauthorized code that may be inserted or injected after the installation process, and also protects against a splicing attack involving a valid I-block from another secure program. The use of the instruction words and the block address prevent spoofing and splicing from within the same program.

Encryption of program executables is required for SICM mode. Cryptographic schemes must balance two requirements. First, a high level of security is absolutely

necessary. Secondly, decryption should be fast, thus causing a low runtime performance overhead. The proposed architecture uses a variant of the one-time pad (OTP) encryption algorithm, which satisfies both requirements.

Variations in the order in which signing and encryption are performed give rise to three known approaches: encrypt&sign (ES), encrypt, then sign (EtS), and sign, then encrypt (StE) [36]. These encryption schemes are illustrated in Figure 4.2. Part (a) shows a plaintext 64 byte binary I-block (encoded for the ARM architecture and represented as hexadecimal) and its 16 byte signature laid out in memory. Part (b) shows the same I-block subjected to the ES scheme, which encrypts the plaintext and calculates its signature independently. Part (c) represents the EtS scheme, in which the I-block is first encrypted and the signature is calculated from the resulting ciphertext. Lastly, part (d) shows the StE scheme, in which the signature is calculated from the plaintext and both the I-block and signature are then encrypted. The relative strength of these implementations is still a subject for debate [36, 37]. Implementation of all three schemes would have similar hardware complexities, so we choose the StE scheme to facilitate analysis.

| 3000a80: | e3a02000 | 3000a80: | 579a754c | 3000a80: | 579a754c | 3000a80: | 579a754c |

|----------|----------|----------|----------|----------|----------|----------|----------|

| 3000a84: | e50b2030 | 3000a84: | c672ef35 | 3000a84: | c672ef35 | 3000a84: | c672ef35 |

| 3000a88: | e59f122c | 3000a88: | 2aabbff5 | 3000a88: | 2aabbff5 | 3000a88: | 2aabbff5 |

| 3000a8c: | e5812000 | 3000a8c: | 75fbfcea | 3000a8c: | 75fbfcea | 3000a8c: | 75fbfcea |

| 3000a90: | e50b2034 | 3000a90: | 9f733369 | 3000a90: | 9f733369 | 3000a90: | 9f733369 |

| 3000a94: | e1a06000 | 3000a94: | 2eefaeec | 3000a94: | 2eefaeec | 3000a94: | 2eefaeec |

| 3000a98: | e59f0220 | 3000a98: | 2d7473aa | 3000a98: | 2d7473aa | 3000a98: | 2d7473aa |

| 3000a9c: | eb002c5b | 3000a9c: | 640ce79b | 3000a9c: | 640ce79b | 3000a9c: | 640ce79b |

| 3000aa0: | e2505000 | 3000aa0: | 4148cddf | 3000aa0: | 4148cddf | 3000aa0: | 4148cddf |

| 3000aa4: | 0a000033 | 3000aa4: | 7bedbe21 | 3000aa4: | 7bedbe21 | 3000aa4: | 7bedbe21 |

| 3000aa8: | e1a00005 | 3000aa8: | 5afce7f8 | 3000aa8: | 5afce7f8 | 3000aa8: | 5afce7f8 |

| 3000aac: | e3a0102f | 3000aac: | e5486c46 | 3000aac: | e5486c46 | 3000aac: | e5486c46 |

| 3000ab0: | eb004ad2 | 3000ab0: | 066ce464 | 3000ab0: | 066ce464 | 3000ab0: | 066ce464 |

| 3000ab4: | e3500000 | 3000ab4: | 6caac2ef | 3000ab4: | 6caac2ef | 3000ab4: | 6caac2ef |

| 3000ab8: | 0a000004 | 3000ab8: | 0c4b1a49 | 3000ab8: | 0c4b1a49 | 3000ab8: | 0c4b1a49 |

| 3000abc: | e59f3200 | 3000abc: | 6a9e6cc8 | 3000abc: | 6a9e6cc8 | 3000abc: | 6a9e6cc8 |

| 3000ac0: | 8228f6a9 | 3000ac0: | 8228f6a9 | 3000ac0: | f6231db4 | 3000ac0: | b5f5be91 |

| 3000ac4: | c9cefbda | 3000ac4: | c9cefbda | 3000ac4: | 3495cc9c | 3000ac4: | cb72dd15 |

| 3000ac8: | 15b99534 | 3000ac8: | 15b99534 | 3000ac8: | 17350aac | 3000ac8: | 831ef1a2 |

| 3000acc: | 62e8bee6 | 3000acc: | 62e8bee6 | 3000acc: | 74d7ac7b | 3000acc: | 6b1f35a5 |

| (a)      |          | (b)      |          | (c)      |          | (d)      |          |

Figure 4.2 Signed Binary Instruction Block: (a) Signed plaintext, (b) ES, (c), EtS, (d) StE

## 4.1.2 Secure Loading

The secure loading process prepares a secure executable to run on the secure architecture. During this process, the encrypted program keys are read from the secure executable header. These are loaded into special-purpose registers on the CPU and decrypted using the processor's secret key (Key.CPU). As mentioned above, these keys should never leave the CPU as plain-text. They may only be accessed by dedicated on-chip hardware resources, such as the instruction block signature verification unit (IBSVU), which shall be discussed later. If a context switch occurs, these keys must be re-encrypted before leaving the processor to be stored in the process control block. When the context switches back to the secure program, they must be re-loaded into the processor and decrypted once again before secure execution may resume.

### 4.1.3 Secure Execution

The secure execution stage is when the secured program actually runs. The proposed architectural enhancements come into play whenever instructions are fetched from memory. Since the CPU chip is assumed to be secure, and instruction caches may be assumed to be read-only, instructions should be trusted once they are in the cache. Thus the architectural enhancements should operate in conjunction with the highest I-cache level, and it is convenient for the protected I-block size to be some multiple of the cache line size. If the system has no instruction cache, then the size of the fetch buffer may determine protected I-block size. Throughout the rest of the paper, we assume, without loss of generality, a system with separate Level 1 instruction and data caches, and no Level 2 caches. The general operation of the proposed mechanisms may be simply explained for the case where protected I-block size equals the cache line size. The case where the protected I-block size is double the cache line size will be explored below in Section 4.3.3.

Because the I-cache is a trusted resource, signature verification need only occur on a cache miss. Signatures are not cached, and are not available during execution, so they may reside outside the processors virtual address space. This requires additional logic to translate the original virtual instruction block address to the actual address of the instruction block in memory. Page padding must also be taken into account. Once the correct addresses are available, the protected I-block and its signature are fetched from memory and decrypted as needed. The signature is recalculated using the newly fetched I-block. If the calculated signature matches the fetched signature, then the I-block can be trusted. If the signatures do not match, then the I-block has been subjected to tampering.

The processor then traps to the operating system, which should take appropriate action to terminate the process. The simplest implementation would stall the processor until the I-block's signature has been verified. We call this a wait 'til verified (WtV) scheme. However, given certain additional hardware resources, a run-before-verification (RbV) scheme may be implemented. In that case, the processor may be allowed to continue execution once the I-block has been fetched and is in the cache. This concept will be elaborated on in Section 4.3.2.

### 4.1.4 Other Considerations

At this point, we must consider two special cases. The first involves dynamically linked libraries (DLLs), which contain binary executable code that is potentially shared among multiple programs. The simplest option would be to forbid the use of DLLs on the secured system. A slightly more complex option would be to introduce a bit in the page table and translation lookaside buffer (TLB) specifying whether or not that page contains protected code. Instruction pages within DLLs could then be marked as unprotected. Even more complex would be to further enhance the page table (and TLB) to mark the page as belonging to a DLL. DLL instructions would then be protected using additional processor-specific keys. Throughout the remainder of the thesis, we assume that DLLs are handled with one of these three methods.

The second case involves instructions that are generated at runtime, including just-in-time compilation and interpreted code. One option is to flag pages containing dynamically generated instructions as unprotected. Another option would be to have the program generating the instructions insert signatures as I-blocks are created. This

requires that the generating program be trusted, and thus the output of the program would also be trusted.

## 4.2 Basic Implementation

This section describes a simple, basic implementation of the instruction protection architecture. We first describe the cryptographic operations required for the simple CBC-MAC cipher, and then analyze the overhead incurred by this implementation. We finally discuss the hardware requirements for the architecture.

## 4.2.1 Implementation Details

The simplest implementation of the instruction protection architecture utilizes the cipher block chaining message authentication code (CBC-MAC) algorithm [29].

Signature generation is performed on-chip, using a dedicated hardware resource. Initial signature generation and possibly encryption is performed during the secure installation stage. During secure execution, the signatures must be recalculated after decryption (if necessary).

Signature generation may be illustrated by choosing an exemplary architecture. We assume a 32-bit architecture with 32 byte protected I-blocks. Each I-block will be appended with a 128-bit signature. The I-block is divided into two sub-blocks of equal size,  $I_{0:3}$  and  $I_{4:7}$ . Let A be the starting virtual address of the I-block, SP represent a secure padding function, and KEYI and KEY2 be the first two of the aforementioned unique program keys.

When using the CBC-MAC cipher, the signature *S* for the I-block is calculated according to Equation (4.1). The form of the signature function in this case is conducive to the sequential chaining provided by the CBC-MAC.

$$S = AES_{KEY2}[(I_{4:7}) \ xor \ AES_{KEY2}((I_{0:3}) \ xor \ AES_{KEY1}(SP(A)))]. \tag{4.1}$$

Equations (4.2) and (4.3) illustrate the encryption functions for the same sample system used to illustrate signature generation. Sub-blocks are defined as before. The encrypted versions of the sub-blocks,  $C_{0:3}$  and  $C_{4:7}$ , are calculated according to Equation (4.2). Note that KEY3 is another unique program key. This key is distinct from those used for signature generation since authentication and encryption should not use the same keys [38]. The encrypted signature eS is calculated according to Equation (4.3).

$$(C_{4i:4i+3}) = (I_{4i:4i+3}) xor AES_{KEY3} (SP(A(SB_i))), i = 0..1,$$

(4.2)

$$eS = S xor AES_{KEY3} (SP(A(eS))).$$

(4.3)

During secure installation, the I-block (possibly encrypted) is stored on disk or in memory, followed by its signature (also possibly encrypted). Protected I-blocks and their signatures should not cross page boundaries. Therefore, page padding may be required after the last signature in the page to ensure that the next I-block starts on the next page.

Signatures must be recalculated on instruction cache misses during secure execution. The signature cS is recalculated in the same manner in which the original signature S was calculated during secure installation. Recalling Equation (4.1), this calculation requires the encryption of secure padded virtual sub-block addresses. This

encryption should happen in parallel with the memory access, thus overlapping some of the cryptographic latency with memory access latency.

If the architecture is running in software integrity and confidentiality mode, then the I-block fetched from memory will contain ciphertext. Assuming the StE scheme, these instructions must be decrypted before signature recalculation and execution. The fetched signature must also be decrypted before comparison with the recalculated signature. Equations (4.4) and (4.5) illustrate the decryption of the fetched I-block and signature, respectively.  $A(SB_i)$  represents the virtual address of sub-block i. Note that if the encrypted addresses are available when the ciphertext arrives from memory, the decryption process only requires a simple XOR operation.

$$(I_{4i4i+3}) = (C_{4i4i+3}) xor AES_{KEY3} (SP(A(SB_i))), i = 0..1,$$

(4.4)

$$S = eS xor AES_{KEY3} (SP(A(eS))).$$

(4.5)

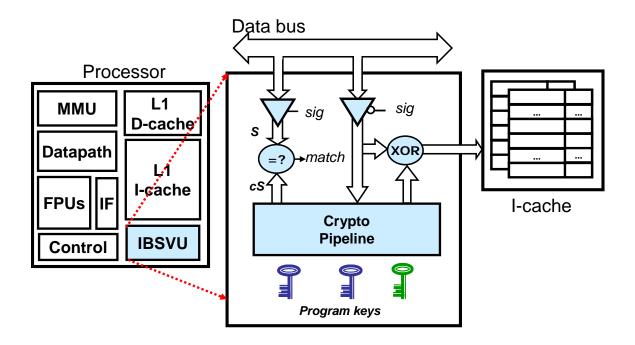

## 4.2.2 Performance Overhead

The implementation described thus far uses the CBC-MAC cipher with a WtV scheme. This CBC-MAC WtV implementation, although simple, is the most inefficient of the implementations to be discussed in this thesis. To illustrate the performance overhead incurred by this implementation, we continue with the sample system from Section 4.1. Throughout the remainder of this chapter, we assume that the processor is executing in SIOM mode. SICM mode requires two extra cryptographic operations, which for the example systems discussed below, can be completed before the encrypted sub-blocks are available from memory.

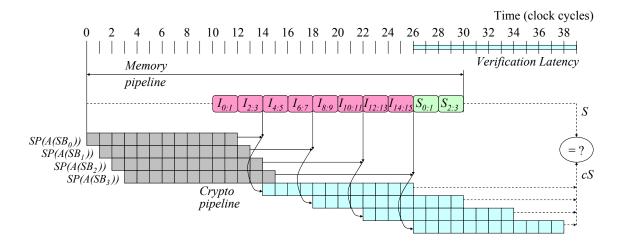

The procedures to be followed on an instruction cache miss are described in Figure 4.3. The verification latency introduced by this implementation is illustrated in Figure 4.4. In addition to the earlier assumptions, we assume bus width of 64 bits, and memory latency of 12 clock cycles for the first 64-bit chunk and 2 clock cycles for subsequent chunks. The darkly shaded blocks in the figure's cryptographic pipeline represent encrypting the sub-block addresses using Key1, which is necessary for signature recalculation. The lightly shaded blocks represent signature recalculation using Key2.

- 1. Probe I-cache for desired block. If found, return, otherwise continue.

- 2. Initiate fetch of instruction block and signature from memory.

- 3. Start cryptographic calculation using KEY1 on instruction block address (see Equation (4.1)).

- 4. If SICM, start cryptographic calculations using KEY3 on instruction sub-block and signature addresses; decrypt instruction block and signature when available (see Equations (4.4) and (4.5)).

- 5. Calculate signature for instruction block (see Equation (4.1))

- 6. Compare calculated signature to signature fetched from memory. If mismatch, trap to operating system.

Figure 4.3 I-Cache Miss Algorithm, CBC-MAC Implementation

Figure 4.4 Verification Latency, CBC-MAC WtV Implementation

Measured from the cycle at which the last instruction word is available (at which point the processor would normally resume execution), this implementation has a verification latency of 21 clock cycles, including a clock cycle for signature comparison.

## 4.2.3 Hardware Requirements

Each of the three stages of this architecture requires at least some hardware support on the CPU. Common to all three stages, however, is the need for a cryptographic cipher unit that implements the Advanced Encryption Standard (AES). There are multiple existing hardware designs for such a hardware unit, two of which are convenient for use with the proposed architecture. The first of these two, the CBC-MAC, has already been mentioned. The other shall be discussed in Section 4.3.1.

In addition to the cryptographic unit, the secure installation stage requires a unique processor key and the ability to generate random program keys. Manufacturers have long had the ability to embed unique read-only data on individual chips. A similar process may be used to embed the CPU's secret key. This key must only be used

internally; it should never leave the chip. The processor must also be able to generate program keys at random. A variety of methods exist for random number generation, including thermal noise within the processor [39] and physical unclonable functions (PUFs) [24]. The program keys must never leave the processor in plain-text form. During secure installation, these keys are encrypted using the crypto unit; the encrypted version of the keys may leave the CPU.

The processor must have a mechanism to enter a secure installation mode. One option is to augment the instruction set, providing an instruction to initiate secure installation. This instruction would trigger a state machine to handle secure installation procedures such as key generation, signature generation, and encryption. Another option is to trigger secure installation with a separate piece of hardware, such as a smart card reader. This piece of hardware would then serve as a key, unlocking the secure installation capabilities.

The secure loading stage requires a state machine to load the encrypted program keys from a specified location in memory and decrypt them. The decrypted keys must be stored in special purpose registers in the CPU, and must never leave the chip. As stated earlier, context switch handling must also be modified to encrypt the keys and write them out to the process control block.

The secure execution stage requires extensive hardware support in the form of the instruction block signature verification unit (IBSVU). The IBSVU, illustrated in Figure 4.5, contains the cryptographic unit, which is also used by the secure installation and loading stages. The IBSVU also contains the address translation logic and a buffer to store a signature waiting to be compared. It may also contain other hardware resources as

described in Section 4.3. The IBSVU must work very closely with the cache controller, and could in some ways be considered an extension of the cache controller.

With the exception of external key hardware to trigger secure installation mode, all of this hardware may be implemented with relatively low complexity. The complexity added to the processor is qualitatively evaluated in Section 7.1.

Figure 4.5 Instruction Block Signature Verification Unit

# 4.3 Reducing Overhead

This section discusses schemes for reducing the relatively high overhead of the implementation described above. We start by introducing the parallelizable MAC (PMAC) algorithm, which reduces cryptographic latency. We then discuss the

implementation of an RbV scheme that almost completely hides verification latency.

Finally we address memory overhead by protecting multiple I-blocks with one signature.

### 4.3.1 PMAC

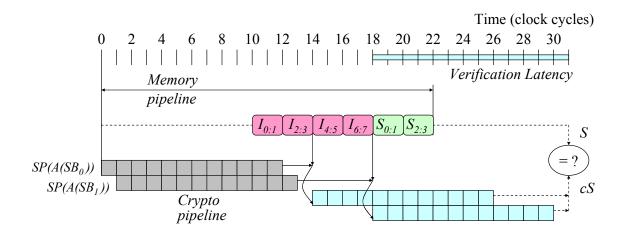

Performance overhead can be greatly reduced by using a parallelizable MAC cipher. The PMAC algorithm was developed by Black and Rogaway [40], who show that it approximates a random permutation. As its name implies, the PMAC can compute multiple cryptographic functions in parallel, allowing for an efficient pipeline.

The PMAC cipher allows signatures for each sub-block to be calculated in parallel. In this case, we can calculate a signature  $Sig(SB_i)$  for each sub-block i according to Equation (4.6). The signature S of the whole protected I-block is an exclusive or (XOR) function of the signatures of the sub-blocks, as expressed in Equation (4.7).

$$Sig(SB_i) = AES_{KEY2}[(I_{4i:4i+3})xor AES_{KEY1}(SP(A(SB_i)))], i = 0..1,$$

(4.6)

$$S = Sig(SB_0) xor Sig(SB_1). (4.7)$$

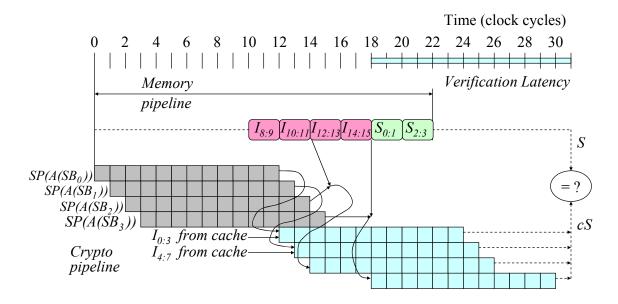

The procedures to be followed for a PMAC implementation on an I-cache miss are outlined in Figure 4.6. Figure 4.7 illustrates the verification latency for the PMAC WtV implementation for the sample machine discussed above. Using PMAC, verification latency is reduced to 13 cycles, including a clock cycle for signature comparison. This is an improvement over the CBC-MAC, but still introduces a significant performance overhead.

- 1. Probe I-cache for desired block. If found, return, otherwise continue.

- 2. Initiate fetch of instruction block and signature from memory.

- 3. Start cryptographic calculations using KEY1 on instruction sub-block addresses (see Equation (4.6)).

- 4. If SICM, start cryptographic calculations using KEY3 on instruction sub-block and signature addresses; decrypt instruction blocks and signature once available (see Equations (4.4) and (4.5)).

- 4. Calculate signature for instruction block (see Equations (4.6) and (4.7))

- 5. Compare calculated signature to signature fetched from memory. If mismatch, trap to operating system.

Figure 4.6 I-Cache Miss Algorithm, PMAC Implementation

Figure 4.7 Verification Latency, PMAC WtV Implementation

## 4.3.2 Run-Before-Verification

Ideally, the verification latency should be completely hidden, thus introducing no performance overhead. This would require that the processor resume executing instructions as soon as the whole instruction cache line is available. Such a scheme is called Run-before-Verification (RbV). The instruction block, however, may have been subject to tampering, which will not be evident until signature verification is complete.

The solution to this quandary is to allow untrusted instructions to execute, but not commit until their signatures have been verified. This prevents tampered instructions from writing to CPU registers or to memory. For out-of-order processors, RbV support requires a simple modification to the reorder buffer, adding a verified flag that the IBSVU will update. Instructions may not be retired until that verified flag is set. The memory access unit must also be modified to prevent an unverified instruction from writing data to memory. In-order processors require an additional resource: the Instruction Verification Buffer.

The structure of the IVB is shown in Figure 4.8. The IVB's depth (number of instructions whose information it can hold) is a design parameter, represented by n in the figure. After instructions are fetched on an I-cache miss, their information is placed in the IVB. When the processor has completed execution of the instruction, it checks the IVB to see if that instruction has been verified. If it has not been verified, the instruction may not be retired. Once the instruction is retired, it is removed from the IVB. In the unlikely event that newly fetched instructions will not fit in the IVB, the processor must stall until enough instructions have been removed so that the new instructions can be inserted.

|       | IType | Destination | Value | Ready<br>Flag | Verified<br>Flag |

|-------|-------|-------------|-------|---------------|------------------|

| 0     |       |             |       |               |                  |

| 1     |       |             |       |               |                  |

|       |       |             |       |               |                  |

|       |       |             |       |               |                  |

| n - 1 |       |             |       |               |                  |

Figure 4.8 Instruction Verification Buffer

Shi and Lee point out that RbV schemes are vulnerable to side-channel attacks if a malicious memory access or jump instruction has been injected into the I-block [41]. Such instructions may reveal confidential data by using it as the target address. If this is a concern, then the architecture may be slightly modified to stall instructions that would result in any memory access until they have been verified.

## 4.3.3 Reducing Memory Overhead

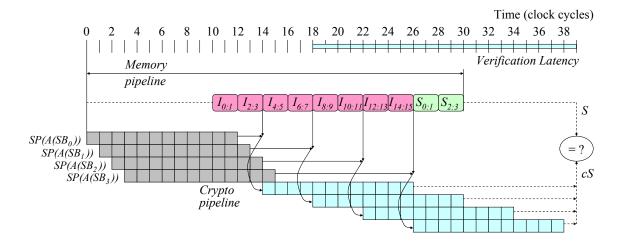

The proposed architecture could introduce a hefty memory overhead. In the examples discussed above, for every 32 bytes of instructions, a 16 byte signature is required. This overhead could be prohibitive on embedded systems with tight memory constraints. The solution is to make the protected I-block size a multiple of the I-cache line size.

In this section we consider a modification to the PMAC RbV implementation implemented above. The protected I-blocks are 64 bytes, twice the size of the I-cache

line. This introduces two additional sub-blocks,  $I_{8:11}$  and  $I_{12:15}$ . The equations presented above need only be extended to take these additional sub-blocks into account. The signatures of the two additional sub-blocks are calculated independently, and the signature for the whole I-block is calculated by XORing the signatures of all four sub-blocks.

Enlarging the protected I-block introduces new design choices. Since a protected I-block now covers two cache lines, a policy is required to handle the currently unused cache line on an I-cache miss. Additionally, the amount of data transferred from memory influences both performance and power overhead. The most naïve implementation would always fetch the entire I-block on an I-cache miss, and discard the portion of the block that is not currently needed. A more efficient implementation would take advantage of the I-cache to reduce memory accesses, and thus power and performance overhead.

The basic procedure to be followed on an I-cache miss with double size protected blocks is outlined in Figure 4.9. The required actions can be broken down further into four cases based on which part of the protected I-block is currently needed by the processor and whether or not the other half of the protected I-block currently resides in the cache. These cases are presented below. For convenience, we call the first cache line in a protected I-block Block A, and the second Block B. The memory layout of blocks A and B with their signature is illustrated in Figure 4.10, along with a summary of the four cases.

- 1. Probe I-cache for desired block. If found, return, otherwise continue.

- 2. Initiate fetch of instruction block and signature from memory.

- 3. Start cryptographic calculations using KEY1 on instruction sub-block addresses (see Equation (4.6)).

- 4. If SICM, start cryptographic calculations using KEY3 on instruction sub-block and signature addresses; decrypt instruction blocks and signature once available (see Equations (4.4) and (4.5)).

- 5. Calculate signatures for each instruction block (see Equations (4.6) and (4.7)).

- 6. Calculate total signature by XORing instruction block signatures.

- 7. Compare calculated signature to signature fetched from memory. If mismatch, trap to operating system.

Figure 4.9 I-Cache Miss Algorithm, PMAC Implementation, Expanded Protected I-Block

| Sub-block 0 | Disak   | Miss On | Condition            | Case # |

|-------------|---------|---------|----------------------|--------|

| Sub-block 1 | Block A | Block A | Block B not in cache | 1      |

| Sub-block 2 | Dlook D | DIOCK A | Block B in cache     | 2      |

| Sub-block 3 | Block B | D11- D  | Block A not in cache | 3      |

| Signature   |         | Block B | Block A in cache     | 4      |

Figure 4.10 Memory Layout and Cache Miss Cases

#### **4.3.3.1** Miss on Block A